Импульсный анализатор колебаний напряжения

Иллюстрации

Показать всеРеферат

Союз Севетских

Социапистических

Республик (a)1000927

К АВТОРСКОМУ СВНДЕТЕЛЬСТВУ (61) Дополнительное к авт, саид-ву . (22) Заявлено 13. 04. 81 .(21) 3313115/18-21 с присоединением заявки М(23) Приоритет

Опубликовано28.02.83. Бюллетень №8

Дата опубликования описания 28. 02. 83 (51)Ч. И,д, G 01 и 19/04

Гесударетвеллме камктет (53) УДК 621,317. .ggj (088.8) пв делам изобретении и аткрмтий (72) Авторы изобретения

В,Ф. Ермаков и В. И. Черепов

Новочеркасский ордена Трудового Красного политехнический институт им. Серго Орджони (71) Заявитель (54) ИМПУЛЬСНЫЙ АНАЛИЗАТОР КОЛЕБАНИЙ НАПРЯЖЕНИЯ

Изобретение относится к измерительной и вычислительной технике и может быть использовано при аппаратурном контроле показателей качества электрической энергии.

Известен статистический анализатор колебаний напряжения, содержащий клю чи, дифференцирующее звено, блок формирования модуля, пороговый элемент, элемент НЕ, разделительные диоды, на- о копительные конденсаторы, аналоговый инвертор„ триггер Шмитта, симметрииные триггеры, элемент временной задержки, элементы совпадения, счетчики импульсов fl ).

К недостатком известного устройства относятся низкие точнссть измерения и помехоустойчивость. Последняя обусловлена наличием дифференци- рующего звена. zo

Наиболее близким к предлагаемому по технической сущности является анализатор колебаний напряжения, со держащий дифференцирующий элемент, 2 блок формирования модуля, управляющий пороговый блок, измерительный пороговый блок с различными уровнями срабатывания, элементы И, регистрирующие счетчики, элемент ИЛИ-И, распредел 1тель импульсов, элемент .задерж ки триггер нулевого канала P2).

Недостаток данного устройства заключается в низкой помехоустойчивости. обусловленной наличием дифференцирования.

Цель изобретения - повышение помехоустойчивости анализатора.

Поставленная цель достигается тем что в импульсный анализатор колебаний напряжения, содержащий блок по- . роговых элементов, первый выход ко" торого соединен с входом первого элемента И, а вход подключен к входной клемме знализатора, первый управляющий пороговый блок, блок памяти элемент задержки, выход которого сое» динен с входом установки нуля блока памяти, введены блок управления, вто3 10009 рой управляющий пороговый блок, элемент И, элемент ИЛИ, выход которого соединен с блоками памяти, а входмс выходами элементов И, первый и второй стробируемые интегратор%, выходы которых через соответствующие управляющие пороговые блоки соединены с входами соответствующих элементов И . и соответствующими входами блока управления, два другие входа которого 16 соединены с соответствующими выходами блока пороговых элементов, а выходс элементом задержки и блоком памяти, источник опорного напряжения, соединенный с входами стробируемых ин- 15 теграторов, другие входы которых сое. динены с соответствующими выходами блока пороговых элементов, второй выход которого соединен с входом второго элемента И.

Блок управления выполнен в виде блока, содержащего. триггер управления, два элемента И, один из входов которых является динамическим, два формирователя и элемент ИЛИ, причем первый и второй входы блока управления соединены соответственно с S- u

R-входами триггера управления, прямой выход которого соединен с входом первого формирователя и со статическим входом первого элемента И, динамический вход которого соединен с третьим входом блока управления, а инверсный выход триггера соединен с выходом второго формирователя и со

35 статическим входом второго элемента

И, динамический вход которого соединен с четвертым входом блока управления, а выходы формирователей и элементов И соединены с входами элемента ИЛИ, выход которого соединен с выходом блока управления.

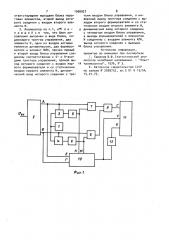

На фиг. 1 представлена структурная блок-схема предлагаемого устройства; на фиг. 2 — временные диаграммы напряжений на элементах схемы устройства; на фиг. 3 — блок пороговых элементов; на фиг. 4 — схема стробируемого интегратора; на фиг. 5 - функциональная схема блока памяти; на

5Î фиг. б - схема блока управления.

Анализатор содержит источник 1 опорного напряжения, блок 2 пороговых элементов, стробируемые интеграторы 3 и 4, управляющие пороговые устройства 5 и б, элементы И 7 и 8, элемент ИЛИ 9, блок 10 управления, блок 11 памяти и элемент 12 задержки.

27 4

Блок 2 пороговых элементов (фиг.3) включает пороговые элементы 13 и элементы ИЛИ 14 и 15 с динамическими входами.

Каждый из стробируемых интеграторов 3 и 4 (фиг.4) содержит входное сопротивление 16, операционный усилитель 17, конденсатор 18 и ключ 19 управления.

Блок 11 памяти (фиг.5 ) состоит из распределителя 20 импульсов и информационных счетчиков 21 импульсов.

Блок 10 управления (фиг.б ) содержит триггеры 22 управления, элементы И 23 и 24, один из входов которых является динамическим, а другой - ста тическим, формирователи 25 и 26, элемент ИЛИ 27.

Анализатор работает следующим образом.

Исследуемое напряжение U „ поступает на вход блока 2 пороговых эле.ментов. Уровни срабатывания пороговых элементов 13 (фиг.3) расставлены по равномерному закону с шагом квантования Д0. При пересечении входным напряжением уровней срабатывания пороговых элементов.13 (фиг.3) последние срабатывают (отпускают ) и на выходе А (В) элемента ИЛИ 14(15) формируются короткие импульсы. Количество этих импульсов равно числу сработавших (отпустивших) пороговых элементов 13, а длительность между соседними импульсами равна времени Дй.

Производная исследуемого напряжения определяется косвенным путем по интервалу времени gt, которое на каждом шаге квантования сравнивается с

5U эталонным временем Дь=> (где U p — крикр тическая скорость изменения напряжения, равная 13/с, Эталонному времени дС соответствует скорость изменения напряжения в li/с. Превышение значения критической скорости является признаком колебания напряжения. Если Дt) ДТ, то скорость изменения мень ше или равна li/с, если Д1 (сЪ,, то скорость изменения напряжения больше l i/с.

Контроль за изменением скорости

О „производится отдельно для кривой нарастающего и спадающего напряжений. Эталонное время QV при анализе нарастающего (спадающего ) напряже000с 27 4

5 1 ния равно времени заряда емкости 18 стробируемого интегратора 3(4 ) от нулевого уровня до напряжения срабатывания порогового элемента 5(6 ).

Рассмотрим процесс анализа колебаний напряжения на кривой нараста-. ющего напряжения (фиг.2).

В исходном положении конденсатор

18 интегратора 3 заряжен до напряжения источника 1 питания, пороговое устройство 5 удерживается в сработавшем состоянии, на его выходе присутствует логический нуль, элемент

И 7 закрыт. При появлении импульса на выходе А блока 2 ключ 19 управления открывается и конденсатор 18 интегратора 3 разряжается. Пороговое устройство 5 при этом отпускает элемент И 7 открывается. По окончании этого импульса происходит заряд конденсатора 18 интегратора 3, На интервале времени t - t (5t (4Ej поф роговое устройство 5 не срабатывает, так как напряжение на выходе стробируемого интегратора 3 не достигает за время и с уровня срабатывания. Импульсы с выхода А блока 2 через открытый элемент И 7 и элемент ИЛИ g поступают на вход блока 11 памяти, Всего на интервале времени t - й,1в

1 блок 11 памяти поступает три импульса. На третьем выходе распределителя 20 появляется логическая единица . и после поступления управляющего импульса на вход U блока 11 памяти счетчиком 21 третьего канала устрой: ства засчитывается единица. Через время, определяемое задержкой элемента 12, импульс управления поступит на вход R блока 11 памяти,. устанавливая распределитель 20 импульсов в нулевое состояние. Аналогично выделение колебаний напряжения происходит для кривой спадающего напряжения. На интервале времени t -t

6 1О в блок памяти поступает четыре импульса, на интервале й.1,1- t<>- два и т.д. Управление работой блока 11 памяти осуществляется блоком 10 управления. При поступлении импульсов на вход Е блока 10 управления триг.гер 22 управления устанавливается в единичное состояние, а импульсы, поступающие на вход Г, переводят его в нулевое состояние. В тех случаях, когда напряжение U нарастает (спаЬХ дает ) триггер 22 управления находится в единичном (нулевом)состоянии, подготавливая элемент И 23(24) к работе. При анализе нарастающей (спадающей ) кривой, когда а-t )дiс, по заднему фронту срабатывания порогового устройства 5(6) на выходе weмента И 23 (24 ) формируется импульс управления, который, проходя через элемент ИЛИ 27, появляется на выходе блока 10 управления (фиг;2, мо" менты t<, t<, t<>, t<<), В тех случаях, когда с изменением знака производной триггер управления меняет свое состояние, на выходе формирователя 25(26)появляется импульс управления (фиг.2, 02, моменты времени .

С6, )-.

Предлагаемая схема анализатора колебаний напряжения обладает высокой помехоустойчивостью по сравнению с известными, что позволяет получать достоверную информацию о качестве напряжения в электрических сетях., Схема анализатора проста и легко реализуется на интегральных микросхемах 155 серии ЛА-2, ЛА-3, ИЕ-2, ИД-l, ИД-3, 153 серии УД-2, УД-6. формула изобретения

Импульсный анализатор колебаний напряжения, содержащий блок по" роговых элементов, первый выход ко.торого соединен с входом первого эле.мента И, а вход подключен к входной клемме анализатора, первый управляющий пороговый блок, блок памяти, элемент задержки, выход которого соединен с входом установки нуля блока памяти, о т л и ч а ю щ и йс я тем, что, с целью повышения помехоустойчивости, в него введены блок управления, второй управляющий пороговый блок„ элемент И, элемент

ИЛИ, выход которого соединен с бло" ком памяти, а входы — с выходами элементов И, первый и второй стробируемые интеграторы, выходы которых через соответствующие управляющие блоки соединены с входами соответствующих элементов И и соответствующими входами блока управления, два другие входа которого соединены с соответ-. ствующими выходами блока пороговых элементов, а выход — с элементом за" держки и блоком памяти, источник опорного напряжения, соединенный с входами стробируемых интеграторов, другие входы которых соединены. с со7 10009 ответствующими выходами блока пороговых элементов, второй выход которого соединен с входом второго элемента И.

2. Анализатор по и. 1, овт л ич а ю шийся тем, что блок управления выполнен в виде блока, содержащего триггер управления, два элемента И, один из входов которых является динамическим, два формиро- IO вателя и элемент ИЛИ, причем первый и второй входы блока управления соединены соответственно с S- u R-аходами триггера управления, прямой выход которого соединен с входом пер- 1 вого формирователя и со статическим входом первого элемента И, динамический вход которого соединен с тре27 8 тьим входом блока управления, а инверсный выход триггера соединен с выходом второго формирователя и со статическим входом второго элемента И, динамический вход которого соединен с четвертым входом блока управления, а выходы формирователей и элементов

И соединены с входами элемента ИЛИ, выход -которого соединен с выходом блока управления.

Источники информации, принятые во внимание при экспертизе . 1. Ермаков В.ф. Статистический анализатор колебаний напряжения. - "Электромеханика", 1976, 1 3.

2. Авторское свидетельство СССР по заявке N 2099732; кл, G 01 R 19/04, 15.01.75. фиг, 1

1000927 ВХ 2А 2Â

1000927

1100927

Составитель С. Морозов

Редактор А. ЛежнинаТехред Ж.КастелевичКорректор И.Ватрушкина

Заказ 1372/47 Тираж 708 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, N-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4