Программируемый контроллер

Иллюстрации

Показать всеРеферат

О П И С А Н И Е ii iooio

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Донолиительное к авт. свнд-ву (22)Заявлено 13.10.81 (21) 3345378/18-24 с присоединением заявки ¹ (23) Приоритет

Опубл и кова но 2 8. 0 2 . 83, Бюллетен ь №

Дата опубликования описания 28.02 . 83 (51)M. Кл.

G 05 В 19/18

ГвсуАарстинньй квинтет

no aessw нзвбретекнй н етхрытий (53) УД К621. 50 3 ... 35 (088,8) Л. А.Элькинд, М, Б. Баранов, В. П, )ряков иЯ. С.Иванов

:, Ф: . . i

4 а, 3т . 1

Ленинградское специальное конструкторскЪе 4@ро тяжелых и уни кал ьных ст ан ков (72) Авторы изобретения (7I) Заявитель (54) ПРОГРАММИРУЕМЫЙ КОНТРОЛЛЕР

Изобретение относится к управляющим системам с программным управлени- ем и может быть использовано для логического управления станками и автоматическими линиями.

Известен программируемый контроллер, содержащий центральный процессор, программируемый блок памяти, устройство, сканирующее содержимое ° памяти, и функциональные блоки входных сигналов, выходных сигналов, таймеров, счетчиков неразрушаемой памяти, оперативной памяти. Сканирующее устройство обеспечивает последователь ный вывод кодов, содержащихся в блоке памяти и выдачу их в процессор и на функциональные блоки )if .

Недостатком его является отсутствие защиты входных цепей контроллера от "дребезга контактов", помех и ïðîпадания напряжения питания входных цепей, т.е. низкая достоверность ввода информации в процессор. а

Наиболее близким техническим решением к предлагаемому является устройство программного управления, которое содержит генератор, счетчик, за. поминающее устройство, процессор, селекторы, дешифраторы, линейки вентилей И входных сигналов, блок формирования выходных сигналов с элементами И.

Генератор обеспечивает счетчик так. товыми импульсами; Счетчик формирует на выходах коды, по которым последовательно "из запоминающего устройства считываются коды команд, которые по ступают на схему, состоящую из селекторов и дешифраторов. Эта схема обеспечивает открывание линеек вентилей

И входных сигналов по командам иэ запоминающего устройства. Сигнал с выхо20 да вентилей поступает в процессор. В зависимости от сигнала и команды, поступающей в процессор, последний фор-. мирует сигналы управления для блока!

00 t0

- n 1! 1, 1ходных o! I над!nн с эле:1 л,1 !

L 1:::дс с-:! ком изн".с ..- о "-. ройстн;1 .-э;>ммно-о упранлен. я является отi::i ние защиты от 1дрсбез а контак5 т;а . помех и пропад",íìÿ на.-. .:яж ния, 1 а, вход ых цепей., T,е. !Ilлзкая помехоу: ойчиность устройства,. Для

;:странения этого недостатка на всех

Eçõoänõ необходимо устанавливать эле- IIQ

;ленты защи Tbl, что в целом увеличивает коли:естно электронного оборудования пропорционал ь но коли че ст ну входон ус 1oйства !el1!; изобретен я — повышение пои-.хоус.-о,;-1иности контроллера

Поставленная цель достигается . е;,. :-о и программируемый контроллер, содержащий элементы согласования, -..neдиненные с входами контроллера, ослед >в"-,тельно соединенные генератор импульсов., программный счетчик и первое s,I;Ioминающее устройство, управляюци= выходы которого подключены к ны чи сл. - BFI ь ному блоку, а адресные

25 выходы — к адресным входам блока формирователя выходных. си гналон, подключонно" î информационным входом к выходу Rbl 1и сли тел ь НО го оло ка а Выходом выходу контроллера введены первый

1 зв и p, врой дешифраторы, формирователь ;-гнул ь =он, адресный = чет -,и к коммутаг..-,;; . мул -.т!лоле ксор, второе заг1оми наюйее устной ст нО, Ое ги OTG Галляти и

1ажс1ри тари 1й элемент, и нфор мационные

4 cl

-1ходы мультиплексора соединень1 с выходами элементов согласования, а адрес,!..!е входы — с адресными ьходами втooo!о запоминающего устройства и выходами коммуTaiopa, первые инфор;-.ационные входы которого соединены с выходами всех разрлдон 1дресного счетчика,. - вгорые информационные входы - с адресными выходами первого запоминающего устройстна и с входами

45 первого дешифратора, выходами подключенного через формирователь импуль. сов к управляющему входу коммутатора, счетный вход адресного счетчика соединен с выходом одного из разрядов про.граммного счетчи ка и с первым входом второго дешифратора, второй вход которого соединен с выходом одногo из разрлдов адресного счетчика, первый выход — с управляющим входом второго запоминающего устройства., а второй выход " с управллющим входом регистра памяти„ подключенного информационными входами к первым вь.ходам втсро12 гo зэпомин;1ющвго устройсiEIà, второй выход которого соединен с информационным входом вычислительного блока, пер. вый лнформационный вход — с выходом мультиплексора и одним из входов мажоритарного элемента, второй информационный вход — с одним из выходов регистра памяти, а третий информационный вход - с выходом мажоритарного элемента, подключенного вторыми входами к выходам регистра памяти.

Та кой программируемый контроллер обладает повышенной помехоустойчивостью, так как заключение о значении входного сигнала делается на основании трех выборок сигнала, разнесенных во времени.

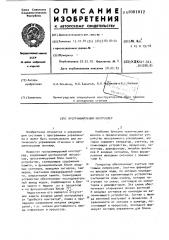

На чертеже приведена структурная

oõeëû контроллера.

Программируемый контроллер содержит генератор 1 импульсов, программный счетчик 2, первое запоми на1сщее устройство (ЗУ) 3, состоящее из многоразрядных я чеек ч памяти и схемы 5 выборки многоразрядных кодов, вычислительный блок 6, блок 7 формирования выходных сигналов, первый дешифОатор 8, формиронатель 9 импульсов, =.одержащий элемент 10 задержки и элемент И 11, второй дешифратор 12, комl óòàòoð 13, адресный счетчик 11, элементы 1 согласования, мультиплексор 16, второе запоминающее ус рой.

:т но 1 ЗУ) 17 регистр 18 памяти, мажоритарный элемент 19:

Программируемь1й контроллер работает следующим образом.

Генератор 1 формирует импульсы, которые с его выхода поступают на вход счетчика 2, На выходах счетчика

2 формируетсл код, который подается на управляющие входы схемы 5, обеспечивающей выдачу содержимого из яче" ек 4, код адреса которой установлен на входах схемы 5.

Каждый следующий импульс устанавливает на выходах счетчика 2 новый адрес и так до тех пор, пока будет считано содержимое всех ячеек. Затем ци кл считы вания повторяется . На выхо" дах ЗУ 3 последовательно формируютя коды команд, которые состоят из двух частей: кода адреса и кода операции. Код операции поступает на управляющие входы блока 6, код адреса — на адресные входы блока 7, дешифратора 8 и коммутатора 13, блок

6 реализует логическую функцию над операндом поступающим на его вход

10010

Формула изобретения

5 с выхода второго ЗУ 17, и операндом, хранящимся в памяти вычислительного блока 6, в соответствии с кодом операции на его управляющих входах.

Р эультат операции подается с выхода блока 6 в блок 7, который по.команде из ЗУ 3 принимает операнд и формирует выходной сигнал, соответствующий значению операнда на том выходе, адрес которого поступает в ЗУ 3. !о

Иультиплексор 16 обеспечивает выбор входа, номер которого соответствует коду адреса, задаваемого адресным счетчиком 14, и подключение второго двоичного сигнала к выходу мультиплексора 16. Элементы 15, например оптроны, обеспечивают развязку входных цепей контроллера и преобразование сигналов с параметрами входных цепей в сигналы с параметрами we- 26 ментной базы контроллера. ЗУ I7 содержит три одинаковые строки ячеек памяти. Количество ячеек памяти в каждой строке равно количеству входных цепей (2"), где n - количество 2ю разрядов в коде адреса. Иомера трех я чее к памяти, в которыя прои сходит одновременная запись или считывание информации, определяются кодом на адресных входах второго ЗУ 17. зв

Импульс записи, поступающий с выхода 1 дешифратора 12 производит запись информации в ячейки второго

ЗУ 17: в ячейку, подключенную к входу l - с выхода мультиплексора 16, в ячейку, подключенную к входу II - с выхода первого разряда регистра 18 памяти, в ячейку, подключенную к вхо:ду !!! - с выхода элемента 19. Иежду импульсами записи ЗУ 17 работает в режиме чтения, и импульсами с выхода дешифратора 12 происходит запись в два разряда регистра 18 содержимого двух ячеек ЗУ 17.

После окончания импульса записи в регистр 18 на входах элемента 19 при-. сутствует информация о сигнале во входной цепи, полученнвя в три момента времени О, Т, 2Т, отстоящей друг

:от друга на время Т =2" Т, где Т - период следования импульсов на выходах дешифратора 12. Элемент 19 передает иа выход то значение сигнала, которое присутствует на боль-! шинстве входов (двух или трех). В слуИ чае присутствия во входнои цепи помехи в течение времени меньшего Т только одно из трех значений сигнала на входе элемента 19 неверно и на

12 6 вход ЗУ 17 передается правильный сигнал о состояНии входной цепи, т.е. происходит селе кти вное подавлени е помехи. При смене кодов на адресных входах мультиплексора !6 и ЗУ 17 игналы о состоянии всех входных цепей после обработки в элементе 19 пеоиодически записываются в третью строчку ЗУ 17. Передача информации из ЗУ

17 в блок 6 осуществляется под управлением специальной команды из ЗУ 3.

Эта команда состоит из двух полей разрядов, присутствующих на адресных выходах первого ЗУ 3: первое поле - разряды с n+1 по К-й, второе поле - разряды с 1 по п-й.

Код первого поля дешифрируется первым дешифратором 8 и обеспечивает выдачу через коммутатор 13 кода адреса входа контроллера, заданного вторым полем, на адресные входы мультиплексора 16 и ЗУ 17, Формирователь 9 обеспечивает формирование импульсов по переднему фронту выходных импульсов дешифратора 8, что необходимо для синхронизации момента обращения к второму ЗУ 17 с интервалом считывания указанного У.

Предлагаемый программируемый контроллер обладает повышенной помехоустойчивостью, что позволяет исключить экономические потери, связанные с выходом иэ строя управляемых объектов или браком обрабатываемых деталей.

Программируемый контроллер, содер-, жащий элементы согласования, соединенные с входами контроллера, последовательно соединенные генератор имйульсов, программный счетчик и первое запоминающее устройство, управляющие выходы которого подключены к вычислительному блоку, а адресные выходы - к адресным входам блока формирования выходных сигналов, подключенного инФормационным входом к выходу вычислительного блока, а выходом - к выходу контроллера, отличающийся тем, что, с целью повышения помехоустойчивости контроллера, в него введены первый и второй дешифраторы, фор. мирователь импульсов, адресный счетчик, коммутатор, мультиплексор, второе запоминающее устройство, регистр памяти и мажоритарный элемент, инФормационные входы мультиплексора сое 7 10010 динены с выходами элементов согласования, а адресные входы - с адресными входами второго запоминающего устрой ст ва и с выходами коммутатора, первые информационные входы которого сое- g динены с выходами всех разрядов адресного счетчика, а вторые информационные входы - с адресными выходами первого запоминающего устрой ст ва и с входами пер во го дешифратор а, выходом под 10 ключенного через формирователь импульсов к управляющему входу коммутатора, счетный вход адресного счетчика соединен с выходом одного из разрядов программного счетчика и с первым входом второго дешифратора, второй вход которого соединен с выходом одного из разрядов адресного счетчика, первый выход - с управляющим входом второго запоминающего устройства, а второй вы-2I) 12 8 ход - с управляющим входом регистра памяти, подключенного информационными входами к первым выходам второго запоминающе ro устрой ст ва, второй выход которого соединен с информационным входом мультиплексора и с одним из входов мажоритарного элемента, второй информационный вход - с одним из выходов регистра памяти, а третий инI формационный вход — с выходом мажоритарного элемента, подключенного вторы. ми входами к выходам регистра памяти, Источники информации, принятые во внимание при экспертизе

1, Срибнер Л. А. Программируемые контроллеры, их особенности и тенденции развития — Управляющие системы и машины, 1Я78, М 2.

2. Патент Великобритании 71507537, кл„ 0 3 М опублик. 1978 (прототип), 1001012 ь ф

4 Фэ

Ь Ю

Тираж 872

Подписное

ВНИИПИ Заказ 1390/52 филиал ППП "Патент", r, Ужгород, ул. Проектная, 4