Цифровой генератор гармонических функций

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социапистичеси их республик (11)1001069 (6! ) Дополнительное к авт. свид-ву (22) Заявлено 25:09.81 (21) 33382417 18-24 (Sl)N. Кл. с присоединением заявки М

8 06F 1/02

Гвс1дарстаакый каиктвт

СССР ю Евам кзабретеккй и втхрытий (23) Приоритет

Опубликовано 28.02."3 ° бюллетень М 8

Дата опубликования описан 28 .02 83 (53уУД 681.3. (088.87

:. I

В.Я. Краковский и В.ф. Ковал ".":

/ :/ !

Ордена Ленина институт кибернетики АН 7крЪииаыцй ССР

"э., ( (72) Авторы изобретения (7l) Заявитель (54) ЦИФРОВОЙ ГЕНЕРАТОР ГАРМОНИЧЕСКИХ

ФУНКЦИИ!

Изобретение относится к автоматике и вычислительной технике и может быть использовано в анализаторах спектра, функциональных преобразователях сигналов, в системах свя" зи, радио, гидролокации,, сейсмологии, виброметрии и т.ll, Известен цифровой генератор гармонических функций, содержащий задающий генератор, счетчик аргумента и счетчик квадрантов, шифратор, сумматор по модулю два, блок памяти и, кроме того, счетчик числа ординат, счетчик параметра частоты и накапливающий сумматор (1).

Недостатком известного генератора гармонических функций являетсп большой объем памяти, необходимой для хранения значений синуса и косинуса для значений аргумента в интервале л

0 = С/2.

Наиболее близким техническим ренением к предлагаемому является цифровой генератор гармонических функции, 2 содержащий задающий генератор, счетчик аргумента, счетчик квадрантов, шифратор, сумматор по модулю доа, два блока памяти, коммутатор, элемент ИЛИ и, кроме того, второй коммутатор и сумматор с инвертирующиии Вхо дами 1 2).

Недостатком известного генератора является его сложность, обусловленная наличием второго коммутатора и сумма" тора с инвертирующими входами.

Цель изобретения - упрощение цифрового генератора гармонических функций.

Поставленная цель достигается тем, что цифровой генератор гармонических функций, содержащий задающий генератор, счетчик аргумента, счетчик квадрантов, элемент И1%, два блок» памяти, коммутатор, шифратор и сумматор по модулю два, причем выход задающего генератора подключен к входу счетчика аргумента, выходы разрядов которого, кроме старшего разряда, подключены к входам элемента ИЛИ, выход старшего

3 1 0010 разряда счетчи ка а р гумен та под ключе н" к входу счетчика квадрантов, выход элемента ИЛИ, выход старшего разряда счетчика аргумента и выход первого разряда счетчика квадрантов подключены соответственно к первому, второму и третьему входам шифратора, выходы первого и второго блоков памяти подключены к соответствующим информационным входам коммутатора, управляющий вход и вход запрета коммутатора подключены соответственно к первому и второму вь ходам шифратора, выходы первого и второго разрядов счетчика квадрантов ,подключены к входам сумматора по иоду-1 лю два, выходы коммутатора являютсн выходами дробной части косинуса и синуса генератора, третий и четвертый выходы шифратора являются выходами целой части косинуса и синуса генератора, выход сумматора по модулю два и выход второго разряда счетчика квадрантов являются выходами знаковых разрядов косинуса и синуса цифрового генератора гармонических функций, содержит блок преобразования прямого кода в дополнительный код, информационные входы которого подключены к выходаи разрядов счетчика аргумента, кроне старшего разряда, управляющий вход блока преобразования прямого кода в дополнительный. код подключен к выходу старшего разряда счетчика аргумента, выход блока преобразования пряного кода в дополнительный код подключен к адресным входам блоков памяти„

Кроме того, шифратор состоит из элемента ИЛИ-НЕ, элемента НЕ, двух элементов И и сумматора по модулю два, причем первый и второй входы элемента ИЛИ-НЕ и вход элемента НЕ

46 являются соответственно первым, вторым и третьим входами шифратора, первый и второй входы сумматора по модулю два подключены соответственно к второму входу элемента ИЛИ-НЕ и к входу элемента НЕ, выход зле; мента ИЛИ-НЕ и элемента НЕ подключены к входам первого элемента И, выход элемента ИЛИ-НЕ и вход элемента НЕ подключены к входам второго элемента И, выходы элемента ИЛИ-НЕ, сумматора Ilo модулю два, первого и

aToðîão элементов И являются соответ" ственно первым, вторым, третьим и четвертым выходами шифратора. 5$

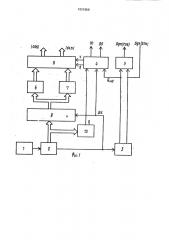

На фиг. 1 представлена функциональная схема цифрового генератора

69 ф гармонических функций; на фиг. 2функциональная схема шифратора.

Цифровой генератор гармонических функций содержит задающий генератор 1, счетчик 2 аргумента, счетчик 1 квадрантов, шифратор 4, сумматор > по модулю два, блоки 6 и 7 памяти, коммутатор 0, блок 9 преобразования прямого кода в дополнительный код, элемент ИЛИ 10. Шифратор 4 содержит элемент ИЛИ-НЕ 11, элемент НЕ 12, элементы И 13 и 14 и сумматор 15 по модулю два.

Генератор гармонических функций работает следующим образом.

На периоде 21с при шаге дискретизации b х аргумента х генератор выдает g = 2 = 2Щьх отсчетов значений синуса и косинуса. Два старших разряда кода аргумента х представляются счетчиком квадраятов, а И -2 младших разрядов — счетчиком ". аргумента. В первом 6 и втором 7 блоках памяти (ПЗУ) по адресам х хранятся соответственно дробные части значенйй

sinx u cosx для й/4 х «» Г/2 - 6 х.

Для формирования адреса при обращении к блокам 6 и 7 памяти используются и-3 младших разряда счетчика 2.

Для выработки значений син са и косинуса произвольного угла (О «х» 2Ж) формируется соответствующим образом адрес и обеспечивается переконмутация выходов блоков памяти B каналы синуса и косинуса. При этом адрес обращения к блокам памяти вырабатывается блоком 9 в зависимости от значения старшего разряда счетчика 2 аргумента (Oct) таким образом, что при Oct

= О, блоки адресуются дополнительным (по модуло 2" ) кодом, а при Oct =, 1 прямым кодом.

Если n-) младших разряда счетчика 2 представлены нулевой комбинацией, то на выходе элемента ИЛИ 10 сигнал ц = О, Во всех остальных случаях ц=1.

При q= О и Oct = О (углы вида

К Е/2; К = 0, 1,,) шифратор 4 вырабатывает сигнал R= 1, который устанавливает на общих группах выходов коммутатора 8 нулевые значения и устанавливает значения разрядов целой части значений функций косинуса 00 и синуса 50, равными соответственно CO =

= Qua, SO = Qua, где Quà — выход младшего разряда счетчика 3. Во всех остальных случаях R= О, CO=0, SO = О.

Если 0ct = Qua, то выход шифратора V= О, при Oct = Qua,V= 1. При V= О

5 10010 коммутатор 8 на выход (cos) подает значение кода дробной части из блока 6, а на выход (sin) - из блока 7.

При Ч= 1 подключение блоков противоположно. Знаки синуса и косинуса формируются на выходе старшего разряда счетчика .3 и выходе сумматора 5 по модулю два.

Шифратор 4 выполняет следующие логические функции: о

R = <90ct, CO = RAQua, SO = КдОца, Ч = Oct Ю Qua.

Предлагаемый генератор требует меньший объем оборудования благодаря отсутствию сумматора и второго коммута- 15 тора.

Формула изобретения

1. Цифровой генератор гармонических функций, содержащий задающий генератор, счетчик аргумента, счетчик квадрантов, элемент ИЛИ, два блока памяти, коммутатор, шифратор и сум- 25 матор-по модулю два, причем выход задающего генератора подключен к входу счетчика аргумента, выходы разрядов которого, кроме старшего разряда, подключены к входам элемен- 3в та ИЛИ, выход старшего разряда счетчика аргумента подключен к входу счетчика квадрантов, выход элемента ИЛИ, выход старшего разряда счетчика аргумента и выход первого разряда счетчика квадрантов подключены соответственно к первому, второму и третьему входам шифратора, выходы первого и второго блоков памяти подключены к соответствующим информационным входам коммутатора, управляющий вход и вход запрета коммутатора подключены соответственно к первому и второму выходам шифратора, выходы первого и второго разрядов счетчика квадрантов подклочены ко входам сумматора по модулю два, выходы коммутатора являются выходамм дробной части косинуса и синуса генератора, третий и четвертый выхо69 4 ды шифратора являются выходами целой части косинуса и синуса генератора, выход сумматора по модулю два и выход второго разряда счетчика квадрантов являются выходами знаковых разрядов косинуса и синуса цифрового генератора гармонических функций, отличающийся тем, что, с целью упрощения он содержит

) блок преобразования прямого кода в дополнительный код, информационные входы которого подключены к выходам разрядов счетчика аргумента, кроме старшего разряда, управляющий вход блока преобразования прямого «ода в дополнительный код подключен « выходу старшего разряда счетчика аргумента, выход блэка преобразования прямого кода в дополнительный код подключен к адресным входам блоков памяти.

2. Генератор по п. 1, о т л ич а ю шийся тем, что шифратор состоит из элемента ИЛИ-НЕ, элемен" та HF, двух элементов И и сумматора по модулю два, причем первый и второй входы элемента ИЛИ-НЕ и вход элемента НЕ являются соответственно первым, вторым и третьим входами, шифратора, первый и второй входы сумматора по модулю два подключены сооТ ветственно к второму входу элемен" та ИЛИ-НЕ и к входу элемента НЕ, выходы элемента ИЛИ-НЕ и элемента НЕ подключены к входам первого элемента И, выход элемента ИЛИ-НЕ и вход элемента НЕ подключены « входам второго элемента И, выходы элемента

ИЛИ-НЕ, сумматора по модулю два, l

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

h 662927, кл. 606 Г 1/02, 1979.

2. Авторское свидетельство СССР по заявке h 2815954, 18-24, кл. 5065 1/02; 1979 (прототип).

1 0(31069

gn(sin) 1001069

Составитель В. Бойков

Ре8актоц Н. Гришанова Техред М. Гергель, Корректор Н. Король

Заказ 1395/54 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открнтий

113035 Москва Ж- 5 Ра иская набд д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, Г