Преобразователь двоичного кода в код системы остаточных классов

Иллюстрации

Показать всеРеферат

) Авторы изобретеиия

А. П. Болтков, Н. И. Червяков и C.. Í. Xëåâíâè ...

; ji j J

4 ф (7! ) Заявитель

1 (5>t ) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В КОД СИСТЕМЫ

ОСТАТОЧНЫХ КЛАССОВ

Изобретение относится к вычислительной технике и -может быть использовано для согласования с вычислительными устройствами, функционирующими в СОК, а также в технике связи при использовании передачи информации кодами СОК. Известен преобразователь кодов позиционной системы счисления в коды

СОК, содержащий входные регистры, разрядные преобразователи, выполненные на цифровых элементах распределения тока с числом сердечников, равным значению соответствующего модуля системы, обмотки записи каждого сердечник - с соответствующими выходами соответствующего входного регистра, а обмотки считывания соединены с, входами арифметического устройства по соответствующему модулю "исте- 20 мы (1).

Однако преобразователь обладает большим объемом оборудования, обусловленным функционированием в десятичной системе счисления.

Наиболее близким к предлагаемому по тех ни чес кому решению я вляется преобразователь двоичного кода в код системы остаточных классов, содержащий входной регистр, блок умножения старшего разряда на основание двоичной системы, корректирующий сумматор по соответствующему модулю, блок умножения промежуточного результата по соответствующему модулю и выходной регистр, причем выход предпоследнего старшегп разряда входного регистра соединен через корректирующий сумматор с блоком умножения промежуточного результата, выходы которого соединены с входами выходного сумматора и корректирующего сумматора, вход которого соединен через блок умножения старшего разряда с выходом последнего старшего разряда входного регистра, выход

3 10010 младшего разряда которого соединен с входом выходного сумматора 21.

Однако известный преобразователь обладает низкой скоростью перевода преобразуемого числа в код СОК, так как для перевода (К+1 ) разрядного двоичного числа в код СОК требуется

2К тактов работы известного устройства, что при больших значениях К может составить значительную величи- 1© ну.

Цель изобретения - повышение быст» родействия.

Поставленная цель достигается тем, что в преобразователь двоичного кода в код системы остаточных классов, содержащий входной регистр разрядностью к, блок умножения на основание двоичной системы по модулю Р„, сумматор по модулю P„" {1 = 1,2, L ) с - ко- эв личество оснований системы ) разрядностью,Й +174mаP (и.+1) С к, первый вход которого йодключен к выходу ,(K-È).ro, разряда входного регистра, а второй вход — к выходу блока умножения: на основание двоичной системы, содержит первый и второй коммутатора, первый и второй вспомогательные регистры, соответствующие информаци онные входы которых объединены и подключены к соответствующим выходам сумматора по модулю Р,, а информационные выходы подключены соответственно к первой и второй группам входов . первого коммутатора, группа выходов которого подключена соответствен-. но к первой группе входов второго ком.мутатора, вторая группа входов которого подключена к группе (к-И+1) старших разрядов входного регистра, а группа выходов соответственно подключена к группе информационных sxo-. дов блока умножения на основание двоичной системы по модулю Р„, управляющие входы входного регистра, первого и второго дополнительных регистров

45 являются соответственно входом сдвига, входом основной записи и входом

Дополнительной записи устройства, rpynna выходов сумматора по модулю Р, .является выходом преобразователя.

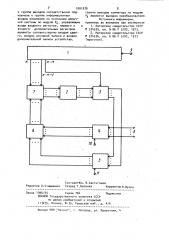

На чертеже представлена функциональная схема преобразователя.

Схема содержит входной регистр

1, блок 2 умножения на основание дво ичной системы по модулю P сумматор

3 по модулю Р, первый и второй дополнительные регистры 4 и 5, первый

79 4 и второй коммутаторы 6 и 7, выход 8 устройства, первый, второй и третий управляющие входы 9-11 устройства.

Преобразователь работает следующим образом.

К + 1 - разрядное двоичное число.

Х, равное может быть переведено в код COK no выбранному модулю P- с помощью из-. вестного алгоритма

Ф

- Q=XmodP;=(- (A„2%A „)2eodP„+

A„ }ðñ2иос Р„+-- + AÄ} oaPÄ+ о).

vnod Р

Если выбранный модуль Р„ имеет разрядность и +1 Ъ Bog Р, то значение выбранного модуля Р лежит в пределах и 2 «е Р% 2и+11 (При этом любое число В, имеющее разрядность И, будет всегда меньше выбранного модуля P так ко В

1 лежит в пределах

«««« " (4 )

Следовательно, учитывая (3) и (4), < Р. °

Перевод числа Х, согласно известному алгоритму (2), начинается со старших разрядов.

Рассмотрим операцию перевода старших разрядов.

В =(--(Ак2+Ак- ) 2и оа Р„-+ °"

„. +Ак, )1вчойР„ (5)

В процессе преобразования первых старших разрядов числа Х ни в одном из тактов не возникает необходимости коррекции результата по выбран" ному модулю. Таким образом, операция перевода И старших разрядов числа Х будет представлена как

9"=(...(А 2+Ак 1)2.--А к „ <)2A к-и+"=

=А 2и "+A к-12и "+" + Д„„+1 (<)

И дальнейший процесс. перевода будет аналогичен известному алгоритму (2), т.е.

Х=-Xod P;+. -. +A„) Q.cod P„. +A, ) od P„(l)

Таким образом,в исходном состоянии во входной регистр 1 записывается знаS 1001 чение переводимого двоичного кода Х, дополнительные регистры 4 и 5 очище- ны, коммутатор 7 подключает к входам блока 2 умножения И старших разрядов входного регистра 1, коммутатор 6 под-3 ключает к первой группе входов коммутатора 7 выходы дополнительного регистра 4.

В первом такте значение И старших разрядов преобразуемого числа X из входного регистра 1 поступает через коммутатор. 7 на входы блока 2 умножения, где происходит умножение значения И старших разрядов на два по модулю Р, значение результата посту- 1

1 пает на входы сумматора 3, на другой вход которого подается значение (к-И)-го разряда числа Х из входного регистра 1, результат операций этого такта по окончанию переходных процессов яо управляющему сигналу, поданному по входу 10, записывает результат операций первого такта в дополнительный регистр 4. Таким обра" зом, в пеовом такте выполняется опеРациЯХ„=(Ь rnOdP„+A 1< „) юО4 Р„°

Во втором такте по сигналу, поданному по входу 9, происходит сдвиг содер. жимого входного регистра 1 на один разряд влево, а коммутатор 7 под- зр: ключает выходы коммутатора 6 к входам блока умножения и в этом сос. тоянии останется до конца преобразования. При -этом содержимое первого такта преобразования через коммутаторы 6 и 7 поступает на блок 2 умножения, результат умножения суммирует ся сумматором 3 по модулю Р со значением (к-я -1)-ro разряда преобразуемого числа Х. По окончании переходных процессов управляющий сигнал, поданный по входу 11, разрешает запись результата операции в дополнительный регистр 5. Таким образом, во втором такте выполняются операции

079 С образом, в третьем такте выполнена операция .

Хз= (Х 3-1иОд Р„+А к-м+ ) юОДР

В последнем такте преобразования .результат предпоследнего такта преоб разования множится на два по модулю

P. блоком 2 умножения и результат

,умножения суммируется сумматором 3 по модулю Р со значением самого младшего разряда Ао преобразуемого числа Х. Окончательный результат преобразования снимается с выходов сумматора 3 по модулю Р;; . Для преобразования (к+1)-го разрядного двоичного числа Х в код

С0К по основанию Pj разрядностью

И+1 потребляется К-0+1 тактов работы устройства, в то же время известное устройство требует 2К тактов работы..

Таким образом, введение в состав предлагаемого преобразователя двух компараторов и двух. дополнительных регистров с соответствующими устройствами позволяет повысить быстродействие преобразователя.

Преобразователь двоичного. кода в код системы остаточных классов, содержащий входной регистр раз- рядностью к, блок умножения на осно-, вание двоичной системы по модулю Р- сумматор ло модулю Р„ (i=1,2,..., количество оснований системи)

t разрядностью И +17ЯО@ Р„(n.»-e) с (К, первый вход которого подключен к выходу(y.†- И )-го разряда блока умножения на основание двоичной системы, отличающийся тем, что, с целью повышения быстродействия, он содержит первый и второй коммутаторы, первый и второй допол-. нительные регистры, соответствую" щие инФормационные входы которых обьединены и подключены к соответствующим выходам сумматора по Мо дула Р„, а информационные выходы подключены соответственно к первой и второй группам входов первого коммутатора, группа выходов ко" торого подключена соответственно к первой группе входов второго .коммутатора, вторая группа входов которого подключена к группе (к-И +1 ) старших разрядов входного регистра, 2 (Х „2.ю04 Р1+Д к » „1 ) Nod Р» .

В третьем также осуществляется сдвиг содержимого входного регистра

1 на один разряд влево, коммутатор 6 подключает выходы дополнительного регистра 5 к второй группе входом коммутатора 7, результат второго такта умножается блоком 2 умножения на два по модулю Р1 и суммируется сумматором 3 по модулю Р1 со значе" йием1к-М-1)-го .разряда числа X.Таким

Формула изобретения

7 1001079 8 а rpynna выходов соответственно под- группа выходов сумматора по модулю ключена к группе информационных Р является выходом преобразователя. входов умножения на основание двоич- Источники информации, ной системы по модулю P«, управляющие принятые во внимание при экспертизе входы входного регистра, первого и з 1. Авторское свидетельство СССР второго: дополнительных регистров 11 374535, кл. G 06 F 5/02, 1973. являются соответственно входом сдви- 2. Авторское свидетельство СССР га, входом основной записи и входом И 374536, кл. G 06 F 5/02, 1973 дополнительной записи устройства, (прототип).

Составитель В. Евстигнеев

Редактор A. Стащишина Техред Т. Маточка Корректор И. Шулла

Заказ 1396/55 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент, г. Ужгород, ул. Проектная, 4