Устройство для вычисления модуля комплексного числа

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик (и) l О01085

ОП ИСАНИЕ

ИЗО6РЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву-(22) Заявлено 12. 10. 81 (2l ) 3343240/18-21 с присоединениеМ заявки М— (23) Приоритет— (54)M К>

О 06 С 7/38

Гееударстеелньй кемктет (53) УДК б81. 3 (088. 8) Опубликовано 28. 02. 83. Бюллетень М 8 пе делам каебретеккй и открытий

Дата опубликования описания 28.02.83

А.В. Дрозд, Е. Л. Полин; И.Ф. /ИураййЦвц ...

А.Н.. Романов и В.А. Соко/крв ; —, "Ф, . .

r А з, з 1

) - -11, ;„) 3-., Одесский ордена Трудового Красног мейи / политехнический институт (72) Авторы изобретения (7l ) Заявитель (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ИОДУЛЯ

КОМПЛЕКСНОГО ЧИСЛА

)

Изобретение относится к вычислительной технике.

Известно устройство для вычисления модуля комплексного числа, содержащее регистры, сумматоры, коммутаторы, бло5 ки сдвига, элементы. НЕ, блок анализа знака f1).

Недостатком данного устройства яв:ляется низкое быстродействие.

1О

Наиболее близким. к предлагаемому по технической сущности является уст ройство для вычисления модуля комп-. лексного числа, которое содержит регистры, сумматоры и коммутаторы npuf5 чем входы первого и второго регистров подключены к первому и второму входам устройства, прямые выходы разрядов первого регистра подключены к группе первых входов первого суммато- ro ра соответственно, выход первого коммутатора подключен к первому входу второго сумматора. прямые выходы разрядов первого регистра подключены к

2 первым группам информационных входов первого и второго коммутаторов, вторые группы информационных входов которых подключены к прямым выходам разрядов второго регистра, инверсные выходы которых подключены к группе вторых входов первого сумматора, выход которого подключен к управляющим входам первого и второго коммутаторов, выход второго коммутатора подключен к второму входу второго сумматора, выход которого подключен к выходу устройства (2

Недостатком известного устройства является его низкое быстродействие. Цель изобретения - повышение быст-. родействия устройства.

Поставленная цель достигается тем, что устройство для вычисления модуля комплексного числа, содержащее регистры, сумматоры и коммутатор, причем входы разрядов первого и второго регистров подключены к информационным

3 10010 входам устройства, прямые выходы разрядов первого регистра подключены к первой группе входов первого сумматора, инверсные выходы разрядов второго регистра подключены к второй группе входов первого сумматора, прямой и инверсные выходы знакового разряда которого подключены к управляющему входу коммутатора, устройство содержит также третий сумматор, причем первая 16 группа входов второго сумматора подключена к прямым выходам разрядов первого регистра„{п-2) старших разрядов которого подключены к первой группе входов третьего сумматора, вторая группа входов которого подключена к прямым выходам разрядов второго регистра, прямые выходы (n-2) старших разрядов которого подключены к второй группе входов второго сумматора, вы-,2в ходы разрядов второго и третьего сумматоров подключены к первой и второй группе информационных входов коммутатора соответственно, выход которого подключен к выходу устройства. 25

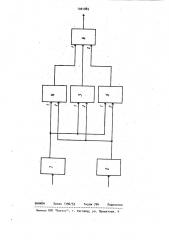

На чертеже представлена структур.ная схема устройства.

Устройство содержит первый регистр

1, второй регистр 2, первый сумматор

3, второй сумматор 4, третий сумматор зв

5, коммутатор 6.

Устройство работает следующим образом.

В начальный момент времени в первыи регистр 1 и второй регистр 2 зазю носятся соответственно и-разрядные мантиссы прямых кодов действительной и мнимой составляющих комплексного числа.

С выхода первого регистра 1 прямой код действительной. составляющей поступает на первые входы первого 3 и второго 4 сумматора, а и-2 старших разрядов этого кода — на первый вход третьего сумматора 5.

С выхода второго регистра 2 инверс- ный код мнимой составляющей поступает на второй вход первого сумматора 3, прямой код — на второй вход третьего сумматора 5, à и-2 старших разряда этого кода - на второй вход второго сумматора 4.

Сигнал с выхода знакового разряда сумматора 3 поступает на управляющий вход коммутатора 6, на первые инфор- И мационные входы которого поступает с ! выхода второго сумматора 4 результат сложения кода действительной состав85 ляющей с мнимой, сдвинутой на два разряда в сторону младших разрядов.

На вторые информационные входы коммутатора 6 поступает с выхода третьего сумматора 5 результат сложения кода мнимой составляющей с действительной, сдвинутой на два разряда в сторону младших разрядов. При соответствующем управляющем сигнале, подаваемом на коммутатор, на его выходе вырабатывается результат сложения большей составляющей комплексного числа с меньшей составляющей, сдвинутой на два разряда в сторону младших раз- . рядов.

Коммутатор 6 представляет собой набор из и элементов 2 И-ИЛИ, на входы каждого элемента подаются соответственно сигналы с выходов второго и третьего сумматоров 4 и 5 и два управляющих. сигнала, являющихся прямым и инверсным сигналами знакового разряда.

На выходе коммутатора 6 в зависимости от управляющих сигналов образуется результат снимаемый с выхода второго или третьего сумматоров 4 или 5.

Устройство позволяет производить вычисление модуля комплексного числа при повышении быстродействия по сравнению с прототипом.

Время выполнения вычислений в предлагаемом устройстве оказывается меньше по сравнению с прототипом на задержку сумматора (при несущественном изменении в затратах оборудования— вместо одного коммутатора введен третий сумматор) .

Реализация устройства для вычисления модуля комплексного числа связана с развитием цифровой обработки сигна— лов в задачах спектрального анализа и является новой перспективной областью вычислительной техники.

Устройство по сравнению с прототипом позволяет повысить быстродействие вычисления модуля комплексного числа.

Задержка, вносимая базовым устройством С =2 + С,, где Сс задержка иразрядного сумматора; С вЂ” задержка коммутатора.

Задержка, вносимая устройством C =

= с %к +Ye учитывая, что > (1<

V- +Т .

Выигрыш в быстродействии без существенных изменений затрат оборудования составляет -" =Т, относительный выигрыш; 5 Yc .

2 с+ к

5 1001

Формула изобретения

Устройство для вычисления модуля комплексного числа, содержащее регист. ры, сумматоры и коммутатор, причем входы разрядов первого и второго ре- % гистров подключены к информационным входам устройства, прямые выходы разрядов первого регистра подключены к первой группе входов первого суммато. ра,инверсные выходы разрядов второго регистра подключены к второй группе входов, первого сумматора, прямой и инверсный выходы знакового разряда которого подключены к управляющему входу коммутатора, о т л и ч а ю щ е- е с q. тем, что, с целью повышения быстродействия устройства, в него введен третий сумматор, причем первая группа входов второго сумматора подключена к прямым выходам разрядов 20

085 6 первого регистра, (И-2) старших разрядов которого подключены к первой . группе входов третьего сумматора, вторая группа входов которого подключена к прямым выходам разрядов второго регистра, прямые выходы (h-2) стар, ших разрядов которого подключенй к, второй группе входов второГо сумматора, выходы разрядов второго и треть" его сумматоров подключены к первой и второй группе информационных входов, коммутатора соответственно, выхоД которого. подключен к выходу устройства.

Источники информации, принятые во внимание при экспертизе

1 ° Авторское свидетельство СССР

11 623202, кл. G 06 F 7/38, 1976.

2. Авторское свидетельство СССР по заявке У 2977566/18-24, кл. G 06 F 7/38, 1978 (прототип).

ВНИИПИ Заказ 1396/55 Тираж 704 Подписное филиал ППП "Патент", г. Ужгород, Ул. Проектная, 4