Устройство для вычисления функций синуса и косинуса

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскин

Социвпистическин республик (i )! 00! 093 (6I ) Дополнительное к авт. саид-ву (22)Занвлено 27.10.81 (2l) 3350755/18 24 с присоединением заявки № (23) Приоритет

Опубликовано 28.02.83. Бюллетень № 8

Дата опубликования описания 28.02.83 (5! )М. Кд.

406 F 7/548

Гкударстеенный камнтвт

СССР.вв делам наабретеннй н нтнрмтнй (53) УДК681. .325 (088.8) (72) Авторы В. Ф. Евдокимов, Ю, Т. Киэим, B. В. Литвиненко, В. В. |1охор изобретения и Ю. А. Плющ (7 ) Заявитель дяотитут проблем моделиролеиия и елергетеи ььее«реллояод.ССР (54) УСТРОЙСТВО ДЛЯ ВЪ|ЧИСЛЕНИЯ ФУНКБИИ

СИНУСА И КОСИНУСА

Изобретение относится к автоматике и вычислительной технике для нахождения тригонометрических функций н может быть применено в цифровых устройствах обработки информации.

Известно устройство, содержащее два усилителя, выходы которых соединены с входами сумматора и два блока памяти (1 .

Недостатком этого устройства явля10 ется ограниченный диапазон измерения аргумента.

Наиболее близким к предлагаемому по технической сущности является ус » !

5 ройство, содержащее три блока памяти, два умножителя и сумматор, входы которого соединены с выходами умножителей, выходы первого и второго блоков памяти соединены с входами первого щ умножителя, входы второго умножителя соединены с выходом третьего блока, памяти и входом части аргумента устройства, другие разряды которого соеди2 иены с входами первого и второго блоков памяти 2 ).

Недостатком известного устройства является низкая точность.

Цель изобретения — увеличение точности вычисления функций.

Поставленная цель достигается тем, что в устройство для вычисления функций синуса и косинуса, содержащее три блока памяти два умножителя и сумматор, входы которого соединены с выходами первого и второго умножителей> первый и второй входы первого умножителя соединены соответственно с первым выходом первого блока памяти и выходом второго блока пеамяти, выход сумматора соединен с выходом синуса устройства, дополнительно введе» ны третий и четвертый умножители, вычитатель и блок управления, первый и второй входы которого соединены соот» ветственно с входом аргумента и тактовым входом устройства, выход блока управления соединен с управляющими

1001093

3 входами блоков памяти второй выход

J первого блока памяти соединен с первыми входами второго и третьего умножителей, второй вход третьего умножителя соединен с выходом второго блока памяти, выход третьего блока памяти соединен с вторым входом второго и первым входом четвертого умножителей, второй вход четвертого умножителя соединен с первым выходом первого блока 1© памяти, информационный вход которого соединен с входом опорного значения функции устройства, выходы третьего и четвертого умножителей соединены с входами вычитателя, выход которого со- И единен с информационным входом второго блока памяти и выходом косинуса устройства, выход сумматора соединен с информационным входом третьего блока памяти, 20

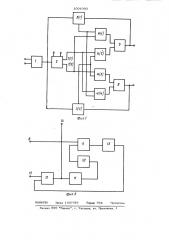

Блок управления содержит элемент И, счетчик, группу элементов НЕ, сумматор по модулю два и элемент И-НЕ, вход и выход которого соединены соответственно д с выходом сумматора по модулю два и первым входом элемента И, второй вход и выход которого соединены соответственно с вторым входом блока управления и входом счетчика, выходы разрядов которого через соответствуюшие элементы HE группы соединены с первой группой разрядных входов сумматора по мс дулю два вторая группа которых соединена с первым входом блока управления, выход которого соединен с выходом эле35 мента И.

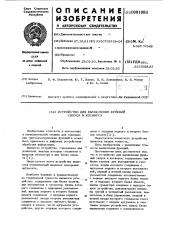

На фиг, 1 представлена блок-схема устройства, на фиг. 2 - вариант реализации блока управления.

46

Устройство для вычисления функций синуса и косинуса содержит блок 1 управления, блоки 2 и 3 памяти, умножители

4, сумматор 5, вычислитель 6, выходы

7 блока 2 памяти. Е1ифры в скобках по

1$ казывают аналогичность реализации указанных блоков.

На первом такте работы устройства на вход 8 поступает аргумент данной функции, Данный аргумент и значение, записанное в счетчике 11, симмируются в сумматоре 9 по модулю два, причем в сумматор 9 из счетчика 11 поступает инверсное значение. При несовпадении значений, подаваемых на сумматор 9, на выходе группы И-НЕ 13 получаем "1".

Зтот сигнал поступает на элемент И

12 и при подаче на вход 15 синхроимпульс попадает в счетчик 11, блок 2 памяти и блоки 3 (1) и 3 (2) памяти.

На выходе 7(1) блока 2 памяти, при поступлении на него сигнала, получаем

Sin 1, на выходе 7(2) — значение cos с

1 . Значение 5 п 1 подается с выхода о

7(1) блока 2 на входы умножителей

4(2) и 4(4), значение coo 1 — на входы умножителей 4(1) и 4(3), В это же время из блока 3(1) памяти по сигналу, идушему с блока 1 управления, поступает на вход умножителей 4(1) и 4(4) записанный рвнее О, из блока 3(2) памяти на вход умножителей 4(2) и 4(3)записанная ранее 1. Полученное на выс ходе умножителя 4(2) значение Sill 1 . поступает через сумматор 5 в блок 3(1) памяти. Полученное на выходе умножителя 4(3) значение со5 1 поступает чео рез вычислитель 6 в блок 3(2) памяти, На втором такте работы цифрового преобразователя снова происходит суммирование по модулю два аргумента и кода, записанного в счетчике. В случае их неравенства на выходах элемента И-HE снова получаем сигнал, поступаюший в счетчик 11, блок 2 памяти, блоки 3(1) и 3(2) памяти, П и этом с выхода 7(1) полученный Б1п 1 подается на входы умножителей 4(2) и 4(3), полученное о значение cos 1 поступает на входы умножителей 4 (1) и 4 (4) . Из блока 3 (1) памяти поступает на вход умножителей

4(1) и 4(4) значение sin 1, из блока

3(2) памяти поступает на вход умножителей 4(2) и 4(3) значение coS 1о.

Блок 1 управления содержит вход 8 аргумента, сумматор 9 по модулю два, группу 10 элементов НЕ, счетчик 11„ элемент И 12, элемент И-НЕ 13, выход

14 и вход 15 тактовых импульсов.

Работу устройства рассмотрим на примере, Пусть необходимо вычислить синус и косинус угла 10, На информационном входе блока 2 памяти имеем значение

sin 1 и cos 1 . Блок 2 памяти может о о быть выполнен на группе элементов И.

После перемножения соответствуюшие произведения поступают на сумматор 5 и вычитатель 6. На выходе сумматора

5 получаем значение S

3(1) и З(2) памяти.

На следующих тактах работы преобразователя находим синус и косинус Ъ и 4 и так далее до значения аргумента, синус и косинус которого нуж5 100 но определить. При равенстве эна чения, записанного в счетчике, со значением аргумента на выходе элемента И-НЕ появляется О, устройство прекрашает свою работу и на его выходе будут значения синуса и косинуса аргумента, подаваемогр на вход устройства. Число тактов работы определяется величиной аргумента и выбранным шагом.

Формула изобретения

1. Устройство для вычисления функций синуса и косинуса, содержашее три блока памяти, два умножителя и сумматор, входы которого соединены с выходами первого и второго умножителей, первый и второй входы первого умножителя соединены соответственно с первым влкодом первого блока памяти и выходом второго блока памяти, выход сумматора соединен с выходом синуса устройства, о т л и ч а ю ш е е с я тем, что, с целью увеличения точности вычисления, в него введены третий и четвертый умножители, вычнтатель и блок управления, первый и второй входы которого соединеньг соответственно с входом аргумента и тактовым входом устройства, выход блока управления соединен с управляю» шими входами блоков памяти, второй выход первого блока памяти соединен с первыми входами второго и третьего умножителей, второй вход третьего умножителя соединен с выходом второго блока памяти, выход третьего блока памяти соединен с вторым входом второго и пер1093 6 вым входом четвертого умножителей, второй вход четвертого умножителя соединен с первым выходом первого блока памяти, информационный вход которого соединен . с входом опорного значения функции уст ройства, выходы третьего и четвертого умножителей соединены с входами вычит6 теля, выход которого соединен c информационным входом второго блока памяти !

О и выходом косинуса устройства, выход сумматора соединен с информационным входом третьего блока памяти.

2. Устройство по п.1, о т л и ч а - ю ш е е с я тем, что, блок управле15 ния содержит элемент И, счетчик, галлу элементов НЕ, сумматор по модулю два и элемент И-НЕ, вход и выход которого соединены соответственно с выходом сум матора по модулю два и первым входом

20 элемента И, второй вход и выход которого соединены соответственно с вторым входом блока управления и входом счетчика, выходы которого через соответствуюшие элементы НЕ группы соединены

25 с первой группой разрядных входов сумматора по модулю два, вторая группа которых соединена с первым входом блока управления, выход которого соединен. с выходом элемента И.

Источники информации, принятые во внимание при экспертизе

1. Оранский А. М. Аппаратные методы в цифровой вычислительной технике, 5 с. 49-50, рис. 2.6.

2. Смолов B. Б. Функциональные преобразователи информации, Л., Энергоиздат, с. 30, рис. 2.8 (прототип).

1001093 (лиг. 2

ВНИИПИ Заказ 1397/56 Тираж 704 Полписно

Филиал ППП Патент, г. Ужгород, ул. Протекная, 4