Устройство для извлечения квадратного корня из суммы квадратов

Иллюстрации

Показать всеРеферат

O ll H C A H N E

ИЗЬБРЕТЕН ИЯ

Союз Советсиик

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву (22)Заявлено 09.09.81 (21) 3337348/18 24 (5!)М. Кд.

Я 06 F 7/552 с присоединением заявки М

ГаеударстаеакыИ каиатет

СССР (23 } П риоритет.

Опубликовано 28.02.83 Бюллетень Р1т 8

Дата опубликования описания 28.02.83 вв Аааам ктобратенкй к аткрыткй (53) -УД К 681. .325 (088.8)i (72} Авторы изобретения

И. Я. Миронов, Ю. В. Малинин, Т. Г. Лазебник и Л. . И .:Новик

I 1

l

1 ва (71} Заявитель (54) УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КВАДРАТНОГО, КОРНЯ ИЗ СУММЫ KBAllPATOB

Изобретение относится к вычислительной технике и может быть использовано в различных цифровых функциональных преобразователях, а также в устройствах обработки дискретной информации.

Известно устройство для вычисления квадратного корня, из суммы квадратов, содержащее сумматоры, вычитатели, первый и второй элементы выделения модуля коммутатор, схемы сравнения, блок1

1О умножения на коэффипиент (1 ) .

Недостатком данного устройства является сложность схемы и его низкая точность вычисления.

Наиболее близким к предлагаемому по технической сущности является устро ство для вычисления функпии 2=С к + 2 содержащее блок нахождения модуля величины Х, блок нахождения модуля величины у, сумматор, блоки сдвига, блок суммирования-вычитания, блок коммутации, блок управления, три блока сравнении. элементы ИЛИ, входные и выходные шины устройства 523 .

Недостатком известного устройства является его низкая точность.

Цель изобретения - повышение точности вычисления функции.

Поставленная цель достигается тем, что в устройство, содержащее первый и второй блоки выделения модуля, информапионные входы которых являются соответствуюшими информационными входа- . ми устройства, сумматор-вычйтатель первый информационный выход которого является выходом устройства, блок управления, первый выход которого соединен с управляющими входами первого и второго блоков выделения модуля и первым управляющим входом сумматора-вы читателя, коммутатор, первый и второй. управляющие входы которого соединены с вторым и третьим выходами блока управления, введены множительно-делительный блок и сдвиговый регистр, выход первого блока выделения модуля соединен с первым информационным входом сумматора-вычитателя и с первым ин1х! IYI

1 IX t+IYI

3 100 10 формационным входом первой группы входов коммутатора, три выхода которого соединены.с тремя входами множительно-делительного блока, выход второго блока выделения модуля подключен к второму информационному входу сумма» тора-вычитателя и к второму информационному входу первой группы входов коммутатора, третий информационный вход первой группы входов которого соединен Io с вторым информационным выходом сумматора-вычитателя и входом сдвигового регистра, выход множительно-делительного блока подключен к третьему информационному входу сумматора-вычитателя и к 15 первому и второму информационным входам второй группы входов коммутатора, третий информационный вход второй группы входов roòoðoãî соединен с выходом сдвигового регистра, четвертый выход щ блока управления подключен к второму управляющему входу сумматора-вычитателя.

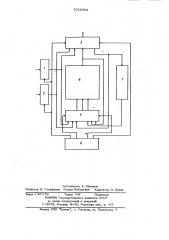

Структурная схема устройства для извлечения квадратного корня из суммы р квадратов приведена на чертеже.

Устройство содержит первый блок 1 выделения модуля, второй блок 2 выделения модуля, сумматор-вычитатель 3, множительно-делительный блок 4, ком- З© мутатор 5, блок 6 управления, сдвиговый р ег ис тр 7.

Предлагаемое устройство реализует приближенную формулу вычисления корня квадратного из суммы квадратов.

ЭЗ

Xz+>2Ixl+lYl Д Д (р)

Ix l I v l

1 1

Д. =

2 g(Ix I+Ig I — Д., ) Поправки Ь„; dZBbIBQABHbI из следующих соотношений, Для вычисления первой поправки d рассматривается выражение 1(2+ Y =

=Цх1+1ч1-д )2.

1 2

4$

Принимается, что Д2 О, тогда получаем

Для вычисления второй поправки рас- 30 сматривается выражение ХZ 4. >Z =

=(Ix 4!31-д„-,д2) 2 откуда следует, что Ь,„+Ь2 -2ЦХ!+!у!-Д„) Д2=0.

Принимается что д О.

Я

Д

Тогда Д1 1

g (I x I +1Y I — и ) 94 4

В итоге получаем соотношение для вычисления квадратного корня из суммы квадратов двух чисел с точностью 0,2%.

Предлагаемое устройство работает следующим образом.

Управляющий импульс с первого выхода блока 6 управления поступает на управляющие входы первого и второго блоков 1 и 2 вьщеления модуля, запускает устройство а через первый управляющий вход сумматора-вычитателя 3 переводит последний в нулевое состояние, на информационные входы которого поступают абсолютные значения входных величин 1 Х l, У1, которые также поступают на первый и второй входы первой группы входов коммутатора 5, сумматор-вычитатель 3 производит суммирование величин Х l и 1 У l и на его второй информационный выход поступает величина (I Х 1+ I У1). Второй управляющий . импульс блока 6 управления, поступающий на первый управляющий вход коммутатора 5, соединяет первую группу вхо дов коммутатора 5 с его выходами„в результате чего величины 1 Х1, I УI (I Х I + 1У1) поступают на множительноделительный блок 4, которое вычисляет, 1Х 11у1 первую поправку по формуле Д =

IХ I+ IY I

Величина первой поправки поступает на вычитаюший вход сумматора-вычитателя)

3 где вырабатывается величина (! X I +

+1У1-Ьg. Эта величина удваивается на сдвиговом регистре 7 и величина

2(1х!+1У1-Az) поступает на третий вход второй группы входов коммутатора 5, на первый и второй входы второй группы которого поступает с выхода множительно-делительного блока 4 величина d1. Третий управляющий импульс блока 6 управления, поступающий на второй управляющий вход коммутатора 5, соединяет вторую группу входов коммутатора с его выходами, поэтому на множительно-делительный блок 4 поступают величины Ь., Ь,! 2(jx!+IYI д ) в результате чего с выхода последнего на вычитаюший вход сумматора-вычитатеД. Д ля 3 поступает величина Д2—

2((Х1Ф I. I -Д1) которая вырабатывает величину

1 +у2 = Ix I+ tel-д, - а, 1х11у1 1 1

Ь Д ! х11Ч1 2 3(lxl+IYI — Ь„) 10010

Укаэанная величина поступает на йервый информационный выход сумматоравычитателя 3 являюшийся выходом устройства, по управляющему импульсу, поступаюшему на второй управляющий вход с четвертого выхода блока 6 управления.

Точность приближенной формулы (1) показана на примерах.

Введем обозначения: 1о

A - точное значение искомой величины;

В - приближенное значение искомой величины;

d - точность приближенной формулы в процентах.

А= х +w; ь=(х1+1М-л -а

2 2, 1

1Х!И1 . Ь1

20 д

1Х 1+ 1 2 2 (1х1+ Ь! -а.1)

Cp = 400ooй .

А

Экономический эффект от использова- 25 ния предлагаемого изобретения достигается за счет применения приближенной

l формулы для вычисления поправок (1) и использования для этого множительно делительного блока, что позволяет ловы- М еить точность вычисления квадратного кор,"ня из суммы квадратов.

Формула изобретения

Устройство для извлечения квадратного корня из суммы квадратов, содержащее первый и второй блоки выделения модуля, информационные входы которых являются соответствующими информационными входами устройства, сумматор-вычитатель первый информационный выход которого является выходом устройства, 94 d блок управления, первый выход которого соединен с управляющими входами первого и второго блоков выделения модуля и первым управляющим входом суммато» ра-вычитателя, коммутатор, первый и второй управляющие входы которого сое» динены с вторым и третьим выходами блока управления, о т л и ч а ю ш е е с я тем, что, с целью повышения точности вычисления, в него введены множительно-делительный блок и сдвиговый регистр, выход первого блока в -щелеиия модуля соединен с первым информационным входом сумматора-вычитателя и с первым информационным входом первой груп"ы входов коммутатора, три выхода которого соединены с тремя входами множительноделительного блока, выход второго блока выделения модуля подключен к второму информационному входу сумматора-вычитателя и к второму информационному входу первой группы входов коммутато» ра, третий информационный вход первой группы входов которого соединен с вторым информационным выходом сумматора-вычитателя и входом сдвигового регистра, выход множительно-делительного блока подключен к третьему информационному входу сумматора-вычитателя и к первОму и второму информационным входам второй группы входов коммутатора, третий информационный вход второй группы входов которого соединен с выходом сдвигового регистра, четвертый выход блока управления подключен к второму управляющему входу сумматора-вычитателя.

Источники информации принятые во внимание при экспертизе

1. Авторское свидетельство СССР

N 813424, кл. 5 06 F 7/552, 1981.

2, Авторское свидетельство СССР

М 634271, кл. 6 06 F 7/552, 1976 (прототип) .

1001094

Составитель А. Шуляпов

Рецактор Н. Стащишина Texpen Ì.Êoøòóðà Корректор О. Билак

Заказ 1 397/56 Тираж 704 Поцписное

ВНИИПИ Госуцарственного комитета СССР по целам изобретений и открытий

113035, Москва, -35, Раушская наб., ц. 4/5

Филиал ППП "Патент, г. Ужгороц, ул. Проектная, 4