Устройство для контроля оперативной памяти

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

<ий 001181 (61) Дополнительное к авт. свид-ву (22) Заявлено 260881 (21) 3329725/18-24 (31} М. Кт1.з

G 11 С 29/00 с присоединением заявки ¹I

Государственный комитет

СССР но делам изобретений н открытий (23) ПриоритетОпубликовано 280283. Бюллетень № 8 (33}УДК 681.327 (088. 81

Дата опубликования описания 280283 ф: ., (. А

B.A. Резван, О B. Летнев, tO. C ° 1бакарькнц и - А, .К,.)<риего ов у (72) Авторы изобретения

l i (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ОПЕРАТИВНОЙ

ПМИТИ

Изобретение относится к запоминающим устройствам. . Известно устройство для контроля оперативной памяти, которое содержит схему пуска, выход которой подключен к регистру числа, счетчику адресов и счетчику циклов, схему сравнения, выход которой соединен со схемой регист рации, подключенной 1с схеме останова, элемент И (1), Это устройство;позволяет контролировать работу оперативного накопителя информации при помощи теста "Дождь", правильность которого определяется визуально с помощью растра на осциллографе ° Такой контроль накопителя в производственных условиях имеет тот недостаток, что в определении правильной работы накопителя по тесту "Дождь" всегда должен участвовать оператор.

Наиболее близким по технической сущности к изобретению является устройство, содержащее схему пуска, регистр числа, счетчик адресов, счетчик, циклов, дешифратор циклов, дополнитет льные счетчики, схему сравнения, схему регистрации, схему останова, коммутатор. разрядов, элемент И (2).

Недостатком этого устройства является невысокая достоверность контроля, так как контроль накопителя осущест= вляется только прямым кодом теста

"Дождь". Это снижает надежность уст-, 5

Цель изобретения — повышение надежности устройства.

Поставленная цель достигается тем, что в устройство для контроля оперативной памяти, содержащее регистр числа, счетчик адресов, счетчик цик . лов, блоки местного управления,.первый счетчик импульсов, дешифратор цик.лов, второй счетчик импульсов, блок регистрации, первый коммутатор, элемент И и схему сравнения, причем выход счетчика адресов подключен к входу счетчика циклов, выходы которого соединены с входами первого счетчика импульсов и дешифратора циклов, вы- . ход которого подключен к первому входу элемента И, входы схемы сравне ния соединены с выходами счетчиков импульсов, а выход подключен к входу блока регистрации, выход которого соединен с входом одного из блоков местного управления, выход которого подключен к одному из входов второго. счетчика импульсов, другой вход которого соединен с выходом элемента И, управляющие входы регистра числа и

1001181 счетчиков соединены с выходом другого блока местного управления, входы первого коммутатора, регистра числа и счетчика адресов являются входами устройства, выходами которого являютest выходы регистра числа и счетчика адресов, введены счетный. триггер, второй коммутатор и элемент НЕ, вход которого подключен к выходу первого коммутатора и первому информационному входу второго коммутатора, а выход, соединен с вторым информационным входом второго коммутатора, управляющие входы которого подключены к выходам счетного триггера, вход которого подключен к выходу первого счетчика им- 15 пульсов, второй вход элемента И соединен с выходом второго коммутатора.

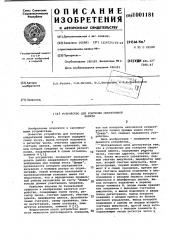

На чертеже приведена функциональная схема устройства для контроля оперативной памяти. 20

Устройство содержит блок 1 местного управления, служащий для пуска устройства, регистр 2 числа, счетчик

3 адресов, счетчик 4 циклов, дешифратор 5 циклов, первый счетчик 6импуль-i сов, второй счетчик 7 импульсов, схему 8 сравнения, блок 9 регистрации, первый коммутатор 10, элемент HE 11, блок 12 местного управления, служащий для останова устройства, второй ком- щ мутатор 13, элемент И 14 и счетный триггер 15. К входам и выходам устройства подключен блок 16 контролируемой оперативной памяти. .Устройство работает следующим об- разом.

Блок 1 совместно с блоком 16, регистром 2 числа, счетчиком 3 адресов обеспечивает получение прямого и инверсного теста "Дождь".

Переполнение счетчика. 3 адресов @ означает прохождение одного малого цикла. Импульсы переполнения счетчика

3 адресов подсчитываются счетчиком 4 циклов. Переполнение счетчика 4 циклов означает прохождение одного боль-45 шого цикла. Импульсы переполнения счетчика 4 циклов подсчитываются счетчиком 6. На время последнего малого цикла в каждом большом цикле дешифратор 5 циклов дает разрешающий сиг- 5О нал на элемент И 14, на который через коммутатор 10 и коммутатор 13 в случае прохождения прямого теста "Дождь", поступают считанные из выбранного разряда единицы. 55

Считанные за время последнего малого цикла единицы подсчитываются .счетчиком 7. Схема 8 сравнения срав нивает два кода — код счетчика 6 и код счетчика 7 после окончания каж- 60 дого большого цикла.

Результат сравнения поступает в блок 9 регистрации, который в случае сравнения вырабатывает команду уста-! новки в ноль, необходимую для дальнейшей правильной работы счетчика 7.

В случае несравнения фиксируется непрохождение теста.

Таким образом, сущность проверки прохождения прямого теста "дождь" заключается в том, что после прохож,цения большого цикла накопитель за-:. полняется таким количеством единиц, которое точно соответствует номеру прошедшего большого цикла. Хранение номера прошедшего большого цикла и подсчет единиц в выбранном разряде блока 16 во время прохождения каждого последнего малого цикла дают возможность судить о правильности прохождения теста, если выполняется равенство количества единиц в разряде после прохождения последнего малого цикла номеру прошедшего большого цикла.

После окончания прямого теста

"Дождь" счетчик 6 оказывается переполненным и импульс переполнения переключает счетный триггер 15, который в свою очередь переключает коммутатор 13. При этом при прохождении инверсного теста "Дождь " из блока 16 будут считываться нули, которые при прохождении коммутатора 10 и элемента НЕ 11 будут преобразованы в единицы. Таким образом, счетчик 7 во время прохождения последнего малого цикла в каждом большом цикле будет подсчитывать количество нулей.

B остальном при прохождении инверсного теста "Дождь" работа предлагаемого устройства не отличается от работы при прохождении прямого теста

"Дождь".

Таким образом, введение в устройство счетного триггера, второго коммутатора и элемента НЕ позволяет существенно повысить достоверность кон троля за счет проверки блока памяти как прямым, так и инверсным кодом типа "Дождь". формула изобретения

Устройство для контроля оперативной памяти, содержащее регистр числа, счетчик адресов, счетчик циклов, блоки местного управления, первый счетчик импульсов, дешифратор циклов, второй счетчик импульсов, блок регистрации, первый коммутатор, элемент И и схему сравнения, причем выход счетчика адресов подключен к входу счетчика циклов, выходы которого соединены с входами первого счетчика импульсов и дешифратора циклов, выход которого подключен к первому входу элемента И, входы схемы сравнения соединены с выходами счетчиков импульсов, а выход подключен к входу блока регистрации, выход которого соединен с входом одного из блоков местного управления, выход которого подключен 1001181

Составитель В.Рудаков

Редактор A.Boðîâè÷ Техред Т,Маточка Корректор В.Бутяга

Заказ 1406/60, Тираж 592 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб.,д.4/5

Филиал ППП "Патент", r. Ужгород, ул.Проектная,4 к одному из входов второго счетчика импульсов, другой вход которого соединен с выходом элемента И, управляющие входы регистра числа и счетчиков соединены с выходом другого блока местного управления, вкодй первого коммутатора, регистра числа и счетчика адресов являются входами устройства, выходами которого являются выходы регистра числа и счетчика адре-. сов, о т л и ч а ю щ е е с я тем, что)о с целью пдвышения надежности устройства, в него введены счетный триггер, второй Коммутатор И элемент НЕ, вход которого подключен к выходу первого коммутатора и первому информационному 15 входу второго коммутатора, а выход соединен с вторым информационным вхо. дом второго коммутатора, управляющие входы которого подключены к выходам счетного триггера, вход которого под; ключен к выходу первого счетчика импульсов, второй вход элемента И соединен с выходом второго коммутатора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 547837, кл. G 11 С 29/00, 1975 °

2. Авторское свидетельство СССР

Р 443414, кл. G 11 С 29/00, 1972 (прототип).