Устройство для контроля оперативной памяти

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОВРЕТЕ»НИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистическик

Республик

<щ1001182 (6!) Дополнительное к авт. свид-ву(22) Заявлено 15.09.81 (2! ) 3337384/18-24

t31)AA NH З

0 11 С 29/00 с присоединением заявки 1о—

Государственный комитет

СССР по делам изобретений и открытий

{23) ПриоритетОпубликовано 2802,83. Бюллетень Мо 8

РЗ) УДК 681. 327 (088.8/

Дата опубликования описания 2 0?83

О В Летнев, !O.C. Шакарьянц, A. . Крий4ЙЬр@-,г! . Резван ю 7-.=:» г ; ";-„""""" -3 у

«»

"" г (72) Авторы изобретения (71) Заявитель

1 54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ОПЕРАТИВНОЙ ПАМЯТИ

Изобретение относится к запоминающигл устройствам.

Известно устройство для контроля оперативной памяти, содержащее схему пуска, регистр числа, счетчик адресов, счетчик циклов, дешифратор цик лов,,два дополнительных счетчика, схему сравнения, схему регистрации, элемент И и схему останова 11;

Недостатком этого .устройства является невысокая достоверность контроля.

Наиболее близким к предлагаемому. по технической сущности является устройство для контроля оперативной памяти, содержащее первый счетчик, регистр числа и блок управления, подключенные к выходным шинам устройства, счетный триггер и формирователь импульсов, элемент И, основные коммутаторы, полусумматор, дополнительные коммутаторы, второй и третий.счетчики 2).

Недостатком данного устройства является невысокая .достоверность конт- . роля, поскольку тест "Дождь" не проверяет взаимовлияния ячеек, в которых записаны разряды одного слова, так как во всех разрядах одного слова записывается одинаковая информация, полнота же проверки взаимовлияния ячеек между разрядами одного слова тестом "Адресный код" не определена.

Цель изобретения - повышение дос-. товерности кбнтроля.

Поставленная цель достигается тем, что в устройство для контроля оперативной памяти, содержащее блок управ-! р ления, регистр числа, элемент И, счетный триггер, формирователь импу". льсов, основные и дополнительные коммутаторы, сумматор по модулю два и счетчики, причем выходы регистра числа и первого счетчика, выход элемен-. та И, и первый. выход блока управления являются выходами устройства, выход элемента И подключен к входу первого счетчика, один из выходов которого

20 соединен с первым и Вторым Входами счетного триггера, выход которого подключен к входу второго счетчика, первым входом сумматора по модулю два и формирователя импульсов, выход которого соединен с инверсным входом, элемента И, второй выход блока управ- ления соединен с,пряным входои элемента И, вторым входом формирователя импульсов, третьим входом счетного триггера .и входом третьего счетчика, один из выходов которого подключен к

1001182 второму входу сумматора по модулю два, выходы основных коммутаторов соединены соответственно с одним из входов регистра числа, другие входы которого подключены к третьему выходу. блока управления, четвертый выход которого соединен с одними из управляющих входов основнЫх коглглутаторов, одни из информационных входов которых подключены соответственно к выходам дополнительных коммутаторов, управляющие и информационные входы которых соединены соответственно с выходами второго и третьего счетчиков, введены регистр сдвига, группа элементов И, группа элементов HJIH и элемент задер- l5 жки, вход которого соединен с выходом сумматора по модулю два, а выход— с первыми входами элементов И группы, первыми входами элементов ИЛИ группы и информационным входом регистра, р{) сдвига, вход синхронизации которого подключен к выходу формирователя импульсов, выходы регистра сдвига соединены с вторыми входами элементов И группы и вторыми входами элементов 75

ИЛИ группы, выходы которых и выходы элементов И группы подключены. соответственно к другим информационным входам основных коммутаторов, другие управляющие входы которых соединены с ЗО одним из выходов второго счетчика..

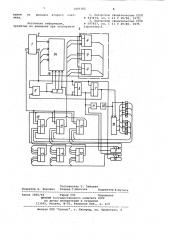

На чертеже изображена функциональная схема предлагаемого устройства.

Устройство содержит блок 1 управления с первым выходом 2, регистр 3 числа, выполненный на триггерах 4, первый счетчик 5, имеющий разрядность . @=Cog< А (где А — количество адресов), счетнйй триггер 6, формирователь 7 импульсов, элемент И 8, второй 9 и третий 10 счетчики, сумматор 11 по модулю два, основные 12 и дополнитель« ные 13 коглмутаторы, контролируемое устройство 14 оперативной памяти, второй выход 15 блока управления, вы-. ход 16 элемента И, четвертый выход 17 45 блока управления и другие управляющие входы 18 основных коммутаторов.

Устройство содержит также регистр

19 сдвига, элемент 20 задержки, группу элементов И 21 и группу элементов 5О

ИЛИ 22, количество которых равно N, где N - количество разрядов проверяемой оперативной памяти.

Устройство работает следующигл образом.

Сигнал с выхода 17 блока 1 обусловливает выбор коммутаторами 12 одного кз двух применяемых в устройстве

Контрольных тестов : "Адресный код"

Или модифицированный "Дождь". При 6О работе устройства в режиме формирова сия теста "Адресный код" в исходном, состоянии все элементы устройства

Обнулены..При этом источником инфорМации, записываемой в регистр 3, являются разряды счетчика 10. При нажа--. тии кнопки "Пуск" в блоке 1 начинает вырабатываться тактовая последовательность импульсов. В первом подцикле на вход регистра 3 подается информация с определенных разрядов счетчика 10.

Счетчик 9 по истечении первого подцикла перебрасывается в следующее состояние сигналом с выхода триггера

6.,В результате этого через коммутаторы 13 на вход регистра 3 поступает информация с других выходов счетчика

10, т. е . происходит перемешивание информации, .записываемой в оперативную память. В каждом последующем под.цикле происходит дальнейшее переключение коммутаторов 13 и дальнейшее перемешивание информации на входе регистра 3. Количество подциклов определяется разрядностью счетчика 9

И количеством управляющих входов коммутаторов 13.

В режиме формирования теста модифицированный "Дождь" после запуска устройства коммутаторы 12 подключают к входу регистра 3 выходы элементов

И 21 либо выходы элементов ИЛИ 22 в зависимости от управляющего импульса на входах 18, поступающего с выхода счетчика 9. В исходном состоянии все элементы устройства обнулены (цепи обнуления не показаны ) и сигнал

"0" на входах 18 коммутаторов 12 подключает к входу регистра 3 выходы элементов Il 21. Блок 1 вырабатывает тактовую последовательность импульсов на выходе 15. В первом подцикле счетчики 5 и 10 работают синхронно от одних и тех же тактовых импульсов блока 1. При этогл на входах сумматора

11 коды — одинаковые, а на его выходе — низкий уровень. По окончании подцикла формирователем 7 выделяется задний фронт импульса с выхода триггера 6 и на элементе И 8 происходит запрет продвижения одного тактового импульса в счетчик 5. В результате второй подцикл в счетчике 5 заканчивается на один такт позже, чем в счетчике 10, и сумматор 11 фиксирует неравнозначность в конце второго подцикла. Импульс "1" с выхода сумматора 11 длительностью в один период тактовой последовательности задерживается элементом 20 задержки также на один период и импульсом с формиро-. вателя 7 записывается в первый разряд регистра 19, в остальных разрядах которого по-прежнему записаны "0".

B этом же подцикле импульсом с выхода формирователя 7 запрещается на элементе И 8 продвижение еще одного импульса тактовой последовательнос- ти к счетчику 5. На первом из элементов И 21 происходит логическое умножение импульсов "1", поступающих с выходов элемента 20 задержки и с

1001182 первого разряда регистра 19, а через коммутаторы 12 в регистр 3 записывается "1" s первый разряд-и "0"

:во все остальные.

Соответственно неравнозначность фиксируется в двух последних адресах третьего подцикла. Задержанный на один период импульс "1" с выхода сумматора 11 длительностью уже в два периода тактовой последовательности через элемент 20 задержки поступает на входы элементов И 21. Поскольку в первом разряде регистра 19 была .записана "1" еще во втором подцикле, то. в предпоследнем .адресе в региСтр

3 записывается "1",в первый разряд 15 и "0" — в остальные, В последнем адресе импульс с формирователя 7 переписывает "1" во второй разряд регистра 19,:записав также "1 и в первый. его разряд. Следовательно,- в gg последнем адресе через элементы И 21 и коммутаторы 12 записывается "1" в первый и второй разряды регистра

3. Возникает сдвиг запиеи "1" на один адрес между соседними разрядами д . записываемых чисел (так называемая

"ступенька"). Аналогично в четвертом подцикле в последнем адресе записывается "1" уже в три младших разряда регистра 3 и т. д. Таким образому оперативная память; заполненная в первом подцикле всеми нулями (начиная с последнего адреса), постепенно заполняется в следующих подциклах единицами. Происходит процесс

"набегания" единиц (характерный для 35 теста "Дождь"1 для каждого разряда оперативной памяти, однако это заполнение происходит со сдвигом на один адрес для соседних разрядов.

Для совокупности всех разрядов one- 40 ративной.памяти происходит процесс

"набегания лестницы". Таким образом„ тест типа "Дождь" преобразуется в, модифицированный "Дождь", позволяю- щий проверять .взаимовлияние соседних разрядов записываемых чисел, что повьиаает достоверность .контроля опе-. ративной памяти..

Когда пройдет A подциклов, коды на входе сумматора 11 будут инверсными. Первый разряд оперативной памяти заполняется "1" в(A-1) -м адресе, второй — в (А-2)-м адресе, третий -в (A-3)-м адресе и т. д. Счетчик 9 подключает через коммутаторы

12 к входу регистра 3 выходы элементов ИЛИ 2. В следукщие А подциклов код единиц сменяется кодом нулей.

Однако из-эа наличия регистра 19 сдвига и элемента 20 задержки в пер- 66 вый разряд оперативнЬй памяти записывается "0" в t A+2) -м адресе, во второй - в (А+3) -м адресе и т. д.

Полная проверка оперативной памяти происходит за (2А+И+1) подциклов. у

Технико-экономическое преимущество. предлагаемого устройства заключается в его более высокой по сравнению с прототипом достоверности контроля оперативной памяти.

Формула изобретения

Устройство для контроля оперативной памяти, содержащее блой управления, регистр числа, элемент И, . счетный триггер, формирователь им-. пульсов, основные и дополнительные коммутаторы, сумматор по модулю два и счетчики, причем выходы регистра числа и первого счетчика, выход элемента И и первый выход блока управления являются выходами устройства, выход элемента И подключен к входу первого счетчика, один из выходов

1 которого соединен с первым и вторым входами счетного триггера, выход которого подключен к входу второго счетчика, первым входом сумматора по модулю два и формирователя импульсов, выход которого соединен с инверсным входом элемента И, второй выход бло" ка управления соединен с прямым входом элемента И, вторым входом формирователя импульсов, третьим входом счетного триггера и входом третьего счетчика, один из выходов которого подключен к второму входу сумматора по модулю два, выходы основных коммутаторов соединены соответственно с одними из входов регистра числа, другие входы которого подключены к третьему выходу блока управления, четвертый выход которого соединен с одними из управляющих входов основных коммутаторов, одни из информационных входов которых подключены соответственно к выходам дополнительных коммутаторов, управляющие и информационные входы которых соединены соответственно с выходами второго и третьего счетчиков, о т л и чаа ющ е е с я тем, что, с целью повышения достоверности контроля, в не"

ro введены регистр сдвига, группа элементов И, группа элементов ИЛИ и элемент задержки, вход. которого соединен с выходвм сумматора по модулю два, а выход — с первыми входами элементов И группы, первыми входами элементов ИЛИ группы и информационным входом регистра сдвига, вход синхронизации которого подключен к выходу формирователя импульсов, выходы регистра сдвига соединены с вторыми входами элементов И группы и вторыми входами элементов ИЛИ группы,-выходы которых и,выходы элементов И группы подключены соответственно к другим информационным входам основных коммутаторов, другие управляющие входы которых соединены с

1001182

Составитель T. Зайцева

Редактор A. Ворович Техред Т.Маточка Корректор В.Бутяга

Заказ 1406/60 Тираж 592 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 одним из выходов второго счетчика.

И сточ ни ки и н формации, принятые во внимание при экспертизе

1 . Авторское

Р 443414, кл. 6

2. Авторское, Р 547837, кл. ( (прототип ).

5 свидетельство СССР

11 С 29/00, 1972. свидетельство СССР

11 С 29/00, 1975