Периферийный процессор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Х АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистинеских

Респуолик и 1003093 (61) Дополнительное к авт. саид-ву (22) Заявлено 04.1181 (21) 3346702/18-24 с присоединением заявки ¹ (23) Приоритет

Р )М g+ з

G Об Р 15/ОО

Государственный комитет

СССР по делам нзобретеннй н открытий

f 53) УДК 681. 3 (088. 8), Опубликовано 07.0383. Бюллетень № 9

Дата опубликования описания 07.0383 к w, . .«В(, Р" а 7

«т; р „ с

Р.К. Русидзе и В.Г. Чача т(Ье Р,с-

Тбилисский научно-исследОвате кий Ййатнтут приборостроения н средств автоиативаЪиви„Ордена /

Ленина институт проблем управления (72) Авторы изобретения (71) Заявители (54) ПЕРИФЕРИЙНИЙ ПРОЦЕССОР изобретение относится к автоМатике и вычислительной технике и пред назначено для управления локальными объектами в качестве встроенного вычислителя в автоматических системах управления технологическими процессами для первичной обработки и передачи информации, а также для управления периферийным оборудованием.

Известно устройство, содержащее арифметико-логический блок, блок оперативной памяти, блок постоянной памяти программ, счетчик команд, а также регистры и генератор (1)«

Недостатком известного устройства является низкая надежность, обусловленная отсутствием контроля правильности передачи информации по каналам связи.между блоками устройства.

Наиболее близким к изобретению по технической сущности является процессор, содержащий арифметический бл к, три регистра, генератор, память команд, дешифратор команд, регистр команд, память программ, счетчик команд, блок ввода-вывода, опе-. ративная память, пульт управления, формирователь макрокоманд и блок контроля (2).

К недостаткам известного устройства относится низкое быстродействие и надежность, обусловленные большйм временем формирования макрокоманд, громоздкостью управления арифметическим блоком и отсутствием контроля правильности обмена информации между блоками устройства.

Целью изобретения является повышение быстродействия и надежности.

Указанная цель достигается за счет того, что в периферийный процессор, содержащий память программ, выход которой соединен с первьм входом регистра команд, память команд и формирователь макрокоманд, .выходы которых соединены соответственно с первым и вторык управляющими входами арифме20,òè÷åñêîãî блока, третий управляющий вход которого соединен с выходом ге;ератора, и входом распределителя, блок контроля, выход которого соединен с первым. входом пульта управления и входом блока ввода-вывода, первый выход которого соединен с вторым входом пульта управления, счетчик команд, дешифратор команд, три регистра, оперативную память, введены блок прерывания, два элемента ИЛИ, элемент ИЛИ-НЕ, элемент И, причем

1003093 рым нходом памяти команд, выход памя- 5 ти программ соединен с входом форми10 и четвертый выходы которого соединены с первыми входами соответствейно 2О первого и второго элементов ИЛИ, вы"

ЗО

З

4О

45 ра снимается с блока 1 и последовательно, по разрядам, подается на регистр 4. Генератор 5 служит для выработки тактовых импульсов. Б памя-6О ти б записаны коды настройки блока 1 на схемную реализацию операторов. памяти б. Регистр 8 является буфернымб5 первый выход счетчика команд соединен с вторым входом регистра команд, первым входом памяти команд и входом дешифратора команд, через который выход регистра команд соединен с вторователя макрокоманд и первым входом счетчика команд, вторые выход и вход соединены соответственно с входом памяти программ и выходом элемента

И, входы которого соединены с первым выходом арифметического блока и вы-. ходом элемента ИЛИ-НЕ, входы которого соединены с выходом пульта управления и выходом блока прерывания, входы которого соединены с вторым выходом арифметического блока и вторым выходом блока ввода — нывода, третий ходы которых через первый и второй регистры соединены с четвертым и пятым входами арифметического блока, третий выход которого соединен через третий регистр с входом блока контро ля, первый выход блока ввода — вывода соединен с первым входом.оперативной памяти, выходы которой соединены с вторыми входами первого и второго элементов ИЛИ, выход блока контроля соединен с вторым входом оперативной памяти, выход распределителя соединен с шестым входом арифметического блОка.

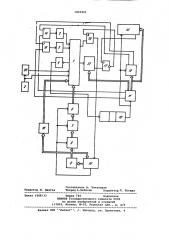

На чертеже приведена блок-схема устройстна.

Устройство содержит арифметический блок 1, регистры 2-4, генератор

5, память б команд, дешифратор 7 ко" манд, регистр 8 команд, память 9 программ, счетчик 1 0 команд, блок 11 внода — вывода, оперативная память

12, пульт 13 управления, элементы

ИЛИ 14 и 15, формирователь. 16 макрокоманд, элемент ИЛИ-НЕ 17, элемент

И 18, блок 19 контроля, распределитель 20 и блок 21 прерывания.

Процессор работает следующим образом.

Арифметический блок 1 предназначен для схемной реализации арифметических и логических операторон алгоритма управления объектом. Регистры

2 и 3 осуществляют последовательную подачу операндов на арифметический блок 1. Результат вычисления оператоДешифратор 7 служит для дешифрации и выборки кодов настройки блока 1 иэ устройством|между памятью 9 программ и дешифратором 7, Память 9 служит для хранения потребительских и управляющих программ и сохраняет информацию при аварийном отключении питания.

Счетчик 10 осуществляет как поОчередную ныборку команд иэ памяти 9, так и условные и безуслонные переходы н алгоритме управления объектом. Блок

11 представляет. собой набор периферийных устройств, осуществляемых двусторонную связь с объектом управления. Память 12 предназначена для хранения промежуточных результатов вычисления, и потребительских констант. Пульт 13 предназначен для работы оператора. формирователь 16 осуществляет идентификацию одного конкретного оператора согласно программе из объединенных нескольких операторов, имеющих общий код настройки блока 1. Блок 19 реализует контроль на четность результатов вычислений, подаваемых с регистра 4 через блок

11 на объект управления. Блок 21 осу25 ществляет аварийное прерывание вычис-. ления алгоритмов от объекта с восста-. новлением .предыдущего состояния про . цессора. Распределитель 20 вырабатывает пачки шестнадцатиразрядных единичных логических уровней для конвейерной обработки информации в блоке 1. Потребительская программа находится в памяти 9, обработка которой осуществляется при помощи счетчика 10. При обработке очередной команды счетчик 10 по адресным входам выбирает код укаэанной команды из памяти

9Ä При отсутствии в команде признаков условного и безусловного переходов код команды заносится в регистр 8.

Далее указанный код дешифрируется дешифратором. 7,результат дешифрации иэ которого с выхода счетчика 10 подается на память б, откуда вырабатывается код настройки блока 1 на схемную реализацию оператора, соответствующего обрабатываемой команде. В случае, если блок 1 настраивается на реализацию составного оператора, например оператора сложения — вычитания, при

БО помощи формирователя 16 по информации

Ф подаваемой из памяти 9 программы осуществляется идентификация одного оператора, например оператора сложения.

Если в обрабатываемой 1команде содержится условие безусловного перехода, оно заносится н счетчик 10. Обрабатываемые операнды иэ блока 11 пода-. ются на блок 1 либо. через память 12, либо в режиме прямого -доступа непосредстненно через элементы ИЛИ 14 и

15 и регистры:2 и 3. Результаты вычисления, снимаемые с блока 1, через регистр .4 поступают на. блок 19. После контроля результата он подается через блок 11 на объект и на пульт

1003093

Формула изобретения

Периферийный процессор, содержащий память программ, выход которой. соединен с первым входом .регистра ко-. манд, память команд .и формирователь .. макрокоманд, выходы которых.соедине- 35 ны соответственно с первым и вторым управляющими входами арифметического блока, третий управляющий вход которого соединен с выходом генератора, и входом распределителя, блок контро-4п ля,выход которого соединен с первым входом пульта управления и входом блока ввода — вывода, первый выход которого соединен с вторым входом пульта управления,. счетчик команд, дешифратор команд, три регистра, оперативную память, о т л и ч а ю30

l3. Если результат промежуточный, он подается в память 12 и по желанию оператора — на пульт 13. Пульт 13 осуществляет индикацию вводимой из объекта информации через блок ll, а также результатов вычисления с блока

19 и вырабатывает условия прерывания и остановки, сформированные оператором. В блоке 21 по информационным входам блока 11 подаются условия прерывания от объекта, а также сигналы l6 переполнения с выхода блока 1. При выработке сигнала прерывания через элемент ИЛИ-HE 17 блокируются элемент И 18 и счетчик 10. Выработанные распределителем 20 шестнадцатиразряд-15 ные единичные логические уровни осуществляют разделение обрабатываемых операндов в конвейере, а также служат для выработки сигналов управления вычислениями в блоке 1. 20

Таким образом, введение в периферийный процессор новых блоков и их связей позволяет значительно упростить его управление, повышая тем самым быстродействие и надежность пред-75 лагаемого устройства по сравнению с известными. шийся тем, что, с целью и эвыаения его быстродействия и надежности, в него введены блок прерывания, два

Элемента ИЛИ, элемент ИЛИ-НЕ, элемент И, причем первый выход счетчика команд соединен с вторым входом регистра команд, первым входом памяти команд и входом дешифратора команд, через который выход регистра команд соединен с вторым входом памяти команд, выход памяти программ соединен с входом формирователя макрокоманд и первым входом счетчика команд, вторые выход и вход соединены соответственно с вх4дом памяти программ и выходом элемента И, входы которого соединены с первым выходом арифметического блока и выходом элемента

ИЛИ-НЕ, входы которого соединены с выходом пульта управления и выхоqoM блока прерывания, входы которого соединены с вторым выходом арифметического блока и вторыми выходом блока ввода — вывода, третий и четвертый выходы которого соедине IH с первыми входами соответственно первого и второго элементов ИЛИ, выходы которых через первый и второй регистры соединены с четвертью и пятым входами арифметического блока, третий выход которого соединен через третий регистр с входом блока контроля, первый выход блока ввода — вывода соединен с первым входом, оперативной памяти, выходы которой соединены с вторйми входами первого и второго элементов ИЛИ, выход блока контроля соединен с вторым входом оперативной памяти, выход распределителя соединен с шестым входом арифметического блока.

Ис точник и информации „ принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 741269, кл. G Об F 15/ОО, 1978.

2 ° Авторское свидетельство СССР

9 525099, кл. G Об F 15/ОО, 1975(прототип) °

1003093

Составитель В. Чачанидэе

Техред A. Ба бин ец Корректор JI. Бокшан

Редан тор .Н. Джуга н

Закаэ 1568/33

Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, А/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4