Цифровой функциональный преобразователь

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 160781 (21) 3318122/18-24 151) М. КП.З с присоединением заявки ¹ (23) Приоритет

G 06 Р 15/31

Государственный кэмитет

СССР по делам изобретений и открытий (53) УДК 681. 325 (088. 8) Опубликовано 07.0383. Бюллетень № . 9

Дата опубликования описания 07,0383

М. Ф. Билык, В, Б. Дудыкевич / и 3. М. Стриле сий к,, „, „

4, l. 8 а.

С /

Львовский ордена Ленина полийехниуеский -ттйфтиту им. Ленинского комсемщта - ".

l (72) Авторы изобретения (71) Заявитель (54) ЦИФРОВОЙ ФУНКЦИОНАЛЬНОЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к автоматике и вычислительной технике и может. быть использовано в системах автоматического управления и контроля, цифровых линеаризирующих устройствах, устройствах аппаратной реализации средств . математического обеспечения ЭЦВМ и др °

Известно устройство вычисления логарифмической функции, содержащее двоичный счетчик, первый и второй сумматоры, пересчетную схему, две группы элементов И и элемент задержки (1).

l5

Однако в указанном устройстве результат вычисления представляет собой сумму членов разложения в ряд логарифмической функции, что в значительной степени влияет иа аппаратурные затраты. Большая зависимость аппаратурных затрат от количества членов ряда является недостатком устройства.

Наиболее близким к изобретению

;по технической .сущности является

Функциональный преобразователь, содержащий входной делитель частоты, выходной счетчик, схемы И первой, второй и третьей групп, схемы ИЛИ, ключи, элементы задержки, цифровой фильтр, управляющие знаковые входы (2) .

Недостатками известного устройства являются ограниченные функциональные возможности, так как он воспроизводит только функция вида " а (Сб a+x где а - постоянный коэфа-х фициент,.х — входная переменная, и не может воспроизводить логарифлические функции, а также пониженное быстродействие., обусловленное наличием двух элементов задержки, участвующих в работе устройства при вычислении обеих воспроизводимых. устройством функций.

Целью изобретения является расширение функциональных воэможностей и повышение быстродействия.

Поставленная цель достигается тем, что в преобразователь, содержащий счетчик, дополнительно введены первый и второй двоичные .умножители, первый и второй сумматоры-вычитатели, причем первый и второй входы первого сумматора-вычитателя соединены соответственно с выходом первого двоичного умножителя и входом преобразователя, подключенного к входу счетчика, 1003094 установочные входы первого и второго двоичных умножителей соединены с информационными выходами счетчика, информационные входы первого и второго двоичных умножителей соединены соответственно с выходами первого и вто« рого сумматоров-вычитателей, первый и второй входы второго сумматора-вычитателя подключены к выходам. соответственно первого сумматора-нычита,теля и второго двоичного умножителя, ()

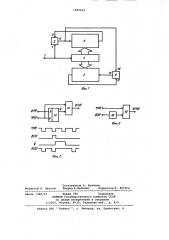

На фиг. 1 представлена структурная схема цифрового функционального преобразователя; на фиг. 2 — вариант выполнения схемы вычитания сумматора- )5 вычитателя (СВ) и временные диаграммы, поясняющие ее работу на фиг.3 вариант выполнения хемы сложения (СС) сумматора- ычитателя.

Преобразователь (фиг.l) содержит вход 1, двоичные умножители 2 и 3, счетчик 4, сумматоры-вычитатели 5 и

6, входы 7 и 0 и выход 9 сумматоравычитателя 5, входы 1 0 и 11 и выход

12 сумматора-вычитателя 6. Схема вычитания импульсных последовательностей (фиг. 2) содержит D-триггер

13 и элемент ИЛИ 14..Схема сложения импульсных последовательностей (фиг 3) содержит элемент ИЛИ 15 и элемент задержки 16.

При конкретном конструктивном выполнении преобразователя в качестве двоичных умножителей 2 и 3 целесообразно применять выпускаемую отечественной промышленностью микросхему

К155 ИЕ8.В качестве счетчика 4 можно применить микро схемы К155ИЕ5, К133ИЕ5, К133ИЕ7. Схема вычитания и схема сложения, варианты выполнения которых представлены на фиг. 2 и 3, Tàêæå 49 без трудностей строятся на элементах

155 серии.

Работа схемы вычитания подробно проиллюстрирована временными диаграм мами (фиг.2). Элемент задержки 16 в схеме сложения (фиг. 3) исключает возможность совпадения импульсов импульсных последовательностей, поступающих на входы схемы.

Преобразователь работает следующим образом.

Пусть сумматоры-вычитатели 5 и 6 работают в режиме вычитания импульсных последовательностей.

На вход 1 преобразователя поступа- ет входная импульсная последовательность, формирующая текущее значение числа х в счетчике 4. Эта же импульс ная последовательность, поступая на вход 7, вызывает появление на ее выходе. импульсной последовательности

2, которая поступает на.вход двоич ного умножителя 2, вызывая появление на выходе импульсов последовательностй у, поступающей I на вход сумматора-вычитателя 5. Импульсы последовательности Е.(поступают также на вход 10 сумматора-вычитателя 6, вызывая появление на ее выходе импульсов последовательности Z . Импульсная последовательность Z, поступающая на вход двоичного умножителя 3, вызывает появление на его выходе импульсной последОвательности у, поступающей на вход сумматора-вычитателя 6, Работа сумматора-вычитателя 5 описывается уравнением

Éz =сЬ-Й (a) где d2. — приращения импульсной последовательности Е„ на вы ходе сумматора-вычитателя

5„ :

dx . — приращения импульсной последовательности х на входе

7 сумматора-вычитателя 5)

dy — приращения импульсной пос

1 ледовательности, у на вхо-" де В сумматора-вычитателя 5.

Значение dy< определяем из уравне ния, описывающего работу двоичного умножителя 2

dl„=X (2. } где х — текущее значение числа в счетчике 4; .d — коэффициент пересчета счетчика двоичного умножителя 2 (в дальнейшем и двоичного умножителя.3) .

Тогда

dz éx-х откуда

dz1 О

dx (4}

Работа сумматора-вычитателя 6 описывается уравнением

Йг = dZ„- Йу, (5) где ЙŠ— йриращения импульсной пос ледовательности Е на выходе 12 сумматора-вычитателя 6;

Йу — приращения импульсной последовательности у на вхо, де 11 сумматора-вычитателя 6.

Значение Йу определяем из уравнения, описывающего работу двоичного умножителя 3

Тогда Учитывая уравнения (4), (5), (6) д =а - -Х " С7}

1003094 ох о- а известный — только функции о х откуда, после элементарных преобраз ваний — (8) аЧХ (a+x)

Приращения dZ> интегрируются счет- 5 чиком двоичного умножителя 3, в котором формируется результат преобразования Х

2 -l = — (9) (a+x) а+ х

Аналогично импульсная последовательность ЙЕ интегрируется счетчи4 ком двоичного умножителя 2, в котором формируется второй результат преобразования:

10!

Следовательно, в рассмотренном режиме работы преобразователя он воспроизводит две Функции:

z,=оСи{«.— "), («)

О-Х

2 = р Х (12-)

В данном случае, т. е. при воспроизведении функций (11) и (12), блоки преобразователя не содержат элементов задержки. Поэтому быстродействие преобразователя при воспроизведении ,этих функций выше, чем у известного .устройства.

Вывод формул всех режимов работы пРеобРазователя аналогичен рассмотренному) поэтому пРиведем сразу.оконча- 35 тельные формулы. Для случая, когда сумматор-вычитатель 5 работает в режиме вычитания, а сумматор-вычитатель б в режиме сложения импульсных последовательностей 40

Формула изобретения

22- - - Ги — (4 ъ)

С(О+Х а-Х

Выраженйе для Е„ не изменилось, т.е. описывается Формулой (11).

Для случая, когда оба сумматоравычитателя 5 и б работают .в режиме сложения импульсных последовательностей

2„=С) Ри аХ

21=а Х

Технические преимущества предлагаемого преобразователя по сравнению 55 с известным заключаются в том, что предлагаемый преобразователь обладает расширенными функциональными возможностями, так как воспроизвоцит следующие функции:

Z= а, < —. 2= О 2=аМ(+ 1 а х Ох -.1 ау(Z=-ч - <и „„) 2=а и „„

1. Введение в кибернетическую . технику. Под .Ред. Б.Н. Калиновского.

60 Киев, Наукова думка, 1979, с. 169-171.

2. Авторское свидетельство СССР

Р 415665, кл. G Об Р 15/31, 1974 (прототип). х dx / Хъ

z = Ja =a(aj4+ — (1о) а+х 1 a ) и Z = i а также обладает повышена x а-х ныл быстродействием при вычисле нии а ° х функции Z. =----- эа счет исключения а+х из его состава элементов задержки.

Это подтверждается тем, что двоичные умножители 2 и 3, счетчик 4 и схема вычитания сумматоров-вычитателей построены без применения элементов задержки.

Таким обра=ом, технико-экономический эффект от внедрения изобретения будет получен эа счет расширенных, по сравнению с известии(устройством, функциональных возможностей преобразователя и повышения его быстродействия.

Цифровой функциональный преобразователь, содержащий счетчик, о т л и ч а ю шийся тем, что, с целью расширения области его применения путем дополнительного вычисления функций

2=cg81 а)) 2д= и а, 2=ОЬ „„ и повышения быстродействия преобразователя, в-него введены первый и второй двоичные умножители, первый и второй сумматоры-вычитатели, причем первый и второй входы первого сумматора-вычитателя соединены соответственно с выходом первого двоичного умножителя и входом преобразователя, подключенного к входу, счетчика, установочные входы первого и второго . двоичных умножителей соединены с информационными выходами счетчика, информационные входы первого и второго двоичных умножителей соединены сс тветственно с выходами. первого и второго сумматоров-вычитателей, первый и второй входы второго сумматора-вычи- тателя подключены к выходам соответственно сумматора-вычитателя и второго двоичного умножителя.

Источники информации, принятые во.внимание при экспертизе

10030 И

Фи. / фф

Фиа У

7/lф

Редактор Н. Джуган

Эакаэ 1568/33 филиал ППП Патент, г, Ужгород, ул. Проектная, 4

УФ) 7Щ

Р®

Составитель й. Шуляпов

Техред А.Бабинец Корректор В. Бутяга

Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР.по делам изобретений.и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5