Устройство для моделирования негауссовых помех

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (щ3003112 (61) Дополнительное к авт. свид-ву— (22) Заявлеио02.11.81 (21) 3349975/18-24 с присоединением заявки Нов (23) Приоритет

Опубликовано 07.03Я3. Бюллетень М 9

Дата опубликования описания .р3.83.Р М К, э

G G 7/48

Государственный комитет

СССР ио делам изобретений и открытий (53) УДК 681. 3

Loss.8) /

3м4

В.С.Попенко, Н.И.Кудряшов, Г.А/.Пономарев и С.НЩаблий т (72) Авторы изобретения (71) Заявитель (54 ) УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ НЕГАУССОВЫХ ПОМЕХ

Изобретение относится к аналоговой вычислительной технике и может быть использовано для моделирования функции помех, описываемой произведением полной гамма-и степенной с целым отрицательным показателем функций.

Известно устройство для моделирования разрывных функций, содержащее сумматоры, преобразователи аналог-код, дешифраторы, инвертор, коммутаторы Й группы ключей, коммутирующих резисторы С13.

Известно устройство для воспроизведения полинома Лагерра,I содержащее три интегратора, два блока перемножения, сумматор и инвертор Г 2з.

Эти устройства не могут быть использованы для моделирования воздействия негауссовой помехи °

Наиболее близким по технической сущности .к предлагаемому является устройство для моделирования полинома

Лагерра, содержащее первый интегратор, вход которого является входом устройства,:а выход соединен с первым входом первого блока умножения, выход которого подключен к первому входу сумматора, выход которого соединен с вторым входом первого блока умножения и с входом второго интегратора, выход которого через инвертор подключен к первому входу второго блока умножения, выход которого соединен с вторым входом сумматора, и

5 к входу третьего интегратора, выход которого является выходом устройства и соединен с третьим входом сумматора t33.

Однако данное устройство не обес10 печивает воспроизведения функции, позволяющей моделировать негауссовую помеху вида произведения полной гаммафункции и степенной с целым отрицательным показателем.функций и является достаточно сложным.

Цель изобретения — упрощение устройства при моделировании негауссовой помехи типа произведения полной гамма- и степенной с целым отрицательным показателем функций.

Эта цель достигается тем, что в устройство, содержащее три интегратора, сумматор, инвертор и два блока умножения, вход первого интегратора является входом устройства, а выход соединен с первым входом первого блока умножения, выход которого подключен к первому входу сумматора, выход которого соединен с вторым входом первого блока умножения и со входом второго интегратора, выход ко1003112

Формула изобретения торого подключен ко входу третьего интегратора, а через инвертор — к первому входу второго блока умножения, выход которого соединен с вторым входом сумматора, выход третьего интегратора является выходом устройства 5 и соединен с третьим входом сумматора, дополнительно введен четвертый инте-. гратор, выход которого подключен к второму входу второго блока умножения, а вход соединен с входом пер- 10 вого интегратора.

В основу работы устройства положено цифференциальное уравнение вида

<3(t)+ j(t) (a+ Ф,+1)+ ц у (t) =0, имеющие решение в виде функции 15

М(Ф,)"- Г(сю) at используемой для моделирования негауссовой помехи.

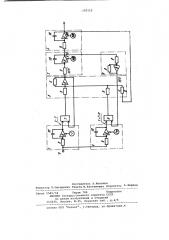

На чертеже представлена функциональная схема предлагаемого устройства.

Устройство содержит первый, второй, третий и четвертый интеграторы 1-4, сумматор 5, инвертор 6, первый и второй блоки 7 и 8 умножения, резисторы 9 и конденсаторы 10.

Устройство работает следующим образом.

В начале формирования вводятся начальные условия: в интегратор 1 -. (-,1}, в интегратор 4 - (1+a),â интеграторы

2 и 3 соответственно — (-у(0) =О, у (О> =0

При включении питания постоянное напряжение -U подается одновременно на выходы интеграторов 1 и 4, которые преобразуют его соответственно в сигналы, описываемые функциями (t -1) и (t +1+а). Сигнал, описываемый функцией (t -1, с выхода интегратора

1 подается на первый вход блока 7 40 уг ножения, на выходе которого формируется сигнал (3 (4) (4 -1Ц, а сигнал (4+1+a) с выхода интегратора 4 подается на второй вход блока 8 умножения,на выходе которого формируется 45 сигнал (Э (Ц(1+1+А) . Сигналы с выходов блоков 7 и 8, описываемые функциями (ЗН) (-1) и t (t) (+1+а)), подаются соответственно на первый и второй входы сумматора 5, на третий вход которого подается колебание с выхода итегратора 3, описываемое функцией f3(t)) при этом на выходе сумматора 5 формируется сигнал fg(t)), который подается одновременно на второй вход блока 7 умножения и на вход интегратора 2, с выхода которого снимается сигнал (-i(t)), который подается через инвертор 6 на первый вход блока 8 умножения и на вход интегра тора 3, на выходе которого формируется колебание, описываемое требуемой функцией f J(t)j

Использование предлагаемого изобретения.позволяет провести выбор оптимальных схем приемных устройств, что обеспечивает повышение помехоустойчивости и качества связи в каналах с негауссовой помехой.

По сравнению с известным предлагаемое устройство имеет в два раза меньше элементов различного типа, что приводит к упрощению конструкции и повышению надежности.

Устройство для моделирования негауссовых помех, содержащее три интегратора, сумматор, инвертор и два блока умножения, пичем вход первого интегратора является входом устройства, а выход соединен с первым входом первого блока умножения, выход которого подключен к первому входу сумматора, выход которого соединен с вторым входом первого блока умножения и с входом второго интегратора, выход которого подключен к входу третьего интегратора, а через инвертор к первому входу второго блока умножения, выход которого соединен с вторым входом сумматора, выход третьего интегратора является выходом устройства и соединен с третьим входом сумматора, о тл и ч а ю щ е е с я тем, что, с целью упрощения устройства при моделировании негауссовой помехи типа произведения полной гамма- и степенной с целым отрицательным показателем функций, оно содержит четвертый интегратор, выход которого подключен к второму входу второго блока умножения, а вход соединен с входом первого интегратора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 525125, кл. Q. 06 G, 7/48, 1977.

2. Авторское свидетельство СССР по заявке Р 2700149/18-24, кл. G 06 7/40, 1977.

3. Аналоговая и аналого-цифровая вычислительная техника. Под ред.

В.И.Ушакова, М., Сов.радио, вып. 1, 1968, с. 138 (прототип ).

03112

Составитель B.Фукалов

Редактор П.Иакаревич Техреду Ж.Кастелевич Корректор ". Ференц

Заказ 1565/34 Тираж 704 . Подписное

ИНИИПИ 1осударственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", r.Óæroðîä, ул.Проектная,4