Устройство для контроля информации, записываемой в оперативную память

Иллюстрации

Показать всеРеферат

Союз Советскнк

Соцмалистическик

Республик (>

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22)Заявлено 01.10.81 (21) 3342352/18-24 с присоединением заявки М(23) Приоритет—

Опубликовано 07.03.83. Бюллетень JA 9

Дата опубликования описания 07.03.83

Ф (51)M. Кл.

G 11 С 29/00

Йкударствелвы» квмктет

СССР аф илам кзабретеккк и втерытик (53) УДК 681. 327 (088.8) (72) Автор изобретения

f г

""!

1 т

А. П. Малышев (7l) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИНФОРМАЦИИ, ЗАПИСЫВАЕМОЙ В ОПЕРАТИВНУЮ ПАМЯТЬ

Изобретение относится к запоминающим устройствам и может быть использовано в устройствах отладки программ для отображения содержимого памяти.

Известно устройство для контроля информации, записываемой в оперативную память, содержащее регистры, схему сравнения, блок уп- равления и буферную память (1) .

Недостатком этого устройства является наличие буферной памяти.

Из известных устройств наиболее близким техническим решением к предлагаемому является устройство для контроля информации, записываемой в оперативную память, содержащее шины адреса и данных, .блок ручной yc"" тановки адреса, схему совпадения, регистр временного хранения данных, элементы схемы синхронизации, и блок индикации, на который выводится содержимое ячейки памяти, адрес которой содержится в блоке ручной установки.адреса (21.

Недостатком этого устройства является невозможность контролировать и выводить на индикацию содержимое нескольких ячеек памяти с различными адресами, что сужает область его применения.

Цель изобретения - расширение области применения устройства за счет обеспечения контроля информации, записанной по нескольким адресам.

Поставленная цель достигается тем что в устройство для контроля информации, записываемой в оперативную память, содержащее блок ввода адресов, буферный регистр, вход которого является информационным входом устройства, элемент И, первый вход которого является тактовым входом устройства, и блок индикации, одни из входов которого соединены с одними из выходов блока ввода адресов, введены схема сравнения, первый коммутатор и сум3 1 матор по модулю два, один из входов которого является адресным входом устройства, другие входы подключены к одним из выходов блока ввода адресов, а выходы - к одним из входов схемы сравнения, другие входы которой соединены с другими выходами блока ввода адресов, а один из выходов подключен к второму входу элемента И, выход которого соединен с первым входом первого коммутатора, второй и третий входы которого подключены соответственно к другому выходу схемы сравнения и к выходу буферного .регистра, а выход соединен с другим входом блока индикации.

Блок ввода адресов содержит регистр начального адреса, регистр количества адресов, датчик адресов, ключ и второй коммутатор, входы которого соединены соответст венно с выходом датчика адресов и .с выходом ключа, а, выходы - соответственно с входами регистра начального адреса и с входами регистра количества адресов, выходы регистра начального адреса и регистра количества адресов являются выходами блока.

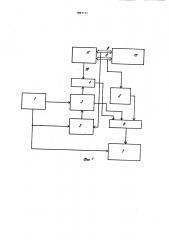

На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 - функциональная схема предпочтительного варианта выполнения блока ввода адресов.

Устройство содержит (фиг.1) блок ! ввода адресов, предназначенный для ручной установки адреса, сумматор 2 по модулю два,схему 3 сравнения,, элемент И 4, буферный регистр 5, первый коммутатор 6 и блок 7 индикации.

На фиг. 1 показаны шина 8 данных, адресная шина 9, тактовый вход 10 устройства, процессор 11 и контролируемая оперативная память (ОЗУ) 12.

Блок ввода адресов содержит(фиг.2) датчик 13 адресов, выполненный в виде наборного поля, ключ 14, второй коммутатор 15, регистр 16 начального адреса и регистр 17 количества адресов.

Блок 7 индикации состоит иэ одинаковых частей, количество которых определяется максимальным размером отображаемого массива. Каждая часть представляет собой регистр хранения данных, записываемых в одну иэ ячеек массива, связанный поразрядно с усилителями блока 7 индикации, к выходам которых подключены светодиоды.

003149 ф ь-/u(> О, S

fS о

25 зо

4S

И, Размер массива и разрядность слова, записываемого в ячейку ОЗУ 12, опре деляют необходимое число элементов в коммутаторе 6 и блоке 7 индикации.

Предлагаемое устройство работает следующим образом.

На наборном поле датчика 13 (фиг.2) устанавливается начальный адрес массива ячеек ОЗУ 12, предназначенного для отображения на блоке 7 индикации.

Значение начального адреса через коммутатор 15 записывается в регистр

16, а также поступает в блок 7 для отображения. Ключ 14 из положения

"Начальный адрес" устанавливается в положение "Размер массива", при этом выход датчика 13, на котором набирается размер массива отображения, коммутатором 15 подключается к входу регистра 17 для записи размера отображаемого массива. Каждый байт, передаваемый flo шине Я (см.фиг.1),от процессора 11 к ОЗУ 12, записывается в регистр 5, а на сумматор 2 поступает текущий адрес ячейки ОЗУ 12 в которую производится запись. ".умматор 2 определяет разность между начальным и текущим адресом и если она меньше нуля, то с выхода сумматора 2 результат вычитания(И) параллельным кодом, беэ знакового разряда, поступает на вход схемы 3 сравнения, где сравнивается с величиной (Ь ), отображаемого массива. Если результат сравнения то на выходе схемы 3 сравнения появляется сигнал, открывающий элемент

И 4 и разрешающий прохождение тактовой частоты с входа 10 на вход. коммутатора 6, а результат вычитания(Ь/4)/)с второго выхода схема 3 сравнения поступает на второй вход коммутатора 6 для формирования адреса при переписи информации в блок 7 индикации. При появлении сигнала тактовой частоты на входе коммутатора 6 информация, хранящаяся на регистре 5, переписываешься в блок 7 по адресу, сформированному коммутатором 6. Время сравнения адресов на зависит от величины отображаемого массива. Блок

7 позволяет наблюдать начальный адрес массива ячеек ОЗУ 12, предназначенного для отображения, и информа;, цию, записанную в ячейки ОЗУ 12 по начальному и следующим за ним по порядку адресам массива. Таким образом устройство позволяет одновременно

S 10031 отображать в блоке 7 индикации и, тем. самым, контролировать информацию, записываемую в массив ячеек ОЗУ 12 с адресами, следующими друг за другом, за счет чего расширяется область применения устройства.

Технико-экономическое преимущество предлагаемого устройства заключается в более широкой области его применения по сравнению с прототипом, te

Формула изобретения

1. Устройство для контроля инфор- i$ мации, записываемой в оперативную память, содержащее блек ввода адресов буферный регистр, вход которого является информационным входом устройства, элемент И, первый вход которого 2в является тактовым входом устройства и блок индикации, одни из входов которого соединены с одними из выходов блока ввода адресов, о т л и ч аю щ е е с.я тем, что, с целью расши- 2s рения области применения устройства за счет обеспечения контроля информации, записанной по нескольким адрегам, в него введены схема сравнения, ( первый коммутатор и сумматор по моду- Зв лю два, один из входов которого явля ется адресным входом устройства, другие входы подключены к одним из вы49 4 ходов блока ввода адресов, а выходык одним из входов схемы сравнения другие входы которой соединены с другими выходами блока ввода адресов, Р а один из выходов подключен к второму входу элемента И, выход которого соединен с первым входом первого коммутатора, второй и третий входы которого подключены соответственно к другому выходу схемы сравнения и к выходу буферного регистра, а выход соединен с другим входом блока индикации.

2. Устройство по п.1, о т л и ч аю щ е е с я тем, что блок ввода адресов содержит регистр начального адреса, регистр количества адресов, датчик адресов, ключ и второй коммутатор, входы которого соединены сеответственно с выходом датчика адресов и с выходом ключа, а выходы - соответственно с входами регистра начального адреса и с входами регистра количества, адресов, выходы регистра начального адреса и регистра количества адресов являются выходами блока.

Источники информации, принятые во внимание при экспертизе

1. Явторское свидетельство СССР и 584338, кл. G 11 С 29/00, 1977.

2. Патент Японии и 54-42338, кл. 97(7) СО, опублик. 1979 (прото-. тип).

>sari

1003149

Составитель Т. Зайцева

Редактор Н. Гришанова Техред Т.фанта Корректор М. Демчик

Заказ 1569/36 Тираж 592 Подписное

ВНИИПИ Государственного комитета. СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП "Патент", г. Ужгород, ул. Проектная, 4