Запоминающее устройство с контролем информации при записи

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советск ив

Социалистическик

Республик (11)! 003151 (В1) Дополнительное к авт. свид-ву (22)Заявлено 09.10 ° 81 (21) 3343868/18-24 с присоединением заявки J% (23) ПриоритетОпублнковано 07. 03.83. Бюллетень Мв 9

Дата опубликования описания 07.03.83 (53 ) M. Кл..

0 11 С 29/00

Гесударстеевлмй кемлтет

СССР яо делам кзебретелкй и открытий (53) УДК 681.327 (088.8) (72) Авторы изобретения

В. В. Мищенко и Ю. B. Быценко

М у т (7l) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С КОНТРОЛЕМ

ИНФОРМАЦИИ ПРИ ЗАПИСИ

Устройство относится к запоминающим устройствам и может быть исполь. зовано для контроля записи информации в запоминающие устройства.

Известно запоминающее устройство с контролем информации, содержащее адресный блок, блок формирования данных, блок управления, счетчик, регистры и блок сравнения, причем выходы блока управления подключены соответственно к входам адресного блока, блока формирования данных, к счетчику и первому регистру, выходы счетчика и первого регистра подключены к входам блока сравнения и второго регистра, выход которого соеди.нен с выходом устройства, выход блока сравнения подключен к одному из входов блока управления (1) .

Один из недостатков этого устройства заключается в большом времени обращения к накопителю из-за предварительного тестирования накопителя, при этом не исключаются искажения, 2 возникающие при записи информации, предназначенной для хранения в накопителе после тестирования. Другой недостаток устройства заключается в больших аппаратурных затратах, выз. ванных необходимостью хранения тестовых программ и органиэации тестирования накопителя по этим программам

Из известных устройств наиболее близким техническим решением к предлагаемому является запоминающее устройство с самоконтролем, содержащее накопитель, входной и выходной регистры числа, блок контроля, элемент задержки и блок управления, причем выходы регистров соединены с блоком контроля, выход которого подключен к входу накопителя, связанного му с контрольным разрядом накопителя

) а вход элемента задержки подключен ,к выходу контрольного разряда Hàêîпителя, а его выход - к счетным входам выходного регистра. Работа уст3 1003 ройства заключается в записи числа в накопитель через входной регистр, затем считывании этого числа из накопителя, записи его в выходной регистр и сравнении двух чисел, записанных во входном и выходном регистрах. По результату сравнения вырабатывается сигнал ошибки. Если при записи числа произошла ошибка, число во входном регистре инвертируется и повторно за- 10 писывается по этому же адресу в накопитель. При этом в контрольный разряд накопителя записывается сигнал логическая "1", который при считыва- нии числа из накопителя инвертирует его в выходном регистре (21.

Один иэ недостатков этого устройства заключается в его низком быстродействии, связанном с необходимостью двукратного обращения к накопителю:

20 вначале выполняется цикл записи,а за-тем цикл считывания числа иэ накопителя и записи его в выходной регистр.

Другой недостаток устройства заключается в том, что при записи инвертированного числа в накопитель возможно появление ошибки, которая приведет к дополнительному инвертированию числа, т.е. число запишется в прямон коде, а в этом случае число записывается с ошибкой. В этой ситуации произойдет зацикливание и дальнейшая запись информации в накопитель невозможна.

Цель изобретения - увеличение быстродействия устройства.

Поставленная цель достигается тем, что в запоминающее устройство с контРолем информации при записи, содержащее регистр числа, формирователь сигналов записи, блок контроля, накопитель, блок местного управления и последовательно соединенные регистр адреса и дешифратор адреса, выход кото-. рого подключен к одному из входов накопителя, другие входы которого соеди-4 нены с выходами регистра числа и фор" мирователя сигналов записи, а выход подключен к одному иэ входов блока контроля, другой вход которого соединен с выходом регистра числа, вве50 дены распределитель импульсов и элемент И, первый вход которого подключен к выходу блока контроля, второйк одному из выходов распределителя импульсов, а выход является управляющим выходом устройства, причем вход распределителя импульсов соединен с выходом блока местного управления, а другие выходы подключены соответствен151 4 но к входам регистра числа, формирователя сигналов записи и регистра адреса.

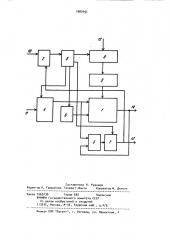

На чертеже представлена Структурная схема предлагаемого устройства.

Устройство содержит накопитель 1, блок 2 местного управления, блок 3 контроля, регистр 4 числа, распределитель 5 импульсов, формирователь 6 сигналов записи, элемент И 7, регистр

8 адреса, дешифратор 9 адреса. Устройство имеет входы 10-12 и выходы 13 и 14.

Устройство работает следующим образом.

По сигналам на входе 10 блок 2 местного управления синхронизирует ргботу устройства в процессе записи.

По сигналам от блока 2 распределитель

5 формирует последовательность синхронизирующих импульсов, с помощью которых производится запись в накопитель 1 и контроль числа в цикле записи, Для записи числа в накопитель по входу 12 поступает код адреса вы" бираемой ячейки памяти, а по входу

10 — сопутствующие коду адреса управляющие сигналы, под действием которых блок 2 и распределитель 5 выдают сигнал, с помощью которого код адреса записывается в регистр 4 числа.

Записываемое число по входу 11 поступает на регистр 4 числа. Под действием управляющих сигналов по входу

10 распределитель 5 выдает сигнал, по которому число записывается в регистр 4 числа. Через некоторое время, большее чем время переходных процессов в регистре 4 числа и время установки числа на входе накопителя 1, распределитель 5 формирует и выдает сигнал, который поступает на формирователь 6. Сформированным сигналом записи с выхода формирователя 6 число записывается а выбранную ячейку накопителя 1. После окончания действия сигнала записи и переходных процессов, связанных с действием это го сигнала, на выходе 14 устанавливается код числа, записанный в выб- . ранную ячейку накопителя 1. При этом код адреса удерживается на входе 12 еще некоторое время, поддерживая тем самым наличие кода числа на выходе

14, и в это время число на выходе достоверно.

Контроль записанного числа в накопитель 1 блоком 3 контроля производит. ся в то время, когда число на выходе

5 1003 накопителя 1 достоверно. 8 это время распределитель 5 выдает сигнал, открывающий элемент И 7, и результат аравнения чисел выдается на выход 13.

Бсли число записано в накопитель 1 без ошибки, то распределитель 5 выдает сигнал в регистр 8 адреса и изменяет его состояние на единицу. Последующее число, поступающее по входу

11, будет записано в следующую ячей- 10 ку накопителя 1. В случае записи числа в накопитель 1 с ошибкой на выход

13 поступает сигнал, информирующий процессор или другое устройство о том, что прозошла запись с ошибкой. Од- >s новременно этот сигнал поступает в блок 2 и прекращает цикл записи,и распределитель 5 не выдает сигнал для изменения состояния регистра 8 адреса. 20

Технико-экономическое преимущество предлагаемого устройства заключается в том, что введение распредели-. теля импульсов и элемента И, а также функциональных связей между ними поз-2 воляет производить контроль записи информации на максимальной частоте обращения, определяемой типом применяемых микросхем памяти в накопителе, при этом сокращается время обмена между зр запоминающим устройством и устройством, выдающим информацию (í",ïðèìåð, процессором цВН) Сокращение еремени ромена обусловлено исключением цикла считывания информации, равного по дли. тельности циклу записи.

151 б

Формула изобретения

Запоминающее устройство с контролем информации при записи, содержащее регистр числа, формирователь сигналов записи, блок контроля, накопитель блок местного управления и последова- . тельно соединенные регистр адреса и дешифратор адреса, выход которого подключен к одному из входов накопителя, другие входы которого соединены с выходами регистра числа и. Формирователя сигналов записи, а выход подключен к одному из входов блока контроля, другой вход которого соединен с выходом регистра числа, о тл и ч а ю щ е е с я тем, что, с целью увеличения быстродействия устройства, в него введены распределитель импульсов и элемент И, первый вход которого подключен к выходу блока контроля, второй - к одному из выходов распределителя импульсов, а выход является управляющим выходом устройства, причем вход распределителя импульсов соединен с выходом блока местного управления, а другие выходы подключены соответственно к входам регистра числа, формирователя сигналов записи и регистра адреса.

Источники информации, принятые во внимание при экспертизе

l. Авторское свидетельство СССР

N 601762, кл. G 11 С 29/00, 1977.

2. Авторское свидетельство. СССР

N 497639, кл. G 11 С 29/00, 1975 (прототип).

1003151

Составитель В. Рудаков

Редактор Н. Гришанова Техред Т.Фанта Корректор M. Дем ик

Заказ 1569/Зб Тираж 592 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, F-35, Раушская наб., д.4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4