Устройство для управления периодом следования импульсов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (иу 1 ООЗЗ 1 5 (61) Дополнительное к авт. свид-ву(22) Заявлено 150781 (21) 3322301/18-21 с присоединением заявки ¹â€” (23) Приоритет—

Опубликовано 07.0383. Бюллетень ¹9

Дата опубликования описания 070383 (1 М g< э

Н 03 К 3/64

Государственный комитет

СССР во делам изобретений и открытий (53) УДК 621.373. .4 (088.8) (72) Автор изобретения

Р. В. Галиев (71) Заявитель (54 ) УСТРОИСТВО ДЛЯ УПРАВЛЕНИЯ ПЕРИОДОМ

СЛЕДОВАНИЯ ИМПУЛЬСОВ

Изобретение относится к импульсной технике и может быть использовано в имитаторах сигналов частотных датчиков, автоматике, системах программного управления.

Известен преобразователь кода в частоту следования импульсов, содержащий генератор опорной частоты, устройство для изменения частоты следования импульсов по закону квадратичной гиперболы, счетчик импульсов, потенциально-импульсные вентили и регистр входного кода fl g.

Недостатком преобразователя является низкая точность установки . частоты, зависящая от точности нелинейного квадратора и дискретности задания опорной частоты.

Известен генератор с программным управлением, содержащий счетчик, накапливающий регистр, второй счетчик, схему сравнения, распределитель, обеспечивающий формирование разнообразных импульсов ) 2 ).

Недостатком является низкая точность установки частоты следования импульсов.

Цель изобретения — повышение точности задания частоты следования импульсов путем увеличения дискретности задания значений периода.

Поставленная цель достигается тем, что в устРойство для управления периодом следования импульсов, содержащее счетчик импульсов, блок совпадения кодов, одна группа входов которого соединена с выходами счетчика импульсов, а другая группа входов соединена с выходами разрядов регистра памяти, дополнительно введены ступенчатая линия задержки, селектор-мультиплексор, сумматор, причем вход ступенчатой линии задержки соединен с выходом блока совпадения кодов и входом селектораМультиплексора, остальные входы которого подключены к отводам ступенчатой линии задержки, вход управления селектора-мультиплексора соединен с младшим разрядом регистра памяти, а выход соединен с разрешающим входом регистра памяти, при этом выходы сумматора подключены параллельно к входам регистра памяти, входы сумматора соединены с выходами разрядов

РЕгистра памяти.

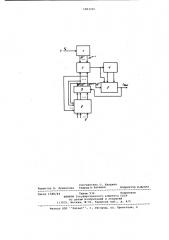

На чертеже представлена функциональная схема устройства для управления периодом следования импульсов.

1003315

Устройство для управления периодом следования импульсов содержит счетчик 1 импульсов, блок 2 совпадения кодов, регистр 3 памяти, ступенчатую линию 4 задержки, селектормультиплексор 5 и сумматор 6, шину

7 импульсов образцовой частоты, шину 8 двоично-десятичных (И+1) разрядных кодов периода формируемой частоты следования импульсов.

Устройство, работает следующим образом.

Счетчик 1 производит непрерывный подсчет числа импульсов образцовой частоты fo, поступающей по шине 7, поступающих íà его вход. При совпа- 15 дении кодов на выходе счетчика 1 и и старших двоично-десятичных разрядов регистра 3 памяти блок 2 совпадения кодов вырабатывает импульс, который подается на вход линии 4 задержки, осуществляющей последователь.— ную задержку импульса на величину — и, где Tö — период следования имTî

10 пульсов образцовой частоты Ео, m— номер отвода линии 4 задержки. Общее время задержки составляет 9 То/10.

В зависимости от значения дополнительного двоично-десятичного разряда с весами 10 " То регистра 3 памяти селектор-мультиплексор 5 передает на выход устройства импульс с одного., из отходов линии 4 задержки (или непосредственно с выхода блока

2 совпадения кодов, если m = О); задержанный на время то р .

С появлением каждого импульса на выходе селектора-мультиплексора

5 производится перезапись в регистр

3 памяти (И+1 )- разрядного двоичнодесятичного кода с выхода сумматора 40

6, представляющего собой сумму значений кода периода формируемой частоты И в данный момент времени и кода состояния регистра 3 памяти в момент времени, непосредственно пред- 45 шествующий процессу перезаписи.

В регистре 3 памяти происходит последовательное накопление кода порциями, равными значению периода формируемой частоты с шины 8, который в общем случае может изменяться для получения плавного (или скачкообразного) изменения формируемой частоты. В процессе аналогичного накопления кода с частотой fg в счет 55 чике 1 блок 2 совпадения кодов вырабатывает импульсы через промежутки времени, равные целочисленным значениям заданного периода Т, дискретизация с точностью до десятых долей (— ) производится посредством линии а

4 задержки и селектора-мультиплексора 5, управляемого дополнительным разрядом регистра 3. При смене кода управления N (шина 8) устройство т отрабатывает до конца предыдущее значение периода следования выходных импульсов, а .длительность последующего периода определяется уже новым значением N, что обусловливает возможность плавного (с дискретностью

10 T ) изменения частоты следования импульсов при соответствующем изменении кода N на входе устройт ства.

Таким образом предлагаемое устройство, по сравнению с известным, позволяет повысить. точность установ ки частоты следования импульсов, не увеличивая при этом образцовую частоту..

Формула изобретения

Устройство для управления периодом следования импульсов, содержащее счетчик импульсов, блок совпадения кодов, одна группа входов которого соединена с выходами счетчика импульсов, а другая группа входов соединена с выходами разрядов регистра памяти, о т л и ч а ю щ е е с я тем, что, с целью повышения точности эаданйя частоты, в него введены ступенчатая линия задержки, селектормультиплексор, сумматор, причем вход ступенчатой линии задержки соединен с выходом блока совпадения кодов и входом селектора-мультиплексора, остальные входы которого подключены к отводам ступенчатой линии задержки, вход управления селектора-мультиплексора соединен с младшим разрядом регистра памяти, а выход соединен с разрешающим входом регистра памяти, при этом выходЫ сумматора подключены параллельно к входам регистра памяти, а входы сумматора соединены с выходами разрядов регистра памяти.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 494847, кл. Н 03 К 13/02, 08.03.73.

2. Авторское свидетельство СССР

9 743176, кл . H 03 К 3/64, 06.12.77.

1003315

Заказ 1588/44

Тираж 934 Подписное

ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 е

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Составитель О. Ханджян

Редактор E. Лушникова Техред A. Бабинед Корректор И.Щулла