Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советскик

Социалистических

Республик л. ф 4. ,/б= К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 260681 (21) 3336465/18-21 (51) М. КЛ. с присоединением заявки Ио (23) Приоритет

Н 03 К 13/02

Государственный комитет

СССР по делам изобретений и открытий.

Опубликовано 070383. Бюллетень М 9

t53) УДК 681.325 (088. 8) Дата опубликования описания 07.0383

В.Э. Балтрашевич .

8 т

/ - -:--,!?

- - о,(,Р т;»;.„

Ленинградский ордена Ленина электротекйи кйй "- - институт им. В. И. Ульянова (Ленина) (72) Автор изобретения (71) Заявитель (54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к аналогоцифровым преобразователям и может быть использовано в области связи, вычислительной и измерительной технике, а также в автоматизированных системах управления технологическими процессами и системах автоматизации научных исследований.

Известно устройство аналого-цифрового преобразования по принципу поразрядного уравновешивания, содержащее цифроаналоговый преобразователь, счетный триггер, схему сравнения, блок управления, реверсивный счетчик, схемы совпадения, инвертор и формирователь импульсов, обеспечивающее сравнение сигнала рассогласования со значением эталона разряда, следующего за опрашиваемым. Если сигнал рассогласования меньше указанного эталона, то осуществляется коррекция образцового сигнала шагом,, соответствующим опрашиваемому разряду (1 ).

Недостатком такого аналого-цифрового преобразователя является не-. возможность обработки сигнала рассогласования в случае, если приращение входного сигнала за такт больше, чем значение эталона на данном такте.

Известен аналого-цифровой преобразователь, содержащий схему сравнения, цифроаналоговый преобразователь, реверсивный счетчик, распределитель импульсов, генератор импульсов, триггер управления и эле)р мент И (2g.

Недостатком устройства является, низкая достоверность выходных кодМ и большая погрешность преобразования, обусловленные тем, что величина шага квантования уменьшается вдвое на каждом такте независимо от ответов схемы сравнения, тем самым не учитывается. возможность изменения взаимного расположения входного сигнала и ранее сформированных образцовых уровней. Однако часто из" за различных сбоев, помех и утечек взаимное расположение образцового уровня и входного сигнала определяется неверно, что ведет к уменьшению достоверности и увеличению погрешности °

Цель изобретения - повышение дос товерности выходного кода и умень-. шение погрешности преобразования.

1003331

Поставленная цель достигается тем, что в аналого-цифровой преобразователь, содержащий схему сравнения, первый вход которой соединен с вхоцной клеммой, а второй вход соединен с выходом цифроаналогового 5 преобразователя, цифровые входы которого соединены с выходами соответствующих разрядов реверсивного счетчика, счетные входы разрядов которого соединены с выходами соответствующих разрядов распределителя импульсов, а входы установки режима работы — с выходом схемы сравнения, элемент И, первый вход которого соединен с единичным вцходом триггера управления, а второй вход — с выходом генератора импульсов, единичный вход триггера управления соединен с шиной "Запуск", а нулевой выход — с шиной "Готовность", введен блок разрешения уменьшения шага квантования, первый вход которого соединен с выходом схемы сравнения, второй вход — с выходом элемента И, а третий вход — c единичным выходом младшего разряда

25 распределителя импульсов, первый выход — с управляющим входом реверсивного счетчика, второй выходс входом распределителя импульсов, а третий выход — с нулевым входом 30 триггера управления.

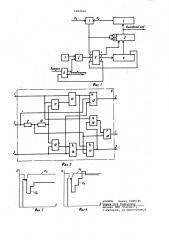

На фиг. 1 представлена функциональная схема аналого-цифрового преобразователя; на фиг. 2 — одна из возможных функциональных схем . для реализации блока разрешения уменьшения .шага квантования> фиг. 3 поясняет недостатки прототипа; фиг. 4 - сущность предлагаемого аналого-цифрового преобразователя. 40

Аналого-цифровой преобразователь (фиг. 1) содержит схему 1 сравнения, первый вход которой соединен с выходом источника входного сигнала, а второй вход соединен с выходом цифроаналогового преобразователя 2, цифровые входы которого соединены с выходами соответствующих разрядов реверсивного счетчика 3, счетные входы разрядов реверсивного счетчика 3 соединены с выходами соответствующих разрядов распределителя .4 импульсов, выход схемы 1 сравнения соединен с входами установки режима работы реверсивного счетчика 3, первый вход элемента И 5 соединен с единичным выходом триггера 6 управления, а второй вход — с выходом генератора 7 импульсов, единичный вход триггера 6 соединен с шиной

"Запуск", а нулевой выход — с шиной "Готовность", первый вход блока 8 разрешения уменьшения шага квантования соединен с выходом схемы 1 сравнения, второй вход — с выходом элемента И 5, а третий вход с единичным выходом последнего (младшего) разряда распределителя

4 импульсов, первый выход блока 8 разрешения уменьшения шага квантования соединен с управляющим входом реверсивного счетчика 3, второй выход — с входом распределителя

4 импульсов, а третий выход — с нулевым входом триггера 6 управления.

Одна из возможных схем реализации блока 8 разрешения уменьшения шага квантования (фиг. 2) содержит первый 9 и второй 10 элементы задержки, первый 11 и второй 12 триггеры, логический элемент 13 неравнозначности, первый 14, второй 15, третий

16 и четвертый 17 элементы И, а также элемент ИЛИ 18. Первый 11 и второй 12 триггеры служат для запоминания состояния на предыдущем такте соответственно схемы 1 сравнения и последнего (младшего) разряда распределителя 4 импульсов (фиг. 1) .

Если обозначить через fi ) ответ схемы сравнения на i-м такте (О ) Ux), через g — сигнал от генератора импульсов (фиг. 1), через g< — задержанный сигнал от генератора импульсов (с помощью элемента 9 задержки на фиг. 2), а через п ti ) — состояние последнего (младшего) разряда распределителя импульсов на i-м такте, то закономерность появления сигнала на 3-м выходе (т.) блока

3 разрешения уменьшения шага квантования может быть задана в виде

Сущность предлагаемого решения заключается в том, что уменьшение величины .шага квантования производится только при чередовании отве- . тов схемы сравнения, тем самым достигается воэможность проверки наличия сигнала в текущем отрезке шкалы, т.е. между предыдущими и текущими образцовыми уровнями.

Устройство работает следующим образом.

Сигнал начальной установки устанавливает в реверсивном счетчике

3 и в распределителе 4 импульсов код 10...0, триггер 6 управления переводится в "0", блок 8 разрешения уменьшения шага квантования переводится в состояние, соответствующее ответу схемы 1 сравнения на предыдущем такте (4 Р- 13 U„ > u ), Реверсивный счетчик 3 переводится в режим сложения. Цепи начальной установки на фиг. 1 не показаны.

1003331

Преобразователь начинает работать после прихода сигнала "Запуск", устанавливающего триггер 6 управления в "1".

При ответе схемы сравнейия Ох)0 реверсивный счетчик переводится в режим сложения, а при Ux< Ов — в режим вычитания. В реверсивном счетчике по сигналу f происходит увеличение (при Ux ) 4о ) или уменьшение (при 0„ < 0 ) кода на одну единицу, вес которой задается текущим кодом распределителя 4 импульсов.

При чередовании ответов схемы сравнения на втором выходе блока 8 разрешения уменьшения шага квантования появляется сигнал f 2, в результате осуществляется сдвиг вправо единИцы в распределителе 4 импульсов, т.е. уменьшается вдвое шаг квантования. При совпадении ответов схемы сравнения величина шага квантования не меняется.

После формирования величины шага квантования на первом выходе блока 8 разрешения уменьшения шага квантования появляется сигнал изменяющий содержимое реверсивного счетчика 3 на величину шага квантования, хранящуюся на распределителе 4 импульсов. После того, как последний (младший) разряд распределителя импульсов устанавливается в "1", дальнейший сдвиг вправо, как уже отмечалось, запрещается и осуществляется проверка попадания сигнала в квант. При появлении сигнала f3 на третьем выходе блока 8 разрешения уменьшения шага квантования триггер 6 управления устанавливается в "0", выдается сигнал

"Готовность" и преобразование заканчивается, при этом, если 0о ), u x, то сигнал f уменьшает содержимое реверсивного счетчика 3 на единицу (квант). На фиг. 4 приведен пример,. поясняющий сущность предлагаемого аналого-цифрового преобразователя при преобразовании постоянного входного сигнала и при воздействии одиночной помехи.

Моделирование прототипа и предлагаемого преобразователя показывает, что при воздействии помех погрешность прототипа может достигать величины половины диапазона возможных-изменений входного сигнала, в то время как погрешность предлагаемого преобразователя не превышает одного кванта. Таким образом, введение блока разрешения уменьшения шага квантования позволяет значительно повысить достоверность выдаваемого кода и уменьшить погрешность преобразования.

Формула изобретения

Аналого-цифровой преобразователь, содержащий схему сравнения, первый

15 вход которой соединен с входной клеммой, а второй вход соединен с выходом цифроаналогового преобразователя, цифровые входы которого соединены с выходами соответствующих разрядов реверсивного счетчика, счетные входы разрядов которого сое:динены с выходами соответствующих разрядов распределителя импульсов, а входы установки режима работы

25 с выходом схемы сравнения, элемент

И, первый вход которого соединен с единичным выходом триггера управления, а второй вход — с выходом генератора импульсов, единичный вход триггера управления соединен с шиной "Запуск", а нулевой выход - с шиной "Готовность", о т л и ч а юшийся тем, что, с целью повышения достоверности выходного кода и уменьшения погрешности преобразования, в него введен блок разрешения уменьшения шага квантования, первый вход которого соединен с выходом схемы сравнения, второй входс выходом элемента И, а третий вход—

40 с единичным выходом младшего разряда распределителя импульсов, первый выход — с управляющим входом реверсивного счетчика, второй выходс входом распределителя импульсов, 45 а третий выход — с нулевым входом триггера управления.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

50 9 214205, кл. Н 03 К 13/17, 1967.

2. Полупроводниковые кодирующие и декодирующие преобразователи.

Под ред. В.Б.. Смолова и др., Л., "Энергия", 1967, с. 135, рис. 2-5.

1003331

ВНИИПИ Заказ 1589/45

Ти аж 934 Подписное

Филиал ППП "Патент", r.Óæãoðîä, ул.Проектная,4