Преобразователь биполярного кода в однополярный

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (63) Дополнительное к авт. сеид-ву— (22) 3asaaeHo 270881 (21) 3332292/18-21 с присоединением заявки ¹ (23) Приоритет

Опубликовано 070383 Бюллетень № 9 (1 М g 3

Н 03 К 13/24

Н 03 К 5/00

Государственный комитет

СССР но делам изобретений и OTKpblTHH (53) УДК 681.325. (088.8) Дата опубликования описания 07.03.83

Л.К. Самойлов, В.В. Гайворонский и Я,.П ;-", Т жкук

I (72) Авторы изобретения (71) Заявитель

Таганрогский радиотехнический инсти им. В.Д. Калмыкова (54) ПРЕОБРАЗОВАТЕЛЬ БИПОЛЯРНОГО КОДА

В ОДНОПОЛЯРНЫЙ

Изобретение относится к проводной связи и предназначено для приема и преобразования кодовых сигналов (одно- или двуполярных1 с проводной симметричной линии связи, в частности для преобразования биполярного самосинхронизирующегося кода в однополярные импульсы.

Известен преобразователь биполярного сигнала в однополярный, содержащий входное пороговое устройство, элемент ИЛИ-HE c инверсными входами и RS-триггерт причем выходы порогового устройства являются входами всего устройства, выходы порогово- . го устройства соединены с инверсными входами элемента ИЛИ-НЕ, а также с входами RS-триггера 1 ).

Данное устройство позволяет принимать на входе самосинхронизирующий ся биполярный код, однако оно обладает низкой помехозащищенностью к синфазным помехам в линии связи.

Наиболее близким по технической сущности и достигаемому эффекту к предлагаемому является устройство, содержащее резистивно-емкостные цепи согласования линии связи, дифференциальный усилитель, два ключевых элемента, элементы И-НЕ и узел регистрации парофазной помехи, причем резистивно-емкостные цепочки включены между входами дифференциального усилителя и шиной нулевого потенциала, первый и второй выходы дифференциального усилителя соединены с входами соответственно первого и второго ключевых элементов, выходы которых соединены с входами элемента И-НЕ и с входами узла регистрации парофазной помехи, выход элемента И-НЕ является информационным выходом приемника (23.

Данное устройство обладает более высокой устойчивостью к синфазным помехам, чем предыдущее, однако также. имеет ряд недостатков. Устройство не декодирует троичного сигнала, так как выдает на выход либо нулевой, либо единичный сигнал, т.е. не различает положительное и отрицательное напряжение между проводами линии связи и в обоих случаях выдает единичный сигнал на выходе ° Поэтому оно не может, как предыдущее, декодировать биполярный самосинхронизирующийся код. Низкая. помехоустойчивость к парофазным импульсным помехам, не нарушающим чередование полярностей импульсов

1003334

15

40

50

65 в линии, объясняется тем, что вход1 ные емкости резистивно-емкостных цепей согласования линии имеют небольшую величину и заряжаются через низкое выходное сопротивление линии связи. Поэтому короткие парофазные помехи вызывают срабатывание диф, ференциального усилителя и, если такая помеха не нарушит чередования . полярностей, произойдет искажение передаваемой информации. Низкая помехоустойчивость к синфазным помехам обусловлена тем, что входные сигналы с линии подаются непосредственно на входы дифференциального усилителя.

Цель изобретения - повышение помехоустойчивости, надежности и расширение функциональных воэможностей путем обеспечения декодирования троичных кодов.

Для достижения указанной цели в преобразователь биполярного кода в однополярный, содержащий дифференциальный усилитель и два ключевых элемента, причем вход первого ключевого элемента соединен с выходом дифференциального усилителя, введены второй дифференциальный усилитель, четыре делителя, два фильтрующих конденсатора, элемент ИЛИ и выходной усилитель, причем входы первого и второго делителей подключены к первому входу устройства, входы третьего и четвертого делителей подключены к второму входу устройства, первый и второй фильтрующие конденсаторы включены соответственно между выходами первого и третьего, второго и четвертого делителей, выходы первого и четвертого делителей соединены с прямосмещенными входами соответственно первого и второго дифференциальных усилителей, выходы второго и третьего делителя соединены с обратносмещенными входами соответственно второго и первого дифференциальных усилителей, выход второго дифференциального усилителя соединен с входом второго ключевого элемента, выходы ключевых элементов подключены к соответствующим входам элемента ИЛИ, выход которого подключен к выходу синхронизации устройства, выход второго ключевого элемента через выходной усилитель подключен к информационному выходу устройства.

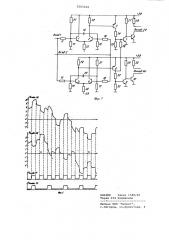

На фиг. 1 приведена электрическая принципиальная схема устройства; на фиг. 2 - временная диаграмма работы устройства.

Устройство содержит первый и втот рой дифференциальные усилители на транзисторах 1 и 2, 3 и 4 соответственно, ключевые элементы на транзисторах 5 и 6, элементы ИЛИ на транзисторах 7 и 8, выходной усилитель на транзисторах 9 и 10, делители напряжения на резисторах 11-18, фильтрующие конденсаторы 19 и 20, .резисторы 21-35.

Устройство работает следующим образом.

При дифференциальном напряжении между первым и вторым входом по модулю меньше пороговой величины, задаваемой резисторами 21, 12 и 31, 17 соответственно в первом и втором дифференциальных усилителях, транзисторы 1 и 4 открыты, транзисторы 3, 2, 6 и 5 закрыты, на информационном выходе и выходе синхронизации будут низкие уровни напряжения, так как транзисторы 10 и 8 будут открыты и насыщены. Резисторы 28 и 35 могут быть соединены с коллекторами транзисторов 8 и 10 или не соединены в зависимости от характера нагрузки на выходах устройства.

При синхронном нарастании или уменьшении напряжения в линии связи, например, как показано на фиг.

2, + 7 Вв момент времени t< или до

-7 В в момент времени t, преобразователь остается в исходном состоянии и на его выходах низкие напряжения. Диаграмма выходных напряжений устройства (фиг. 2) показана для случая, когда резисторы 28 и

35 соединены с коллекторами транзисторов 8 и 10.

Если происходит парофазное изменение напряжения в линии связи, например увеличение напряжения на первом входе относительно второго входа до пороговой величины, то происходит переключение второго дифференциального усилителя, открываются транзисторы 3, 6, 9 и 7,,закрываются транзисторы 10 и 8 и на выходах устройства появляются высокие уровни напряжения, т.е. синхроимпульс и информационный импульс. Когда парофаэное напряжение . между первым и вторым входами отрицательное и больше (по абсолютной величине) заданного порога, переключается первый дифференциальный каскад, открываются транзисторы 2, 5 и 7 и появляется высокое напряжение на выходе. синхронизации. Инфор- . мационный выход в этом случае имеет низкий уровень напряжения, Делители входного напряжения обеспечивают уменьшение амплитуды сигналов на базах транзисторов дифференциальных усилителей, что позволяет увеличить максимально допустимое синфазное входное напряжение до 10В, а допустимое парофазное напряжение — до ,15В. Фильтрующие конденсаторы 20 и

19 образуют ийтегрирующие цепочки соответственно с резисторами 13, 18, 11 и 16, что позволяет повысить

1003334, Формула изобретения

40 парофазную помехоустойчивость за счет срезания импульСных наводок с длительностью, меньшей длительности информационных сигналов. Элемент

ИЛИ обеспечивает сигнализацию о на.личии в линии парофазной разности напряжений между проводами, а выход" ной усилитель указывает полярность этого напряжения.

Таким образом, введение новых элементов-делителей, фильтрующих конденсаторов элемента ИЛИ, выхбд.ного усилителя - позволяет повысить устойчивость устройства к парофазным помехам и допустимый уровень входных синфазных и парофазных нап- 15 ряжений, существенно расширить функциональные воэможности устройства.

Предлагаемый преобразователь может декодировать парофазные сигналы обычных ТТЛ-формирователей, квазитроичные сигналы, биполярный код в условиях синфазных помех, превышающих по амплитуде напряжение питания преобразователя (синфазные помехи до 10В при питании +5В) . По сравнению с существующими ЭСЛ дифференциальными приемниками предлагаемый преобразователь обладает бо.лее высокими помехоустойчивостью и надежностью и более широкими 30 функциональными возможностями.

Преобразователь биполярного кода в однополярный, содержащий дифференциальный усилитель и два ключевых элемента, причем вход первого ключевого элемента соединен с выходом дифференциального усилителя, отличающийся тем, что, с целью повышения его помехоустойчивости, надежности и расширения функциональных возможностей путем обеспечения декодирования. троичных кодов, в него введены второй дифференциальный усилитель, четыре делителя, два фильтрующих конденсатора, элемент ИЛИ и.выходной усилитель, причем входы первого и второго делителей подключены к первому входу устройства, входы тре-. тьего и четвертого делителей подключены к второму входу устройства, первый и второй фильтрующие конденсаторы включены соответственно между выходами первого и третьего, вто-, рого и четвертого делителей, выходы первого и четвертого делителей соединены с прямосмещенными входами соответственно первого и второго дифференциальных усилителей, выходы второго и третьего делителей соединены с обратносмещенными входами соответственно второго и первого диф ференциальных усилителей; выход вто-. рого дифференциального усилителя соединен с входом второго ключевого элемента, выходы ключевых элементов подключены к соответствующим входам элемента ИЛИ, выход которого подключен к выходу синхронизации устройства, выход второго ключевого элемента через выходной усилитель подключен к информационному выходу устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 595853, кл. Н 03 К 5/00, 15.07.76.

2. Семенов A.A. Приемопередатчики с квазитроичной кодировкой информации для симметричной линйи связи. ОИЯИ 11-11627, Дубна, 1978, с. 6, рис. За. - РЖ "Электросвязь", 1979, 9 1, реферат 1.64.325.

1003334

ВНИИПИ Заказ 1589/45

Тираж 934 Подписное

Филиал ППП "Патент", r.Óæroðîä, ул.Проектная, 4