Делитель частоты следования импульсов

Иллюстрации

Показать всеРеферат

(72) Авторы изобретения

Б: А. Киреев, Л. П. Ларин и Ю. П. Урадо (7! ) Заявитель (54) ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ

I!

Изобретение относится к .импульсной технике и может использоваться, например, в цифровых импульсных генераторах, синте- заторах частоты.

Известен делитель частоты, содержащий счетчик импульсов, элемент задержки; weмент ИЛИ (1).

Недостаток указанного устройства — низкая надежность деления частоты, Наиболее близким к предлагаемому является делитель частоты следования импульсов, 10 содержащий блок управления, выходы которого соединены с входами запоминающего элемента, выходы которого соединены с первыми входами элемента сравнения кодов, вторые

35 входы которого соединены с выходами ситчика импульсов (2).

Недостатком известного устройства является низкая надежность его работы.

Цель изобретения — повышение надежности >о работы устройства.

Поставленная цель достигается тем; что в делитель частоты следования импульсов, содержащий блок управления, выходы которого соединены с входами запоминающего элемента;" выходы которого соединены с первымн . входами элемента сравнения кодов, вторые входы которого соединены с выходами счетчика импульсов, введены дешифратор кода исходного состояния, элемент ИЛИ и формирователь импульсов задержки, вход которого соединен с выходом элемента сравнения кодов, а выход — с одним из входов элемента ИЛИ, выход которого соединен с установочным входом счетчика импульсов, входы дешифратора кода

;исходного состояния подключены к выходам запоминающего элемента, а выход — к второму входу элемента ИЛИ.

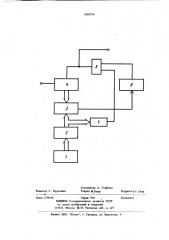

На чертеже представлена структурная функциональная схема устройства.

Устройство содержит блок 1 управления, элемент 2 запоминающий, элемент 3 сравнения кодов, счетчик 4 импульсов, элемент ИЛИ 5, формирователь 6 импульсов задержки, дешифра. тор 7 кода исходного состояния.

Устройство работает следующим образом.

На счетный вход счетчика 4 поступает последовательность входных импульсов, которая

3 100335 изменяет его выходной код, В момент совпадения кодов счетчика 4 с кодом запоминающего элемента 2, записанного блоком 1 управлейия

1 на выходе элемента 3 сравнения возникает потенциал, передний фронт которого производит запуск формирователя 6 длительности импульсов. В момент появления импульсов на выходе формирователя 6 начинается переключение в исходное состояние счетчика 4 по установочному входу черрэ элемент ИЛИ 5. После переклю-. 16 учения хотя бы одного разряда счетчика 4 импульсы на выходе элемента 3 сравнения кодов прекратятся, однако в течение длительности импульсов, сформированных формирователем 6, происходит надежное переключение в исходное состояние всех разрядов счетчика. Дешифратор

7 кода исходного состояния необходим для формирования на его выходе потенциала, надежно устанавливающего счетчик 4 в исходное состояние, запрещая счет Импульсов счетчиком

4 прн установке кода в запоминающем элементе 2, равным коду исходного состояния. Это особенно необходимо, когда за исходное состояние счетчика принято нулевое, и при коде, равном нулю, делитель не должен формирован импульсы, так как деление на нуль невозможно, Очевидно, что длительность импульса на выходе формирователя У определяется неравенством СЧ 1иО -ф И1 где t — максимальное время переключения разряда счетчика по установочному входу;

Т „, — период следования импульсов, поступающих на.. вход делителя частоты.

Длительность импульса запуска формирователя 6 на выходе элемента 3 сравнения определяется выражением ИЭС C М1И 9с Se3 где t — минимальное время переклю ч ими чения счетчика по установочному входу;

3С вЂ” время переходного процесса в элементе сравнения кодов; — время задержки переключения Ф формирователя импульса.

Время задержки t должно удовлетворять неравенству (t ynw + чс т уЬ «1и

В предлагаемом устройстве допускается, возможность установки коэффициента деления частоты входных импульсов в системае счисления с основанием N за счет того, что счетчик 4 в устройстве может быть выполнен в виде последовательно соединенных двоичноN-ричных счетчиков. Каждый счетчик делителя нри этом с частью элемента сравнения, запоминания и управления образует двоично-М-ричный разряд. Установочные входы счетчиков каждого разряда соединены вместе и подкюпочены к выходу формирователя длительности импульсов, Формула изо бретения

Делитель частоты следования импульсов, содержыций блок управления, выходы которого соединены с входами запоминающего элемента, выходы которого соединены с первыми входами элемента сравнения кодов, вторые входы которого соединены с выходами счетчика импульсов, о т л и ч а ю щ и йс я тем, что, с целью повышения надежности

его работы, в него введены дешифратор кода исходного состояния, элемент ИЛИ и формирователь импульсов задержки, вход которого соединен с выходом элемента сравнения кодов, а выход — с одним из входов элемента ИЛИ, выход которого соединен с установочным входом счетчика импульсов, входы дешифратора кода исходного состояния подключены к выходам запоминающего элемента, а выход— к второму входу элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР No 875641 кл. Н 03 К 23/02, 13.02.80.

2. Заявка Японии К 51 — 37862, кл. 98 (5) С 32, 18.10.76.

1003354

Составитель А. Горбачев

Техред М.Тепер

Редактор С. Крупенина

Корректор Г. Огар

Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Заказ 1590/46 Тираж 934

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5