Реверсивный счетчик

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскнк

Социалистических

Республик (11.j I 003356, (61) Дополнительное к авт. свид-ву (22) Заявлено 30 03.81 (21) 3266421/18 21 с присоединением заявки М (23) Приоритет (51)М. Кл.

Н 03 К 23/02

Гевуаврстввкай квнвтвт

СССР

Ав яввват Азвврвтвккв я вткрнткй

Опубликовано 07.03.83. бюллетень рр 9

Дата опубликования описания 07.03.83 (53) УДК 621.374. .4 (088.8) (72) Авторы изобретения

В. Ф. Мочалов и В. Л. Лысенко (71) Заявитель б (54) РЕВЕРСИВНЫЙ СЧЕТЧИК

Изобретение относится к вычислительной технике и автоматике и может быть нспользовано для счета импульсов.

Известен реверсивный счетчик, содержащий группы разрядов, тактовые входы которых соединены с входом счетчика, а выход переноса каждой группы соединен с тактовыми входами разрядов следующих. групп (1)Недостатком этого реверсивного счетчика является функциональная ненадежность.

Наиболее близким по технической сущ1О ности является реверсивный счетчик, содержащий группы разрядов, каждый из которых содержит первый и второй формирователи сигнала переноса,. первый и второй коммута55 ционные триггеры и триггер памяти, тактовые входы всех коммутационных триггеров данной группы разрядов соединены с входом1 счетчика и первым и вторым выходами переноса каждой Н3 предыдущих групп разрядов зп разрешающие входы коммутационных триггеров данного разряда данной группы разрядов соединены с первым и вторым выходами формирователей сигнала переноса каждого разряда, предшествующего данному в этой же группе разрядов, а с одним из входов первого н второго формирователей сигнала переноса каждого разряда соединены соответственно шины "Сложение" и "Вычитание (2).

Недостатком этого реверсивного счетчика является относительно низкое быстродействие.

Это связано с необходимостью использования связей каждого разряда со всеми последующими, что приводит к большой нагрузке на элементы и снижению быстродействия.

Цель изобретения — повышение быстродействия.

Поставленная цель достигается тем, что в реверсивном счетчике, содержащем группы разрядов, каждый из которых содержит первый и второй формирователи сигнала переноI са, первый и второй .коммутационные триггеры и триггер памяти, тактовые входы всех коммутационных триггеров данной группы разрядов соединены с входом счетчика и первым и вторым выходами переноса каждой нз предыдущих групп разрядов, разрешающие входы коммутационных триггеров данного

1003356 разряда данной группы разрядов, кроме последнего разряда этой же группы и первого разряда первой группы, соединены с первым и вторым выходами формирователей сигнала переноса всех предыдущих разрядов в этой S же группе, разрешающие входы первого и второго коммутационных триггеров последнего разряда данной группы разрядов соединены соответственно с первым и вторым выходами формирователей сигнала переноса каждого разряда, предшествующего последнему разряду в этой же группе разрядов, а с одним из входов первого и второго формирователей сигнала переноса каждого разряда соединены соответственно шины "Сложение" и "Вычита- 1 ние", к информационным входам первого коммутационного триггера последнего разряда данной гр"ппы разрядов подключены прямой выход второго коммутационного триггера этого же разряда, шина "Сложение", инверс- 20 ный и прямой выходы соответственно первого коммутационного триггера и триггера памяти каждого разряда, предшествующего последнему разряду в данной группе разрядов, а к информационным входам второго коммутацион- 2$ ного триггера последнего разряда данной группы разрядов подключены инверсный выход первого коммутационного триггера этого же разряда, шина "Вычитание", прямой и инверсный выходы соответственно второго, щ коммутационного триггера и триггера памяти. каждого разряда, предшествующего последнему разряду в данной группе разрядов, при этом прямой выход первого коммутационного триггера и инверсный выход второго коммутационного триггера последнего разряда данной группы разрядов соединены соответственно с входами установки и сброса триггера памяти каждого разряда, предшествующего последнему разряду в этой же группе разрядов, выходы первого и второго формирователей: сигнала переноса последнего разряда данной группы разрядов соединены соответственно с первым и вторым выходами переноса данной группы разрядов, а с одним из разрешающих входов

4S первого и второго коммутационных триггеров последнего разряда данной группы разрядов соединены соответственно второй и первый выходы переноса этой же группы разрядов.

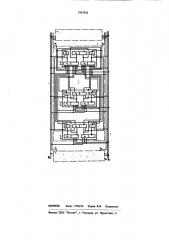

На чертеже изображена схема реверсивного счетчика.

Устройство содержит группы 1 разрядов, разряды 2-1 — 2-к группы, первый и второй коммутационные триггеры 3 и 4 разряда, триггер 5 памяти разряда, первый и второй формирователи 6 и 7 сигнала переноса разl ряда, первый и второй выходы 8 и 9 переноса группы разрядов, шику 10 "Сложение" и шину 11 "Вычитание", вход 12 счетчика.

Каждая группа разрядов реверсивного счетчика работает следующим образом, Пусть на шине 10 — логическая "1" а на шине 11 — логический "0", т. е. счетчик работает в режиме суммирования. Тогда изменение состояния триггеров 5 памяти этой группы происходит по импульсам, подаваемым на вход 12, при условиии, что сигналы на первом и втором выходах переноса 8 и 9 каж— дой из предыдущих групп разрядов равны логической "1". При выполнении этого условия происходит переключение триггера 5 памяти первого разряда 2-1 этой группы, если перед этим же -триггеры 5 памяти этой группы находились в нулевом логическом состоянии. В ближайшей паузе между импульсами, подаваемь1ми на вход. 12, появляется логическая "1" на выходе первого формирователя

6 сигнала переноса первого разряда 2-1 этой группы. При следующем выполнении условия срабатывания для этой группы происходит . переключение триггеров 5 памяти первого

2-1 и второго 2-2 разрядов этой группы и т. д. К моменту прихода 2 М-го импульса, где М вЂ” коэффициент пересчета предыдущих групп разрядов счетчика, появляется логическая

"1" на первом выходе переноса 8 этой группы. 2" М-й импульс производит переключение всех триггеров 5 памяти этой группы и триггера памяти первого разряда следующей группы разрядов. Работа группы разрядов счетчика в режиме вычитания аналогична вышеописанному.

Таким образом, при введении новых свя--: зей снижается нагрузка на выходы переносов, что обеспечивает повышение быстродействия счетчика.

Формула изобретения .Реверсивный счетчик, содержащий группы разрядов, каждый из которых содержит первый и второй формирователи сигнала переноса, первый и второй коммутационные триггеры и триггер памяти, тактовые входы всех коммутационных триггеров данной группы разрядов соединены с входом счетчика и первым и вторыМ выходами переноса каждой из предыдущих групп, разрядов, разрешающие входы коммутационных триггеров данного разряда данной группы разрядов, кроме последнего разряда этой же группы и первого разряда первой группы, соединены с первым и вторым выходами формирователей сигнала переноса всех предьщущих разрядов в этой же группе, разрешающие входы первого и второго коммутационных триггеров последнего разряда данной группы разрядов соединены

5 10033 соответственно с первым и вторым вйходами формирователей сигнала переноса каждого . разряда, предшествующего последнему разряду в этой же группе разрядов, а с одним из входов первого и второго формирователей сигнала переноса каждого разряда соединены соответственно„шины Сложение" и ."Вычита- ние", отличающийся тем, что, с целью повышения его быстродействия,.к информационным входам коммутационного триггера последнего разряда данной группы разрядов подключены прямой выход второго коммутационного триггера этого же разряда, шина "Сложение", инверсный и прямой выходы соответственно первого коммутационного 1З триггера и триггера памяти каждого разряда, предшествующего последнему разряду в дан. ной группе разрядов, а к информационным входам второго коммутационного триггера последнего разряда данной группы разрядов подключены инверсный выход первого коммутационного триггера этого же разряда, шина "Вычитание", прямой и Юйверсный: выходы соответственно второго коммутационного триггера и триггера памяти каждого,...,l5 разряда, предшествующего последйему разряду

56 d

B g3HHoH группе уазрядов, при этом прямой выход первого коммутационного триггера и инверсный выход второго коммутационного . триггера последнего разряда данной группы разрядов соединены соответственно с входами установки и сброса триггера памяти каждого разряда, предшествующего последнему разряду в этой же группе разрядов, выходы первого и второго формирователей сигнала переноса последнего разряда данной группы разрядов соединены соответственно с первым и вторым выходами переноса данной группы;урядов, а с одним из разрешающих входов первого и второго коммутационных триггеров последнего разряда данной группы разрядов соединены соответственно второй и первый выходы переноса этой же группы разрядов.

Источники информации, принятые во внимание при экспертизе

1. Майоров С. А. Проектирование микроэлектронных цифровых устройств. М., "Советское радио", 1977, с. 156, рис. 5.7.

2. Авторское свидетельство СССР Н 287121, кл. Н 03 К 23/00, 1969 (прототип).

1003356

ВНИИПИ Заказ 1590/4б Тираж 934 Подписное

Филиал ППП "Патент", r Ужгород, ул. Проектная, 4