Устройство для измерения дифференциально-фазовых искажений

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Ссноз Советских

Социалистических

Республик

Н 04 и 7/02

Государственный комитет

СССР но делам изобретений и открытий

1з З! УДК б 21 ° 397. 13 (088.0) Дата опубликования описания 07.03.83 т и Ю.k Сташкив - :.. -:

1, ::

i -»:»i и.- .-„

"». = P (72) Авторы изобретения

Ю.А. Медведев, В.Т. Басий (71) Заявитель (54)) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДИФФЕРЕНЦИАЛЬНОФАЗОВЫХ ИСКАЖЕНИЙ

Ясли т.1 )т (42 l

8q I ) „

Изобретение относится к средствам телевизионных измерений, в частности, к устройствам для измерения дифференциально-фазовых искажений телевизионного сигнала.

По основному авт. св. 9 748901 известно устройство для измерения дифференциально-фазовых искажений, содержащее последовательно соединенные полосовой фильтр, ограничитель, первый фазовый детектор, коммутатор, . фильтр нижних частот (ФЙЧ) и блок фиксации, при этом к выходу ограничи.теля подключены блок управления и последовательно соединенные инвертор и второй фазовый детектор, выход которого подключен к второму входу коМмутатора, с третьим входом которого соединен выход блока управления, а также кварцевый генератор„ выход которого подключен к вторым входам фазовых детекторов и блока управления.$1)25 с ,. С выхода блока фиксации сигнал, характеризующий дифференциально-фазовые искажения, подается на осциллограф,:с помощью которого произво,цится измерение величин Р„ и q .

Величина дифференциальной фазы определяется следующими соотношениями

Недостатком известного устройства является недостаточная точность измерения, ограниченная точностью осциллографических измерений, и необходимость измерения двух величин (. и (Р2) °

Цель изобретения — сокращение времени измерения и повышение его точности.

Поставленная цель достигается тем, что в устройство введены последовательно соединенные элемент ИЛИ, Qтриггер, интегратор и инвертирующий усилитель, а также первый и второй компараторы, первые входы которых подключены к выходу блока фиксации, а выходы — к входам элемента HFH, при этом второй вход первого компаратора подключен к выходу интегратора, а второй вход второго компаратора - к выходу инвертирующего усилителя, причем выход D-триггера соединен с его установочным входом, 1003382 а его синхронизирующий вход является вторым входом устройства.

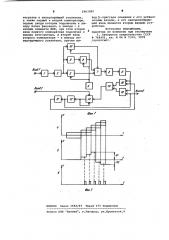

На фиг. 1 изображена блок-схеМа устройства для измерения дифференциально-фазовых искажений; на фиг.2 временные диаграммы. 5

Устройство для измерения дифференциально-фазовых искажений содержит полосовой фильтр 1, ограничитель 2, первый фазовый детектор 3, кварцевый генератор 4, фильтр 5 нижних частот, l0 блок 6 фиксации, коммутатор 7, второй фазовый детектор 8, инвертор 9, блок 10 управления, инвертирующий усилитель 11, интегратор 12, D -триггер 13, элемент ИЛИ 14, первый компа- (5 ратор 15 и второй компаратор 16.

Устройство работает следующим об- разом.

На вход устройства для измерения дифференциально-фазовых искажений

20 поступает измерительный сигнал 92 (фиг. ?a) . Полосовой фильтр 1 выде ляет напряжение цветовой поднесущей.

Через ограничитель 2 напряжение подается на первый и второй фазовые детекторы 3 и 8, имеющие характерис" тику, лйнейную в пределах от 0 до

360О, причем на второй фазовый детектор 8 сигнал подается через инвертор 9, в результате чего характеристики первого и второго фазовых детекторов 3 и 8 оказываются сдвинутыми относительно друг друга на 180 о

На другие входы первого и второго фазовых детекторов подается напряжение поднесущей частоты с автоном- З5 ного кварцевого генератора 4, частота которого равна частоте цветовой поднесущей.

Наличие двух фазовых детекторов позволяет устранить неоднозначность 40 отсчета при переходе рабочей точки от 360О к Оо. Это достигается подачей на коммутатор 7 сигналов с двух фазовых детекторов, характеристики которых сдвинуты на 180О относитель- 45 но друг друга, и коммутацией соответствующего фазового детектора на вход фильтра 5 нижних частот.

Управление коммутатором 7 осуществляется с помощью блока 10 управле- 50 ния. С выхода коммутатора сигнал про-. пускается через фильтр 5 нижних частот, под-авляющий частоту цветовой поднесущей и подается на блок 6 фиксации, обеспечивающий неподвижность характеристики дифференциальной фазы (фиг. 2 6), Интегратор 12 и инвертирующий усилитель 11 (с коэффициентом передачи К = -1) вырабатывают напряжения U „ и U, причем 0 1 -0>. Эти напряжейия подаются на первые входы 60 с первого и второго компараторов, на вторите входы которых подается сигнал, характеризующий дифференциальную фазу. Входы компараторов (инвертирующий и неинвертирующий) подключены . 65 б так, что на выходе первого компара тора 15 появляется уровень логической единицы, когда U 7Ч„ на каждой ступеньке сигнала (фиг. 26), а на выходе второго компаратора 16 появится уровень логической единицы, когда ! 02! >!Ч2!на каждой ступеньке сигнала (фиг, 26) . При этом, на выходе элемента ИЛИ 14, соединенного с входом

Э-триггера 13, появится .уровень логической единицы, который по сигналу (фиг. 2 8), поступающему с второго входа устройства для измерения диф-. ференциально-фазовьи искажений на синхронизирующий вход 9-триггера 13, будет записан в 9 -триггер 13. Уро-вень логической единицы с выхода 9триггера 13 поступает на вход интегратора 12, в результате чего выходные напряжения интегратора 12 и инвертирующего усилителя 11 будут уменьшаться по абсолютной величине.

Как только хоть одно из напряжений О.!, 02! станет меньше величины

91, (9 )хоть на од. ой из ступенек сйгнаяа (фиг. 2б), то на выходе элемента ИЛИ 14 появится уровень логического нуля, который запишется в

3-триггер 13. Уровень логического нуля с выхода 3 -триггера 13 приведет к увеличению напряжений U „ l02l

Для обеспечения фиксации D òðèããåðà

13 в нулевом состоянии его выход соединен с его установочным входом.

Устройство для измерения дифференциально-фазовых искажений придет в равйовесие, когда напряжение U < = (02I станет равным максимальному из значений Ч или le2l. Вследствие внутренних шумов или флуктуаций измеряемого сигнала в состоянии равновесия ,()-триггер поочередно будет переключаться иэ одного состояния в другое

На выходе интегратора 12 сформируется постоянное напряжение, равное величине дифференциальной фазы, которОе можно преобразовывать в цифровой код для дальнейшей автоматической обработки, в частности измерять с необходимой точностью цифровым вольтметром постоянного тока.

Исключение ручного труда, обусловленного осциллографическими измерениями, автоматизация процесса обработки результатов измерения позволяют повысить объективность и точность измерений и сократить его время.

Формула изобретения

Устройство для измерения дифференциально-фазовых искажений по авт.св.

9 748 901, о т л и ч а ю щ е е с я тем, что,с целью сокращения времени измерения и повышения его точности, в него введены последовательно сое диненные элемент ИЛИ, g -триггер, ин1003382

ВНИИПИ Заказ 1592/47 Тираж 675 Подписное

Филиал ППП "Патент", r.Óæãîðoä, ул.Проектная,4 тегратор и инвертирукиций усилитель, а также первый и второй компараторы, первые входы которых подключены к выходу блока фиксации, а выходы — к входам элемента ИЛИ, при этом второй вход первого компаратора подключен к выходу интегратора, а второй вход второго компаратора - к выходу инвертирукицего усилителя, причем выход Э -триггера соединен с его устано вочным входом, а его синхронизирующий вход является вторым входом устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 748901, кл. Н 04 N 7/02, 1976 (прототип). !