Импульсный регулятор

Иллюстрации

Показать всеРеферат

Союз Советсиик

Социалистичесиик

Республик

О П И С А Н И Е <,„ ооаввв

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕПЬСТВУ (61) Дополнительное к авт. сеид-ву (22) Заявлено 04,11.81 (2l ). 3354096/18-24 с присоединением заявки № (5!)М. Кл.

4 05 В 11/26

Гееуаарстееаее квинтет (23) Приоритет

Опубликовано 15.03.83. Бюллетень ¹ 10

Дата опубликования описания 15.03.83 ве девам кмеретекий к еткритий (53) УДК62-50(088.8) (72) Авторы изобретения

В. М, Лохин и В. В. Макаров (7I ) Заявитель (54) ИМПУЛЬСНЫЙ РЕГУЛЯТОР

Изобретейие относится к автоматическому управлению, а именно к автоматическим импульсным регуляторам, в которых выходной сигнал является прерывной импульсной функцией отклонения входного сигнала от заданной величины, и может быть применено в системах автоматического управления различными объектами, в которых обьект регулирования, исполнительное устройство и датчик регулируемой величины можно приближенно описать дифференциальным уравнением первого порядка, в частности при регулировании температуры с помощью различных электронагревательных устройств с высоким качеством регулирования.

Известен регулятор, содержащий датчик .регулируемой величины и задатчик, подключенные выходами к соответствую.щим входам первого формирователя сигнала управления, выход которого соединен с первым входом второго формирователя сигнала управления, второй вход которого через дифференциатор подключен к датчи-, 2 ку регулируемой величины, а выход - ко входу усилителя мощности, причем, если второй формирователь сигнала управления является пропорциональным звеном, то его функции может выполнять сумматор Pl ) .

Известен также импульсный регулятор, содержащий датчик регулируемой величины и задатчик, подключенные входами к первому сумматору, выход которого сое динен с первым входом второго суммато ра, выход которого через усилитель соединен с первым входом третьего сумматора и входом нелинейного корректирующего блока, выход которого через интегратор и переключатель соединен со вторым входом третьего сумматора, выход которого через трехпозиционный релейный блок подключен к управляющему входу переключателя и входу исполнительного механизма, выход которого через блок го местной обратной связи соединен со вторым входом второго сумматора (2) .

Недостатком известных регуляторов является их низкая точность.

2$

3$

40 величины и к входу дифференциатора, а выходом через последовательно соеди$0 пенные усилитель, интегратор, трехпозиционный релейный блок и второй с 4матор - к усилителю мощности, о т л ич а ю ш и и с я тем, что, с целью повышения точности регулятора, в нем ус.тановлены блок задержки и ключ, сигналь3

Наиболее близким к изобретению по технической сущности является импульс« ный. регулятор, содержащий первый сумматор, подключенный первым входом к выходу задатчика вторым входом - к выходу датчика регулируемой величины и к входу дифференциатора, а выходом чьрез последовательно соединенные усилитель, интегратор, трехпозииионный релейный блок и второй сумматоь - к усилителю мощности P8 j .

Недостатком данного регулятора является также его нйзкая точность.

Uemь изобретения — повышение точности регулятора.

Поставленная цель достигается тем, Я что в импульсном регуляторе установлены блок задержки и ключ, сигнальным входом подключенный к выходу дифференциатора, управляющим входом - к выходу трехпозиционного релейного блока и к входу блока задержки, а выходом - к второму входу второго сумматора, выход блока задержки соединен с управляющим входом интегратора.

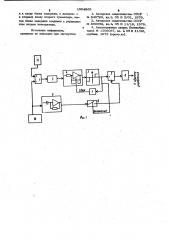

На фиг. 1 представлена функциональнея схема регулятора; на фиг. 2 - осциллограмма фазовых траекторий системы регулирования с предлагаемым регулятоPoM„

Регулятор включает первый и второй сумматоры 1 и 2, усилитель 3, интегратор 4, трехпозиционный релейный блок 5, . ключ 6, блок задержки 7, усилитель 8 мошности, дифференциатор 9, датчик 10 регулируемой величины, задатчик 11.

Соответственно фиг. 2 У и Х - входной и выходной сигналы интегратора, dкоэффициент, характеризующий достижение апериодического режима.

Блок задержки 7 в частном случае .может быть реализован с помощью реле времени.

Регулятор работает следующим образом.

Сигнал с выхода датчика 10 регулируемой величины поступает на вход дифференциатора 9 и второй вход первого сумматора 1, где сравнивается с сигналом задатчика 11, который поступает на первыйй вход сумматора 1. Выходной цигнал сумматора 1, равный разности между заданным и действительным значениями регулируемой величины, поступает на вход усилителя 3, Выходной сигнал усилителя 3 поступает на вход интегратора. Ири достижении выходным сигналом интегратора 4 порога срабатывания блока 5 последний срабатывает и подает сигнал на входы сумматора 2, блока задержки 7 и управляющий вход ключа 6. Сигнал с выхода сумматора 2 через усилитель мощности 8 поступает на выход регулятора. Ключ 6 lIQ сигна лу c блока 5 замыкается и подключает сигнал с выхода дифференциатора 9 ко второму входу второго сумматора 2. В этом случае (т.е. при наличии сигнала на выходе блока 5) в регуляторе формируется гибкая отрицательная обратная связь. По истечении заданной задержки времени, установленной в блоке задержки 7, выходной сигнал блока 5 осуществляет сброс интегратора 4 до нуля. При этом выходной сигнал интегратора 4 становится меньше порога срабатывания блока 5. Выходной сигнал блока 5 становится равным нулю и ключ 6 отключает выходной сигнал дифференциатора 9 от второго входа второго сумматОра.

Далее процесс повторяется до тех пор, пока значение сигнала на выходе сумматора не стает равным нулю.

Моделирование процесса работы регулятора позволяет установить, что точность работы регулятора повышается примерно в 100 раз по сравнению с известным устройством. На фиг. 2 приведена осциллограмма фазовых траекторий системы регулирования при использовании предлагаемого регулятора при параметрах:

К= 10, Тр= 1 с, f =0,2 с . ф= = 0,5 Вс.

Кроме того, замыкание гибкой отрицательной обратной связи в регуляторе приводит к устранению автоколебаний в регуляторе и повышению качества работы системы, в которой установлен предлагаемый регулятор.

Формула изобретейия

Импульсный регулятор, содержащий первый сумматор, подключенный первым входом к выходу задатчика, вторым входом — к выходу датчика регулируемой ным входом подключенный к выходу ди ференциатора, управляющим входом — к выходу трехпозиционного релейного блока

5 1ОО4969 ,и к входу блока задержки, а выходом 4 1 Ав торское свидетельство СССР ход блока заде жки торому входу второго сумматора, вы- № 840789 кл. G 0, кл. 5 В 5/01, 1979.

l ход . ка задержки соединен с п авляь . 2. Авторское свидетельство СССР пщм входом интегратора. ¹ 809058, кл. Q 05 В 11/16, 1979. принятые во внимание.при. экспертизе и ин рмаиии,, тании ¹1306067,,кл. 4 05В 1, кл. 11/26, ржзе опу . 1973 (прото;ип).

1004969

Составитель Г, Нефедова

Редактор М. Келемеш Техред >V,. Кастелевич Корректор Й. Рошко

Заказ 1893/60 Тираж 872 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

li3035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент, r. Ужгород, ул. Проектная, 4