Параллельный комбинационный сумматор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 101281 (2l) 3362033/18-24 с присоединением заявки ¹

Р М Кп з

G 06 Г 7/50

С 06 Р 11/16

Государственный комитет

СССР по делим изобретений и открытий (23) Приоритет—

Опубликовано 150383. Бюллетень ¹10

Дата опубликования описания 150383 (53) УДК 681. 325; .54(088.8) (72) Авторы изобретения

A.À. Чечин и М.В..Гоцаков 54) ПАРАЛЛЕЛЬНЫЙ КОМБИНАЦИОННЫЙ СУММАТОР

Изобретение относится к цифровой вычислительной технике и может применяться в вычислительных, специализированных и. управляющих устройствах, в частности в арифметических устрой- ствах различного назначения.

Известен параллельный комбинационный сумматор, содержащий триггеры, схему И переноса, схему И нечетности, входные элементы И, ИЛИ, схему несовпадения, схему свертки, схему И фиксации комбинаций, выходной элемент ИЛИ (1 ).

Недостатком устройства является плохая диагностируемость, выражающаяся в большом числе входных наборов, необходимых для полной диагностики .сумматора.

Наиболее близким к предлагаемому по технической сущности является па раллельный комбинационный сумматор, содержащий п одноразрядных сумматоров, элементы И и ИЛИ в. каждом разряде сумматора, четыре элемента И, элемент ИЛИ и элемент ИЛИ-НЕ (2 .

Недостатком устройства является неполнота проверки всего параллельного комбинационного сумматора. При .проверке не проверяются цепи переноса между разрядами сумматора.

Цель изобретения - увеличение полноты контроля сумматора.

Поставленная цель достигается тем, что в параллельный комбинационный сумматор, содержащий п одноразрядных сумматоров, первый элемент И и первый элемент ИЛИ в каждом разряде сумматора, второй и третий элементы И, второй элемент ИЛИ, первый элемент НЕ, элемент ИЛИ-НЕ, причем первый и второй входы и одноразрядных сумматоров подключены, к выходным шинам сумматора, вход переноса одноразрядного сумматора младшего разряда подключен к входной шине переноса, выходы переносов одноразрядных сумматоров соединены с первыми входами первых элементов И соответствующих разрядов сумматора, выходы которых соединены с первыми входами первых элементов ИЛИ, выходы которых связаны с входами переноса соответствующих одноразрядных сумматоров всех разрядов, кроме старшего, первые входы первых элементов И всем разрядов соединены с соответствую-. щими входами третьего элемента И и элемента ИЛИ-НЕ, выходы третьего .

30 элемента И и элемента ИЛИ-НЕ подклк1005038 мента ИЛИ 4 старшего разряда. Выход первого элемента ИЛИ 4 старшего раз ряда является выходом сумматора.

Устройство работает следующим образом. для полной проверки предлагаемо" го сумматора необходимо подавать на входы 2 входных наборов (два информационных входа и один вход переноса младшего разряда) . Коды входных наборов и результаты суммирования представлены в таблице.

Номер Р;. набора

0 0

1 1

0 1

1 0

0 1

1 0

0 0

1 б

ЗО

Примечание:

Х1У - слагаемые i-ro разряда;

P,51 â перенос н сумма j-го сумма". тора;

Р- „ — перенос в последующий разряд

1+1 (3 + 1) -го сумматора.

Из таблицы следует, что при входных наборах Р О, 1, 2, 5, б, 7 связи переноса между сумматорами разрывать не требуется, так как в этом случае коды Р- и Р„ совпадают, а в .наборах Р 3 и 4 значения P и Р + проти воположны. Поэтому для набора Р 3 требуется запретить формирование переноса в последующих разрядах, а для набора Р 4 — ввести перенос во всех разрядах сумматора.

В предлагаемом сумматоре при подаче на шину 3 логического "0" и поступлении входного набора 9 3 на выходе элемента ИЛИ 14 формируется

".0", который запрещает прохождение переноса во все::последующие разряды сумматора, а при входном наборе 9 4 (вход переноса младшего разряда равен "1", входы слагаемых соответствуют логическим "0") на выходе элемента И появляется "1", которая формирует сигнал переноса во всех последующих разрядах сумматора. B реэультате введения элементов ИЛИ 14, НЕ 15 и 16, И 17 íà всех входах печены соответственно к первому Ъ вто рому входам второго элемента ИЛИ, выход которого соединен с первым входом второго элемента И, второй вход .которого связан с выходом первого элемента НЕ, вход которого сое- 5 динен с вторым входом первого элемента И старшего разряда, введены второй и третий элементы HE четвертый элемент И и третий элемент

ИЛИ, причем входы второго и третьего элементов НЕ подключены соответственно к первому и второму входам одно-. разрядного сумматора младшего разряда, выходы второго и третьего элементов HE соединены с первым и вторым 15 входами четвертого элемента И соответственно, третий вход которого свя-. зан с входом переноса одноразрядного сумматора младшего разряда и первым входом третьего элемента ИЛИ, выход которого соединен с вторыми входами первых элементов И всех разрядов, кроме старшего, второй вход третьего . элемента ИЛИ подключен к управляющему входу сумматора и входу первого элемента НЕ, выход четвертого элемента

И соединен.с вторым входом первого элемента ИЛИ младшего разряда сумматора.

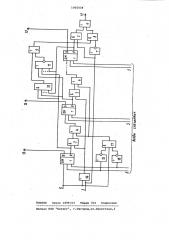

На чертеже приведена структурная схема параллельного комбинационного сумматора.

Устройство содержит и одноразрядных сумматоров 1, первый элемент И 2 в каждом разряде сумматора, вход 3 управления переносом, первый элемент

ИЛИ 4 в каждом разряде сумматора, информационные входы 5 слагаемых, вход 6 переноса, первый элемент НЕ 7., второй элемент H 8, второй элемент

ИЛИ 9, третий элемент И 10, элемент .Щ

ИЛИ-HE 11, выход 12 обнаружения ошибки, выход 13 сумм, третий элемент

ИЛИ 14,второй и третий элементы HE 15 и 16, четвертый элемент И 17.

Вход б переноса соединен с входом 45 переноса младшего разряда сумматора

1, а также с первым входом третьего элемента ИЛИ 14 и с одним из входов четвертого элемента И 17, к двум другим входам которого через второй и третий элементы HE 15 и 16 подключены входы слагаемых одного иэ -разрядов сумматора. Управляющий вход 3 со-. единен с вторым входом третьего элемента ИЛИ 14, вторым входом первого элемента И 2 старшего разряда и входом первого элемента НЕ 7,выход котоpord соединен с вторым входом второго элемента И 8.

Выходы третьего элемента И 10 и элемента ИЛИ-НЕ 11 соединены соответ-60 ственно с первым и вторым входами второго элемента ИЛИ 9, выход которой соединен с первым входом второ го элемента И 8, выход которого сое;. динен с вторым входом первого эле1005038 реносов сумматоров формируются одни и те же коды числа в соответствии с номером входного набора.

Проверка всего комбинационного сумматора происходит при подаче на вход 3 логического "0" и поочередной подаче на его информационные входы всех кодов набрров. При этом элементы .И 10 и ИЛИ-НЕ 11 фиксируют равенство выходных значений переносов всех одноразрядных сумматоров. Если пере- 10 носы должны быть равны "0", то на выходе элемента И 10 имеется "0", а на выходе элемента ИЛИ-НЕ 11- — "1".

Эта единица через элементы ИЛИ 9,И 8 и ИЛИ 4 появляется на выходе 12 сум- 15 матора. В случае, если на одном или нескольких выходах переносов сумматоров сигнал не равен "0", то на выходе

12 сумматора появляется "0". Таким образом, устанавливается ошибка в 20 формировании переносов. Аналогично, если на всех выходах одноразрядных сумматоров должна быть логическая

"1", на выходе элемента ИЛИ-НЕ 11 присутствует "0", а на выходе эле- g5. мента И 10 — сигнал "1", который тоже появляется на выходе 12. Если имеет место ошибка в каких-то разря,дах, то на выходе элемента И- 10, а следовательно, и на выходе 12, находится логический "0". Таким образом, обнаруживается ошибка. Ошибки при формировании сумм обнаруживаются на выходах 13 сумм одноразрядных сумматоров. g

Итак, в результате подачи 2 вход-.. З5 ных наборов обнаруживаются все ошибки при формировании переноса в одноразрядных комбинационных сумматорах, межсумматорных цепях переноса и при формировании сумм в одноразрядных сум40 маторах.

Таким образом, если принять, что для построения одного .разряда сумматора требуется 8 элементов типа И, ИЛИ, НЕ, то при введении дополнитель 45 ных элементов сложность всего сумматора увеличивается при длине суммато» ра.,равного одному байту,на 3,4Ъ,а при количестве разрядов в 2 байта — на

L,8Ъ.При этом повышается достовер- . ность обработки информации за счет обнаружения отказов и исключения ра боты такого сумматора в случае наличия отказов. Количество входных набо-: ,ров остается прежним.

55 . Формула изобретения

Параллельный комбинационный сумматор, содержащий п одноразрядных сумматоров, первый элемент И и первый элемент ИЛИ в каждом разряде сумматора, второй и третий элементы И, второй элемент ИЛИ, первый элемент HE элемент ИЛИ-НЕ, причем первый и второй входы и одноразрядных сумматоров подключены к выходным шинам сумматора, вход переноса одноразрядного сумматора младшего разряда подключен к входной шине переноса, выходы переносов одноразрядных сумматоров соединены с первыми .входами первых элементов И соответствующих разрядов сумматора, выходы которых соединены с первыми входами первых элементов. ИЛИ, выходы которых связаны с входами переноса соответствующих одноразрядных сумматоров всех разрядов, кроме старшего, первые входы первых элементов И всех разрядов соединены с соответствующими входами третьего элемента И и элемента ИЛИ-НЕ, выходы третьего элемента И и элемента ИЛИ-НЕ подключены соответтвенно к первому и второму входам второго элемента ИЛИ, выход которого соединен с первым входом второго элемента И, второй вход которого связан с выходом первого элемента НЕ, вход которого соединен с вторым входом первого элемента И старшего разряда, отличающийся тем, что, с целью увеличения полноты контроля, в.устройство введены второй и третий элементы НЕ, четвертый элемент И и третий элемент ИЛИ, причем входы второго и третьего элементов НЕ подключены соответственно к первому и второму входам одноразрядного сумматора младшего разряда, выходы второ го и третьего элементов НЕ соединены с первым и вторым входами четвертого элемента И соответственно, третий вход которого связан с входом переноса одноразрядного сумматора младшего разряда и первым входом третьего элемента ИЛИ, выход третьего элемента

ИЛИ соединен с вторыми входами первых элементов И всех разрядов, кроме старшего, второй вход третьего элемента ИЛЙ подключен к управляющему входу сумматора и входу первого элемента НЕ, выход четвертого элемента И соединен с вторым входом первого эле.-. мента ИЛИ младшего разряда сумматора.

Источники информации, принятые во внимание при экспертизе.

1. Авторское. свидетельство СССР

9 354413 кл. G -06 F 7/50, 1970.

2. Авторское свидетельство СССР

У 696477, кл, G 06 F 7/50, 1979.

1005038

ВНИИПИ Заказ 1899/63 Тираж 704 Подписное

Филиал ППП "Патент", г.Ужгород,ул.Проектная,4