Синусно-косинусный преобразователь

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических республик рц 1 005040 (61) Дополнительное к авт. свид-ву— (И1И. Нл.з (22) Заявлено 21.0881 (21) 3327543/18-24 сприсоединениемзаявки ¹â€” (23) Приоритет—

0 06 Г 7/548

Государстаеииый комитет

СССР ио делам изобретений и открытий

Опубликовано 15.0383..Бюллетень Но 10 (53)УДК 881.325 (088. 8) Дата опубликования описания 15. 03. 83 (72) Авторы изобретения

Е.Ф.Киселев и О.A.Êóçèíà (71) Заявитель (54) СИНУСНО-КОСИНУСНЫЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к вычислительной технике и предназначено для воспроизведения функций синуса и косинуса по аргументу, представленному параллельным кодом, и может быть использовано в специализированных вычислителях с высоким быстродействием.

Известен вычислитель функции сину-. са и косинуса, содержащий генератор импульсов, регистр аргумента, блок управления, блок вычисления старших разрядов функций накапливающий сумматор, два блока умножения и два регистра результата.

Преобразователь выполняет преобразование параллельного кода 4- ар.л . л гумента 4 в коды в1п в и cos ck на основе формул дифференциального исчисления

9тпcL =91tl (/5+Я )%за ф+ ф СОЭ f6р

Cesd =Соз,ф+У}сизP-4I МпР, л л л;л (q)

1.гдери у — коды, образованные старшими и младшими разрядами кода oL соответственно t17.

Недостатком этого преобразователя является относительно низкое быстродействие, обусловленное фор.лл .п мнрованием кодов siï f3и cos f5 за л время развертки кода р от 0 до максимального значения.

Наиболее близким к изобретению является синусно-косинусное устройство таблично-алгоритмичного типа, содержащее блок памяти, четыре множительных устройства, два сумматора Г27Недостатком этого устройства является относительно низкое быстродействие, так как оно содержит четы" ре множительных устройства, которые

15 значительно увеличивают время получения результата.

Цель изобретения — повышение быстродействия преобразователя.

Поставленная цель достигается тем, что в синусно-косинусный преобразователь, содержащий блок памяти, выходы старших разрядов кодов синуса и косинуса которого подключены к вхо" дам первых сомножителей первого и второго умножителей и входа старших разрядов первых слагаемых первого и второго сумматора соответственно, выходы младших разрядов кодов синуса и .косинуса блока памяти соединены с входами младших разрядов первых сла.

1005040 гаемых первого и второго сумматоров, выходы которых являются информационными выходами кодов синуса и косинуса преобразователя, вход второго слагаемого первого сумматора соединен с выхоцом второгЬ умножителя, дополнительно введены анализатор кода, комбинационный умножитель, блок элементов НЕ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, вход первого старшего разряда аргумента преобразователя является выходом знакового разряда кода синуса преобразователя и соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является выходом знакового разряда кода косинуса преобразо-15 вателя, вход второго старшего разряда аргумента преобразователя соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и первым входом анализатора кода, второй вход которого 20 подключен к входу младших разрядов аргумента преобразователя, выход старших разрядов анализатора кода соединен с входом блока памяти„ выход младших разрядов анализатора 25 кода соединен с входом умножителя, выход которого подключен к входам опорных сомножителей первого и второго умножителей, выход первого умйожителя соединен"с входом блока элементов НЕ, .выход которого подключен к входу второго слагаемого второго сумматора.

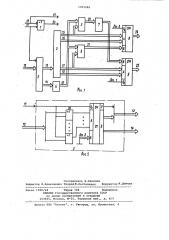

На фиг. 1 приведена структурная схсма синусно-косинусного преобразователя; на фиг. 2 — функциональная схема анализатора кода.

Устройство содержит элемент

ИСКЛЮЧАЮЩЕЕ ИЛИ 1, анализатор 2 кода, блок 3 памяти, комбинационный умножитель 4, умножители 5 и б, блок элементов HE 7, сумматоры 8 и 9, входы 10 и 11 старших и кодовый вход 45

12 младших разрядов кода аргумента, выходы 13 и 14 старших и младших разрядов кода анализатора 2 с ответственно, кодовые выходы 15 — 18 блока

3 памяти, кодовый выход 19 комбина- 50 ционного умножителя 4, кодовые выходы 20 и 21 умножителей 5 и б соогветственно, выходы 22 и 23 зна- . ковых разрядов кодов синуса и косинуса соответственно и выходы 24 и 55

25 кодов синуса и косинуса преобразователя соответственно. Анализатор 2 кода содержит группу 26 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 6Î и сумматор 27.

Предлагаемый преобразователь вырабатывает по (и + 2)-разрядному коду î- agryMejjra o(.(h+ 1) разрядные .п п коды синуса и косинуса s in u cosoL. 65 п

Код с и аргумент а связаны соотношением и+2 (=гх Е .(, р-, 1=1 где с ; — разрядная цифра i-го раз ряда кода 6б

Два старших разряда кода с определяют знаковые разряды кодов п n s i и оС и cos cL в соответствии с выражениями:

Ф22 = oj.1, Ф23 = с(.1 О+о(.2, где Ф22, Ф23 — знаковые разряды коп

-дов 5 i n oj-u co s с(. соответственно.

Анализатор 2 кода выдает при

72 = 0 прямой код (при 2=1 — дополнительный код ) по коду, образованному в младшими разрядами вход.ного кода аргумента.

Блок 3 памяти комбинационно вырабатывает и -разрядные коды sin p и и и cos р по коду р, образованному старшими разрядами выходного кода анализатора 2. младшие (m-1) разрядов выходного кода анализатора 2 образуют код соответствующий аргументу ! f = 1jI 2Å у; 2 . Для представления а р-

1=п.-тиФ2 и гумента г кодом у в радианах с весом младшего разряда ау"= 2 служит комбинационный умножитель 4, .реализующий операцию % — lj/g

Умножители 5 и 6 формируют и-разрядные коды произведений m-разряднсго кода у» на коды s in tt> и cos»p, /\» .п» образованнйе старшими m разрядами .п кодов s in p и соя р соответственно. п

Усечение кодов s i np u cos p при умножении применяется для упрощения реализации умножителей 5 и б. При

2 m > п погрешность умножения не превышает величиныау > н= 2

-П

Преобразование кода 2 в коды .п п

Isinol l u icos d. осуществляется на основе соотношений ! ! 51 и cL I:- û ï p + я " c os p, I cos а" I = cos pj- " g i »р. (С подачей двух старших разрядов кода Ж по входам 10 и 11 и остальных его разрядов по входу 12 преобразователя блок 3 памяти на выходах

15 и 16 вырабатывает код sin ,и поступающий на входы первого слагаемого сумматора .8, а на выходах 17

n и 18 — код cos р, поступающий на входы первого слагаемого сумматора 9.

1005040

Умножитель 6 формирует на выл» ходе 21 код г . cos$, подаваемый на входы второго слагаемого сумматора 8, а умножитель 5 на выходе 20 вырабатывает код ф"-sin Ъ, .поступаю.т щий через блок элементов ЙЕ 7 обрат- . ным кодом на входы-второго слагае мого суюеатора 9, на вход переноса которого подается логическая "1".

С выходов 24 и 25 суммато >ов 8 и

9 снимаются искомые коды !з î l

lcosct.l соответственно, а с выхо-. дов 22 и 23 - знаковые разряды,кодов синуса и косинуса соответственно.

Преобразователь работает как комбинационная логическая схема, быстродействие которой определяется временем -распространения сигнала от ее входов до выходов, т.е. быстродействием применяемой элементной ба-. 20 зы.

Технико-экономическая эффективность изобретения заключается в том> что предлагаемый преобразователь.имеет по сравнению с прототипом более 25 высокое быстродействие.

Формула изобретения

Синусно-косинусный преобразОватель, содержащий блок памяти, выходы старших разрядов кодов синуса и косинуса которого подключены к входам первых сомножителей первого и второ- 35 го умножителей и входам старших разрядов первых слагаемых первого и второго сумматоров соответственно, выходы младших разрядов кодов синуса и косинуса блока памяти соединены с входами мпадших разрядов первых сла- 40 гаемых первого и второго сумматоров, выходы которых являются информациои ными выходами кодов синуса и косинуса преобразователя, вход второго слагаемого первого сумматора соединен с выходом второго умножителя, о тл и ч а ю шийся тем, что, с целью повиаения быстродействия, в него дополнительно введены анализатор кода, комбинационный умножитель, блок элементов НЕ и элемент

ИСКЛЮЧАЮЩЕЕ ИЛИ, вход первого старшего разряда аргумента преобразователя является выходом знакового разряда кода синуса преобразователя и соединен с первым входом элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является выходом знакового разряда кода косинуса преобразователя, вход .второго старшего разряда аргумента преобразователя соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и первым входом анализатора кода, второй вход которого подключен. к .входу младших разрядов аргумента преобразователя, выход старших разрядов анализатора кода соединен с входом блока памяти, выход младших разрядов анализатора кода соединен с вхо-. дом умножителя, выход которого подключен к входам опорных сомножителей первого и второго умножителей, выход первого умножителя соединен. с входом блока элементов НЕ, выход которого подключен. к входу второго слагаемого второго сумматора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 628491, кл. С 06 F 7/548, 1976.

2. Оранский A.М. Аппаратные методы в цифровой вычислительной технике.

Минск, из-во БГУ им. В.И.Ленина, 1977,. с. 47-50 (прототип).

Ф..г

Составитель Е.Киселев

Редактор Л.Алексеенко ТехредЖ.Кастелевич Корректор М.де

Заказ 1900/64 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Ъ

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4