Мажоритарное декодирующее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ 1005059

ИЗ О БР ТЕпИЯ

Союз Советских

Социалистических

Республик ф

» .. .Ф» .

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявле но 12.02.81 (21) 3250757/18-24 (53) М.Rtl.з

G 06 F 11/08

Н 04 L 1/10 с присоединением заявки ¹â€” (23) ПриоритетГосударственный «омнтет

СССР по делам изобретений и открытий

f 53) УДК 681. 325 (088.8)

Опубликовано 15.0383. Бюллетень ¹ 10

Дата опубликования описания 15 ° 03.83 а

«1

Г.С. Евсеев, E.A. Крук и М.Л. Миневич . с

1 . :;., q„

;с . gA!

1 (72) Авторы изобретения (71) Заявитель (54) МАЖОРИТАРНОЕ ДЕКОДИРУКМЦЕЕ УСТРОЙСТВО

Изобретение относится к импульсной технике и может быть использовано в аппаратуре передачи данных.

Известно устройство для мажоритарного декодирования, содержащее регистр сдвига., выходы соответствующих разрядов которого соединены через сумматоры по вод 2 с входами первого мажоритарного элемента и через вторые сумматоры .по mod 2 с соответствующими входами второго мажоритарного элемента, выход первого мажоритарного элемента через второй регистр соединен с входами вторых сумматоров rio mod 2 ).1).

Недостаток устройства — сложность реализации.

Наиболее близким к изобретению является устройство для мажоритарного декодирования циклических кодов, содержащее последовательно соединенные первый элемент ИЛИ, регистр сдвига, блок сумматоров, мажоритарный элемент, первый ключ, элемент

HE-И, счетчик исправлений и второй элемент ИЛИ, а-также счетчик сдвига, второй ключ и последовательно соединенные сумматор, вычислитель синдрома и блок определения веса синдрома, выход которого подключен к вто, рому входу второго элемента ИЛИ; при этом выходы счетчика сдвига подключе ны соответственно к вторым входам первого ключа и второго ключа, первый выход которого объединен с первым входом сумматора, к второму -входу которого, а также к соответствующим входам вычислителя синдрома подключен выход вычислителя синдрома, причем соответствующий выход регистра сдвига подключен к входу первого элемента ИЛИ, к соответствующему входу мажоритарного элемента и к второму входу элемента НЕ-И 1 2).

15 Недостаток известного устройства заключается в малой достоверности декодирования из-за невозможности полностью реализовать кодовое расстояние

d> 2to+1 циклического кода путем исправления всех ошибок кратностью до Цель изобретения - повышение правильности декодирования за счет увеличения кратности исправляемых ошибок °

- Поставленная цель достигается тем, что в мажоритарное декодирукщее устройство, содержащее первый элемент

ИЛИ, выход .которого соединен с входом регистра сдвига, разрядные выходы которого соединены через блок сумма1005059!

О дом первого сумматора, а потенциональЗО

40.45

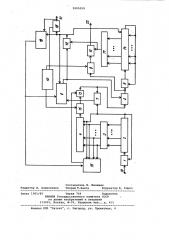

ИЛИ 1, регистр 2 сдвига, блок сумматоров 3, мажоритарный элемент 4, первый ключ 5, первый суммаТор 6, элемент НЕ-И 7, второй ключ 8, счетчик

9 исправлений, счетчик 10 сдвигов, третий ключ 11, второй элемент ИЛИ 12 второй сумматор 13, вычислитель 14 синдрома, четвертый ключ 15, пятый. ключ 16, определитель 17 веса синдрома, элемент 18 памяти, дешифратор

19, вход 20 устройства, выходы 21 и

22 устройства, Принцип работы устройства заключается в следующем. 60

Во всех случаях, когда вместо

2г0+1 необходимых проверочных соотношейий удается найти только 2t -1 .таких соотношений, ошибки кратности to в прототипе не исправляются, причем торов с входами мажоритарного элемента, выход последнего разряда соединен с вторым входом первого элемента ИЛИ и входом элемента НЕ-И, выход которого через счетчик исправлений соединен с входом второго элемента ИЛИ и с управляющим входом первого ключа, выход которого соединен с входом второго ключа и через первый сумма;тор — с входом вычислителя синдрома, общий выход которого соединен с его входами суммирования и с вторым вхоные выходы через определитель веса синдрома — с вторым входом второго элемента ИЛИ и с управляющим входом третьего ключа, вход которого соединен с выходом второго ключа, и счетчик сдвигов, выходы которого соединены с управляющими входами второго и четвертого ключей, вход последнего соединен с выходом мажоритарного элемента, введены дешифратор, элемент памяти, второй сумматор и пятый ключ, при этом входы дешифратора соединены с разрядными выходами блока сумматоров и с выходом последнего разряда регистра сдвига, а выход соединен с первым входом второго сумматора, второй вход которого соединен с выходом четвертого ключа, а выход — с .входом первого ключа и с вторым входом элемента НЕ-И, третий выход счетчика сдвигов соединен с управляющим входом пятого ключа, выход которого соединен с вторьпл входом элемента памяти, выход которого соединен с вторыми входами дешифратора и счетчика исправлений, выход второго .элемента ИЛИ соединен с входами элемента памяти, пятого ключа и с дополнительными входами определителя веса синдрома, вычислителя сидрома и счетчика исправлений.

На чертеже .представлена структурная блок-схема мажоритарного декодирующего устройства.

Устройство содержит первый элемент

25 ошибочное решение выносится мажоритарньм элементом всегда со счетом я :(t 1). Это обстоятельство используется для исправления ошибок кратностью t, в предлагаемом устройстве, Существо заключается в том, что если действительное число ошибок составляет t -1 или меньше, то они правильно исправляются декодером, поскольку для этого достаточно 2t

1 проверочных соотношений. Если же число ошибок составляет о и декодирование производится неверно, то при повторном декодировании можно выявить соотношение входов t :(t -1 j и в этих случаях произвести йнвертирование выхода мажоритарного элемента, поскольку известно, что в эти моменты он принимает неверное решение.

Тем самым исправляются ошибки кратности t0 °

Устройство работает следующим образом.

Принятая последовательность с входа 20 через элемент ИЛИ 1 поступает на вход регистра 2 сдвига и в течение и тактов записывается в него. В процессе записи ключи 5 и 15 закрыты и сигналов не пропускают. Момент окончания записи фиксируется счетчиком

10 сдвигов, который подает разрешающий сигнал на вход ключа 5.

В течение следующих и тактов происходит мажоритарное декодирование этой последовательности: при каждом сдвиге в регистре 2 сдвига мажоритарный элемент 4 выносит решение о значении символа, находящегося в крайней правой ячейке регистра 2 сдвига, и результат решения записывает через ключ 5 и сумматор 6, ключ 8 и сумматор 13 в вычислитель 14 синдрома.

При этом дешифратор 19 не работает и никаких сигналов на сумматор 6 не подает, поскольку на него не подан разрешающий сигнал с элемента 18 памяти. Одновременно сигналы с выхода регистра 2 сдвига и с выхода сумматора 6 поступают на элемент

HE-И 7, который выдает на вход счетчика 9 исправлений сигнал каждый раз, когда сигналы на его входах не совпадают, т.е. когда мажоритарный элемент

4 произвел исправление в символе.

Таким образом, после окончания и тактов декодирования в регистре 2 сдвига оказывается записанной вновь исходная последовательность, в счетчике 9 исправлений хранится число произведенных исправлений, а в определителе 17 веса синдрома - вес синдрома продекодированной последовательности.

Если число исправлений меньше с и вес синдрома равен О, зто означает, что продекодированную последовательность можно выдавать потребителю—

1005059 в течение следующих. и тактов вновь происходит процесс декодирования и с каждым тактом декодированная информация через ключ 5, сумматор б и открытые ключи 8,15 и 16 поступает на выход 22.

Если либо число исправлений больше с, либо вес синдрома больше О, сигнал об этом через элемент ИЛИ 12 поступает на вход элемента 18 памяти (например, триггер) и переводит его в единичное состояние, Одновременно этим сигналом обнуляется счетчик 9 исправлений, определитель 17 веса синдрома и вычислитель 14 синдрома. Через ключ 11 этот. 15 сигнал не проходит, поскольку на него не подан разрешающий сигнал со счетчика 10 сдвигов. Сигнал с элемента 18 памяти разрешает работу дешифратора 19 и меняет порог в счет- gp чике 9 с t на с, т.е. сигнал на выходе счетчика 9 теперь появляется только если число исправлений не равно t (поскольку не было возможности декодировать принятую последовательность в предположении, что число ошибок меньше tot теперь производится попытка это сделать, предполагая, что их число точно равно с ).

Повторный процесс декодирования произ водится аналогичным образом, однако теперь элемент 18 памяти своим сигналом разрешает работу дешифратора

19, который выявляет все те моменты, когда решение в мажоритарном элементе35

4 принимается при соотношении входов с .(с -1) и при каждом таком случае о 0 подает сигнал на сумматор б, меняя знак решения на обратный. !

Вновь производится процесс деко40 дирования уже с использованием сиг- налов дешифратора 19. Если число исправлений не больше с и вес синдрома не больше О, ключи 8 и 16 открыты и в течение следующих и тактов 45 при повторном процессе декодирования информация выдается потребйтелю.

Затем сигналом со счетчика 10 сдвигов элемент 18 памяти обнуляется.

Если же число исправлений больше 50 с или вес синдрома больше О, сигнал о с элемента ИЛИ 12 через открытый к этому моменту ключ 11 поступает на выход 21 в виде сигнала об обнаружении ошибки, одновременно обнуляя 55 элемент 18 памяти.

Таким образом, мажоритарное деко дирующее устройство позволяет повысить достоверность принимаемой ин- 60 формации путем увеличения на 1 максимальной кратности исправления ошибок.

Формула изобретения

Мажоритарное декодирующее устройство, содержащее первый элемент ИЛИ, выход которого соединен с входом регистра сдвига, разрядные выходы ко- торого соединены через блок сумматоров с входами мажоритарного элемента, выход последнего разряда соединен с вторым входом первого элемента

ИЛИ и входом элемента НЕ-И, выход которого через счетчик исправлений соединен с входом второго элемента

ИЛИ и с управляющим входом первого ключа, выход которого соединен с входом второго ключа и через первый сумматор — с входом вычитателя синдрома, общий выход которого соединен с его входами суммирования и вторым входом первого сумматора, а потенциональные выходы через определитель веса синдрома — с вторым входом второго элемента ИЛИ и с управляющим входом третьего ключа, вход которого соединен- с выходом второго ключа, и счетчик сдвигов, выходы которого соединены с управляющими входами второго и четвертого. ключей, вход последнего из которых соединен с выходом мажоритарного элемента, о тл и ч а ю щ е е с я тем, что, с целью повышения правильности декодирования за счет увеличения кратнос-ти исправляемых ошибок, в него вве 1ены дешифратор, элемент памяти, вто-рой сумматор и пятый ключ, при этом входы дешифратора соединены с разрядными выходами блока сумматоров и с входом последнего разряда регистра сдвига, а выход соединен с первым входом второго сумматора, второй вход которого соединен с выходом четвертого ключа, а выход — с входом первого ключа и с вторым входом элемента НЕ-И, третий выход счетчика сдвигов соединен с управляющим входом пятого ключа, выход которого соединен с вторым входом элемента памяти, выход которого соединен с вторыми входами дешифратора и счетчика исправлений, выход второго элемента ИЛИ соединен зходами элемента памяти, пятого ключа и с дополнительными входами определения веса синдрома, вычислителя синдрома и счетчика исправлений.

Источники информации, принятые во внимание при экспертизе

1. Колесник В.Д., Иирончиков Е.Т.

Декодирование циклических кодов. И., "Связь",, 1965.

2 ° Декодирование двоичных групповых кодов, перспективных для информационных каналов современных радиотехнических систем. Обзор, вып. 41, 1967, ИРП (прототип) .

1005059

Составитель M. Миневич

Техред T. Фанта Корректор Е. Рсшко

Редактор Л. Алексеенко

Заказ 1901/65 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4