Устройство для контроля цифровых узлов

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ .СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик р111005061 (63) Дополнительное к авт. свид-ву (22) Заявлено 28.08.81 (21) 3328015/18-24 (И) М. КпР

6 06 F 11/16 с присоединением заявки №

Государственный комитет

СССР оо делам изобретений и открытий (23) Приоритет Опубликовано 1503.83. Бюллетень ¹ 10 (Щ УДК 681. 326 (088.8).

Дата опубликования. описания 15. 03. 83 (72) Авторы изобретения

В.М. (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ

УЗЛОВ »2

Изобретение относится к цифровой вычислительной технике, в частности к устройствам для проверки узлов цифровых вычислительных машин, например микросхем.

Известно устройство для контроля цифровых узлов, содержащее генератор импульсов, двоичный счетчик, элемент

И, эталонную микросхему, индикаторы, блок сравнения, ключ установки в исходное состояние 1).

Недостатком этого устройства является то, что íà входы проверяемой и эталонной микросхем подаются кодовые комбинации, определяеьвте всеми состояниями двоичного счетчика, хотя среди них имеются запрещенные состояния.

Наиболее близким к предлагаемому по технической сущности является устройство для контроля цифровых узлов, содержащее генератор импульсов, двоичный счетчик, элемент И, эталонную микросхему, индикаторы, блок сравнения, ключ установки в исходное состояние, генератор одиночного им- . пульса, ключ одиночного шага, блок исключения запрещенных состояний, два элемента ИЛИ 2).

Однако в данном устройстве на. вход проверяемой и эталонной микросхем также подаются кодовые комбинации двоичного счетчика, среди которых имеются и запрещенные. Если в проверяемой микросхеме имеются RS-триггеры, то после подачи на входы к и запрещенных комбинаций триггеры переходят в неоднозначные состояния, определяемые только асимметрией их схем. . Это может привести к тому, -что в результате подачи запрещенных входных сигналов, триггеры проверяемой и эталонной микросхем устанавливаются в различные состояния, после чего дальнейшая проверка микросхем. становится недостоверной. В известном устройстве блок. исключения запрещенных состояний только маскирует сигнал с блока сравнения при подаче на входы проверяемой и -эталонной микросхем запрещенных комбинаций, т.е. данное устройство не позволяет осуществлять достоверный контроль схем с RS -триггерами.

Цель изобретения - повьхаение достоверности контроля.

Поставленная цель достигается тем, что в устройство для контроля цифровых узлов, содержащее счетчик, эта1005061 лонный узел, генератор импульсов, генератор одиночного импульса, первый элемент И, элемент ИЛИ, два переключателя, три блока индикации, блок срав° .нения запрещенных состояний, причем выходы счетчика соединены соответственно с входами блока:исключения запрещенных состояний, вход генератора одиночного импульсачерез первыйпереключатель соединен с шиной положительного потенциала,выходгенератора одиноч- 0 ного импульсасоединен с первымвходом элемента ИЛИ, второй вход которого соеди нен с выходом первого элемента И, выход. элемента ИЛИ связан со счетным входом счетчика, установочные входы счетчи- l5 ка, эталонного узла и проверяемого узла подключены через второй переключатель к шине положительного потенцила, выходы проверяемого узла соединены сопервой группой входов блока . 20 сравнения и с входами первого блока индикации, выходы эталонного узла соединены с второй группой входов блока сравнения и с входами второго блока индикации, выход блока сравнения подключен к первому входу первого элемента И, второй вход кото-, рого соединен с выходом генератора импульсов, введены регистр, элемент

НЕ, второй элемент И, выход которого соединен с управляющим входом регистра, установочный вход которого соединен с установочным входом счетчика, а информационные входы регистра соединены с .выходами счетчика, выходы регистра соединены соответственно с входами проверяемого узла, с входами эталонного узла, с входами третьего блока индикации, выход блока исключения запрещенных состояний соединен со входом элемента НЕ, выход которого соединен с первым входом второго элемента. И, второй вход которого соединен с выходом генератора импульсов.

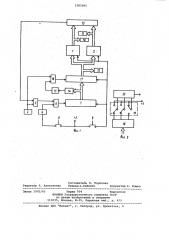

На фиг. 1 представлена схема устройства, на фиг. 2 - схема блока исключения запрещенных состояний.

Устройство содержит проверяемый 1 и эталонный 2 цифровые узлы, генератор 3 импульсов, генератор 4 одиночного импульса, элемент И 5, элеМент ИЛИ 6, счетчик 7, первый переключатель 8, второй переключатель 9, блоки 10, 11 и 12 индикации, блок 13 сравнения блок 14 исключения запрещенных состояний, элемент НЕ 15, элемент И 16, регистр 17.

Блок исключения запрещенных состояний (фиг. 2) состоит из дешифратора:

18, переключателей 19 и элемента (0

ИЛИ 20.

Проверка цифрового узла начинается с включения переключателя 9. При этом происходит сброс счетчика 7, регистра 17, провер., - зго 1 и эталон-Я ного 2 узлов в начальное состояние.

Блок 10 индикации показывает нулевое состояние, соответствующее комбинации логических уровней, поданных на входы узлов 1 и 2.

Если при этом на входах узлов 1 и 2 одинаковые комбинации логических уровней, то блоки 12 и 11 индикации показывают одинаковые числа, а блок

13 сравнения выдает на вход элемента

И 5 разрешающий сигнал и очередной импульс с генератора 3 проходит через элемент ИЛИ б на вход счетчика 7. По переднему фронту этого импульса счетчик 7 изменяет свое состояние на единицу. Новое состояние счетчика 7 поступает на входы регистра 17 и блока 14 исключения запрещенных состояний ° . Переключатель 19 блока 14 исключения запрещенных состояний, соответствующий запрещенным состояниям, устанавливается в положение, при котором выходы дешифратора 18 соединены с входами элемента ИЛИ 20. При появлении на выходе счетчика 7 разрешенной комбинации блок 14 формирует на своем выходе нулевой потенциал, который через элемент НЕ поступает на вход элемента И 16. Благодаря этому импульс от генератора 3 поступает на управляющий вход регистра 17. IIo заднему фронту этого импуль

ca состояние счетчика 7 записывается в регистр 17 и поступает на входы проверяемого 1 и эталонного 2 узлов.

При появлении на выходе счетчика 7 комбинации логических уровней, представляющей запрещенное состояние, на одном из выходов дешифратора 18 возникает единичный потенциал, который через соответствующий переключатель 19, элемент ИЛИ 20 и элемент НЕ 15 поступает на вход элемента И 16. Вследствие этого, импульс от .генератора 3 не проходит на управляющий вход регистра 17. Таким образом, .запрещенная комбинация не записывается в регистр 17 и не поступает на входы цифровых узлов

1 и 2 .

Если при подаче логической комбинации на входы узлов 1 и 2 на их выходах .формируются различные состояния, с блока 13 сравнения поступает на вход элемента И 5 запрещающий потенциал и импульс с выхода генератора 3 не поступает на вход счетчика 7. По показаниям блоков

10, 11 и 12 индикации можно зарегистрировать логические уровни на входах и выходах узлов 1 и 2. для продолжения проверки в этом случае необходимо включить переключатель 8.

Генератор 4 выдает один импульс,который изменяет состояние счетчика на единицу, далее процесс повторяется.

Введение в устройство регистра 17, элемейта .И 16 и элемента HE 15 позво1005061 ляет исключить запрещенные комбина;ции из числа наборов логических уров ней, поступающих на входы проверяемого и эталонного щфровых узлов, тем самым увеличить достоверность контра- ля, обеспечить койтроль элементов па-. мяти с запрещенными входными воздей ствиями. формула изобретения

Устройство для контроля цифровых узлов,,содержащее счетчик, эталонный узел, генератор импульсов, генератор одиночного импульса, первый элемент И; элемент ИЛИ, два переключателя, три блока индикации, блок сравнения, блок исключения запрещенных состояний, причем выходы счетчика соединены соответственно с.входами блока исключения запрещенных состояний, вход генератора одиночного импульса через Зр первый переключатель соединен с шиной положительного потенциала, вы. ход генератора одиночного импульса соединен с первым входом элемента

ИЛИ, второй вход которого соединен с 25 выходом первого элемента И, выход элемента ИЛИ связан со счетным входом счетчика, установочные входы счетчика, эталонного узла и проверяемого узла подключены через второй Зр переключатель к шине положительного потенциала, выходы проверяемого узла соединены с первой группой входов блока сравнения и с входами перного блока индикации, выходы зталоЪного узла соединены с второй группой входов блока сравнения и с входами второго блока индикации, выход блока сравнения подключен к первому входу первого элемента И, второй вход которого соединен с выходом генератора импульсов, о т.л и ч а ю щ ее с я тем, что, с целью повьыения достоверности контроля, в устройство введены регистр, элемент НЕ, второй элемент И, выход которого соединен с управляющйм входом регистра, установочный вход которого соединен с установочным входом счетчика, а информа ционные входы регистра соединены; с выходами счетчика, выхода регистра соединены соответственно с входами проверяемого узла, с входами эталонного узла, с входами третьего блока индикации, выход блока исключения запрещенных состояний соединен с входом элемента НЕ, выход которого соединен с первьм входом второго эле- . мента И, второй вход которого соединен с выходом генератора импульсов.

Источники информации, принятые во внимание при экспертизе

1. Универсальный логический тестор для проверки микросхем в производстве. - "Электроника" И., "Мир", 1974, Р 8, с. 65-67.

2. Авторское свидетельство СССР

В 648981, кл. G 06 F 11/00, 1977 (прототип).

1605061

Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам:изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.,4/5

Заказ 1901/65

Филиал ППП Патент", г. Ужгород, ул. Проектная, 4

Составитель Н. Торопова

Редактор Л. Алексеенко Техред А.Бабинец Корректор Е. Рашко