Устройство для сокращения избыточности информации

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советскиз

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. сеид-ву— (22) Заявлено 30.12,81 (21) 3372241/18-24 с присоединением заявки Йо(23) Приоритет—

Опубликовано 15D383. Бюллетень М10

Дата опубликования описания 15.03.83

РЦМ.К>.

G 08 С 19/28

Государственный комитет

СССР но делам изобретений н открытий

Щ) УДК 621, 398 (088. 8) (72) Авторы изобретения

Ю.A. Галяс, A.Ê. Флоров и B.Ï.

Ф.

Днепропетровский ордена Трудов государственный универс воссоединения Украи (71) Заявитель,(54) УСТРОЙСТВО ДЛЯ СОКРАЩЕНИЯ ИЗБЫТОЧНОСТИ

ИНФОРМАЦИИ

Изобретение относится к телеметрии и может быть . использовано в многоканальных цифровых телеметрических системах для передачи информации с малой избыточностью.

Известно устройство для передачи телеметри еской информации, содержащее синхронизатор, выход которого подключен к коммутатору каналов, к блоку памяти полных кодов и соответственно через блок кодирования адресов и блок кодирования времени-к первому и второму входам. буферного запоминающего устройства, выход коммутатора каналов через блок кодирования 15 подсоединен к блоку памяти полных кодов и к анализатору сигналов. Выход блока памяти полных кодов соединен с анализатором сигналов, выход которого подключен соответственно к первому входу и через блок памяти кодов приращения-ко второму входу блока сравнения кодов приращения. Выход блока памяти полных кодов подключен к входу элемента И, выход блока сравнения кодов приращения - к второму входу элемента И, к входу буферного запоминающего устройства, выход элемента

И соединен с другим входом буферного запоминающего устройства, а один выход синхронизатора — с соответствующим входом блока памяти кодов приращения 5,13.

Это устройство обеспечивает большой коэффициент сжатия, но является сложным по своей технической реализации и обладает сравнительно низким быстродействием.

Наиболее близким по технической сущности к предложенному является устройство, содержащее коммутатор, вход которого соединен с блоком синхронизации, а выход через аналого-цифровой преобразователь соединен с блоком буферной памяти.и со входами N блоков сравнения, выходы которых подключены ко входам устройства управления, а выходы устройства управления подключены к управляющим входам й- блоков сравнения, к блоку буферной памяти и к управляющим входам N сумматоров, информационные входы которых подключены к выходу аналого-цифрового пре- образователя,. вторые информационные входы подключены к выходам соответствующих блоков постоянной памяти, а выходы сумматоров соединены с информационными входами соответствующих блоков сравнения, управляющие входы которых подключены к выходу блока

1005148

K, =K

СЧ И синхронизации, другой выход которого соединен с управляющими входами сумматоров (2 3.

К недостаткам известного устройства "отйосится то, что коэффициент сжатия частот, обеспечиваемый устрой- 5 ством, является небольшим. Это обусловлено тем< что сжатие информации достигается эа счет уменьшения числа передаваемых координат, а объем каждой передаваемой координаты остается 10 неизменным. К числу недостатков данного устройства следует отнести также сложность его технической реализации.

Цель изобретения — повышение информативности устройства и упрощение )5 технической реализации устройства.

Поставленная цель достигается тем, что устройство, содержащее коммутатор, информационный вход которого соединен с входом устройства, выход с входом аналого-цифрового преобразо20 вателя, блок синхронизации, первый и . второй выходы которого соединены с управляющими входами коммутатора и блока сравнения, блок постоянной памяти и блок буферной памяти, выход которого соединен с выходом устройства, дополнительно содержит арифметический блок и регистр, выход аналогоцифрового преобразователя и блока постоянной памяти соединены с информационными входами арифметического блока, первый выход которого соединен с информационным входом регистра, второй выход — c информационным входом блока буферной памяти и первым инфор- З5 мационным входом блока сравнения, первый и второй выходы блока сравнения соединены с управляющими входами соответственно блока буферной памяти и регистра, выход которого соединен 40 со вторым информационным входом блока сравнения, третий выход блока синхронизации срединен с управляющим входом арифметического блока.

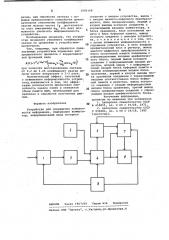

На чертеже представлена структур- 45 ная схема устройства.

Устройство содержит коммутатор 1, аналого-цифровой преобразователь 2, блок 3 постоянной памяти, арифметический блок 4, регистр 5, блок б син- 5О хронизации, блок 7 сравнения и блок 8 буферной памяти.

Устройство работает следующим образом.

В блок 3 постоянной памяти до начала обработки сообщения заносится значение максимально допустимой абсолютной погрешности восстановления сжатых данных . Цикл обработки 1-.го отсчета состоит из трех тактов. По первому тактовому импульсу с блока 6. 6О синхронизации обрабатываемый сигнал через коммутатор 1 поступает на аналого-цифровой преобразователь 2, где преобразуется в цифровую форму. По второму тактовому сигналу арифмети- 65 ческий блок 4, используя данные, поступающие на его входы с блока 3 постоянной памяти и с аналого-цифрового преобразователя 2 в соответствии с выражением где Х (1 ) — значение обрабатываемого отсчета, определяет параметр Н(), однозначно характеризующий отсчет. По третьему тактовому импульсу, поступающему с блока 6 синхронизации. блок 7 сравнения сравнивает значение параметра N (i ), поступающего на его вход с арифметического блока 4 со значением параметра N(-1), поступающим на другой его вход с регистра 5. Если N(i)=N(i-1), то блок 7 сравнения не вырабатывает никаких управляющих сигналов и устройство переходит к обработке нового отсчета. Если же N(i ) 4 И (1- I ), то блок 7 сравнения вырабатывает сигнал,по которому значение N(i) переписывается в регистр 5 и в блок 8 буферной памяти, из котррого это значение N (i) передается на выход устройства (в канал связи). Далее устройство переходит к обработке нового отсчета. достижение поставленной цели можно проиллюстрировать следующими рассуждениями.Как известно, коэффициент сжатия полосы частот К определяется соотношением где К вЂ” коэффициент сжатия по числу отсчетов; пи — объем информационной части слова не сжатых данных;

toè — объем информационной части слона сжатых данных; в „ - объем служебной, информации, приходящейся на один существенный отсчет.

Из этого выражения следует, что коэффициент сжатия полосы частот можно увеличить путем увеличения К и путем уменьшения m В устройстве-прототипе, как и во всех других апертурных устройствах сжатия информации, К« увеличивается путем увеличения К. Эначе ния nä и m в этих устройствах представляют собой одну и ту же величину.

В предлагаемом устройстве обрабатываемый процесс на выходе устройства представляется в виде параметров N(i} .

Экспериментальные и теоретические исследования показывают, что количество двоичных разрядов, необходимых для представления параметров N(i) меньше, чем количество двоичных разрядов, необходимых для представления значений

i -го отсчета сигнала Х (i ) . Таким об1005148

Формула изобретения

ВНИИПИ Заказ 1907/69 Тираж б16 Подписное

Филиал ППП "Патент", г.ужгород,ул.Проектная,4 разом, при обработке сигнала с помощью предлагаемого устройства дополнительное увеличение коэффициента сжатия полосы частот Еу достигается за счет уменьшенйя ви, что дает возможность увеличить информативность устройства.

Исследования показали, что устройство позволяет увеличить коэффициент сжатия по сравнению с устройствомпрототипом.

Так, например, при обработке предлагаемым устройством нормально распределенного процесса с корреляционной функцией вида

15 ,9(Т)=7, Е - (cos(u Vü+.— gin(u )it)

2 -со (!/ ф при точности восстановления сигнала от 0,2 до 1.0Ъ коэффициент сжатия по.яосы частот возрастает в 2-3 раза.

Положительный эффект, связанньФ с повышением информативности устройства заключается в том, что эффективно используется пропускная способность канала связи и снижается объем памяти ЦВИ, необходимый для хранения и обработки полученных данных.

Устройство для сокращения избыточности информации, содержащее коммутатор, информационный вход которого

"оединен с входом устройства, выход— с входом аналого-цифрового преобразователя, блок синхронизации, первый и второй выходы которого соединены с управляющими входами коммутатора, и блока сравнения, блок поСтоянной памяти и блок буферной памяти, выход которого соединен с выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения информативности .и упрощения устройства, в него введены арифметический блок и регистр, выход аналого-цифрового преобразователя и блока постоянной памяти соединены с информационными входами арифметического блока, первый выход которого соединен с информационным входом регистра, второй выход — с информационным входом блока буферной памяти и первым информационным входом блока сравнения, первый и второй выходы бло» ка сравнения соединены с управляющими входами соответственно блока буферной памяти и регистра, выход которого соединен с вторым информационным входом блока сравнения, третий выход, блока синхронизации соединен с управляющим входом арифметического блока.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 458851, кл. G 08 С 19/28, 1971.

2. Авторское свидетельство СССР

Р 830484, кл. G 08 С 19/28, 1980 (прототип ).