Трехканальное запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (g))1005186 (61) Дополнительное к авт. свид-ву— (22) Заявлено 200781 (21) 3317907/18-24 (31) М. Кд. з с присоединением заявки М— (23) Приоритет —.

С11 С 11/00

Государственный комитет

СССР ио делам изобретений и открытий

Опубликовано 150333. Бюллетень 1о 10

ДЗ) УДК 681.327 (088.8) Дата опубликования описания 150383

О.И.Плясов и В.Н.Середа (72) Авторы изобретения (71) Заявитель (54) ТРЕХКАНАЛЬНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к запоминающим устройствам.

Известно трехканальное запоминающее устройство, содержащее коммутатор каналов, каналы вычислительной системы, мажоритарный блок сравнения. блок анализа11 1.

Недостатком этого устройства является низкая надежность °

Наиболее близким к изобретению является трехканальное запоминающее устройство, содержащее три резервируемых блока памяти. мажоритарный элемент, схемы сравнения; триггеры, элемент И, переключающий элемент, причем выходы резервируемых блоков подключены ко входам мажоритарного эчемента.и попарно — к трем схемам сравнения.. выходы которых соединены со входами соответствующих трех триггеров, выходы триггеров через элемент И подключены к управляющему, входу переключающего элемента, первый сигнальный вход которого соетщнен с выходом мажоритарного элемента. а второй — с выходом одного из резервируемых блоков (2).

Недостатком известного устройства является отсутствие средств внутриканального контроля резервируемых блоков. что не позволяет достоверно определить последний исправный канал при отказе двух других каналов устройства и снижает его надежность.

5 Целью изобретения является повышение надежности устройства..

Поставленная цель достигается. тем. что в трехканальное запоминающее устройство, содержащее в каждом

10 из каналов первый блок памяти, схему сравнения, первый триггер, мажоритарный элемент и первый элемент И. причем информационные выходы первого блока памяти соединены с одноименны15 ми инфОьмационными входами мажоры тарных элементов первого;второго и третьего каналов . одними из входов. схемы сравнения одноименного канала и другими входами схемы сравнения

2р предыдущего канала. выходы мажори.тарных элементов и адресные входы первых блоков памяти являются соответственно информационными выходами . и,адресными входами устройства, введены в каждом канале второй блок памяти. второй .триггер. второй элемент И, элемент ИЛИ и элемент НЕ, причем выход схемы сравнения ооеди нен с первыми . входами первого и второго элементов И одноименного канала. вторыми входами первого и вто1005186 рого элементов И последующего канала, третьим входом первого элемента

И и входам элемента НЕ предыдущего канала, третий вход второго элемента И, каждого канала подключен к выходу элемента НЕ. а выход — к первому входу элемента ИЛИ, выход которого соединен со входом второго триггера. а второй вход — с контрольным выхо,дом первого блока памяти, одни из ад ресных входов которого подключены к 10 адресным входам второго блока памяти, контрольный вход которого соединен с выходом первого триггера. вход которого подключен к выходу первого элемента И. первый, второй и третий 15 информационные входы второго блока памяти соединены соответственно с выходами вторых триггеров первого, второго и третьего каналов, первый, второй и третий выходы второго блока памяти подключены к управляющим входам

20 мажоритарного элемента, выходы с первого по четвертый вторых блоков .памяти являются контрольными выходами устройства.

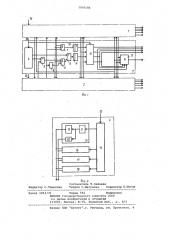

На фиг.1 изображена функциональная схема предложенного устройстваг на фиг.2 - функциональная схема наиболее предпочтительного варианта выполнения первого блока памяти.

На фиг.1 обозначены первый 1, вто-З0 рой 2 и третий 3 каналы устройства.

Устройство содержит (фиг.1) в каждом из каналов первый блок 4 памяти, схему сравнения 5, элемент НЕ 6, пер-.. вый 7 и второй 8 элементы И, элемент 35

HJIH 9, первый 10 и второй 11 триггеры, второй блок 12 памяти и мажоритарный элемент 13.

Первый блок памяти состоит из {фиг,2) блока 14 управления, первой 15,второй

16, третьей 17 и четвертой 18 секций, каждая из которых содержит блок 19 элементов памяти с последовательными адресами, причем число элементов памяти равно четверти информационного объема блока памяти, блок 20 контро.ля по модулю два и дешифратор 21 адреса. На фиг.1 и фиг.2 обозначены адресные входы 22 устройства.

Секцией блока 4 считается совокупность оборудования, отказ которого не приводит к отказу в других секциях блока 4, причем в общем случае количество секций может быть не равно четырем.

Второй блок 12 памяти содержит 55 одноразрядные ячейки памяти, каждая из которых соответствует одной из секций 15-18 блока 4, и может быть выполнена на одной БИС.

Устройство работает следующим .об- 60 разом.

При появлении адреса на входах 22 срабатывает блок 14 (фиг.2), дешифратор 21, соответствующий адресу одной из секций 15 (16,17,18) и на информационных выходах блока 4 появляется код. содержащийся в выбранном по адресу элементе памяти блока 19.

Одновременно на контрольном выходе блока 4 появляется сформированный блоком 20 сигнал контроля по модулю два. Нулевой уровень этого сигнала соответствует отсутствию брака в коде, присутствующем на информационных выходах блока 4, а единичный— наличию брака.

Код с информационных выходов блока 4 (фиг.1) поступает на информационные входы мажоритарного элемента 13.

Код п старших разрядов адреса на входах 22 (фиг.1 и фиг.2)(m

Во< 20, где Р— число секций блока 4 ) поступает на адресные входы блока 12 (фиг.1) и на его выходах появляется код содержимого ячейки памяти соответствующей m старшим разрядам адреса. В начальном состоянии все ячейки памяти блока 12 содержат код "1111" (входы установки кода на фиг.1 условно не показаны).

При отсутствии отказов в блоке 4 триггеры 10, 11 не срабатывают и код поступает на контрольные выходы устройства, свидетельствуя о6 отсутствии отказов, а второй, третий и четвертый разряды кода поступают на управляющие входы мажоритарного элемента 13, задавая мажоритарный режим работы. При этом на информационных выходах устройства (на фиг.1 показан один из выходов ) появляется мажоритированная информация.

При отказе блока 4 в одном канале (например, в канале 2) срабатывают схемы 5 сравнения в каналах 1 и 2, а схема 5 сравнения в канале 3 не срабатывает,так как код на информационных выходах блока 4 в каналах

3 и 1 одинаковый.

Затем срабатывает элемент И 8 и:элемент ИЛИ 9, и триггер 11 в канале 2 устанавливается в "0" (начальное состояние "1") независимо от того, обнаружен контролем по модулю два брак в канале 2 или нет. При этом, s случае правильной работы устройства вероятность обнаружения первого отказа канала 1,2 или 3 максимальна и равна единице.

Код триггера 11 переписывается в разряд ячейки памяти блока 12, соответствующий отказавшему каналу.

Адрес, присутствующий иа входах 22, соответствует адресу отказавшей из

° секций 15-18 блока 4 (фиг.2) . Информация, отражающая содержимое этой ячейки памяти блока 12 (1101), появляется на выходах блока 12 и контрольных выходах устройства. Мажоритарный элемент 13 при этом продолжает работать в мажоритарном режиме.

1005186

Аналогичные процессы происходят при отказе блока 4 одного из каналов 1 или 3.

При отказе блока 4 в двух из каналов 1,2,3 информация первого отказавшего канала может быть искажена или соответствовать правильной.

Последнее происходит, например, в случае отказа информационного разряда блока 4 в одном иэ каналов 1,2,3 при случайном (с вероятностью 0,5) совпадении его значения с правильным значением. При этом обнаружение второго отказа производится схемами сравнения. При искажении информации обоих отказавших каналов 15 схемы 5 сравнения и элементы И 7 всех трех каналов 1,2;3 срабатывают, в триггер 10 и первый разряд блока 12 записывается "0" (начальное состояние триггера 10 — "1"), триг- 20

rep 11 второго отказавшего из каналов 1,2,3 срабатывает при обнаружении отказа в нем контролем по модулю два °

Например, если отказали одноименные из секции 15-18 (фиг.2) каналов 1 и 2 (фиг.1) то выходные коды блоков 12 будут "1001" или "0001", и мажоритарные элементы 13 перестраиваются на выдачу кода последней исправной из секций 15-18 (фнг.2) блока 4 третьего канала 3. При обнаружении отказа в блоке 4(фиг.1) последнего (третьего) канала 3, например, выходной код блока 12 будет

"1000" или "0000", и мажоритарный элемент 13 перестраивается на работу в мажоритарном режиме.

Это позволяет, в случае отказа разноименных информационных разрядов блоков 4 в трех каналах 1,2 и 3 40 сформировать правильную информацию на выходе мажоритарного элемента 13.

Таким образом, повышение надежности устройства достигается за счет обеспечения работоспособности уст- .45 ройства при максимальном .числе отказов с различными вариантами распределения отказов по секциям 15-18 (фиг.2) блоков 4 (фиг.1). .Технико-экономическое преимущество предложенного устройства заключа5 ется в его более высокой надежности по сравнению с прототипом.

Формула изобретения

ТРехканальное запоминающее УстРой-55 ство, содержащее в каждом из каналов первый блок памяти, схему сравнения, первый триггер, мажоритарный элемент и первый элемент И, причем информационные выходы первого блока памяти соединены с одноименными информационными входами мажоритарных элементов первого, второго и третьего каналов, одними из входов схемы сравнения одноименного. канала и другими входами схемы сравнения предыдущего канала, выходы мажоритарных элементов и адресные входы первых блоков памяти являются соответственно информационны- ми выходами и адресными входами устройства, о т л и ч а ю щ е е с я тем, что, с цельЮ повыаения надежности устройства, в него введены в каждом канале второй блок памяти, второй триггер, второй элемент И, элемент

ИЛИ и элемент НЕ, причем выход схемы сравнения соединен с первыми входами первого и второго элементов И одноименного канала, вторыми входами первого и второго элементов И последующего канала, третьим входом первого элемента И и входом элемента НЕ предыдущего канала, третий вход второго элемента И каждого канала подключен к выходу элемента НЕ, а выход — к первому входу элемента ИЛИ, выход которого соединен с входом второго триггера, а второй входс контрольным выходом первого блока памяти, одни из адресных входов которого подключены к адресным входам второго блока памяти, контрольный вход которого соединен с выходом первого триггера, вход которого подключен к выходу первого элемента И, первый, второй и третий информационные входы второго блока памяти соединены соответственно с выходами вторых триггеров первого

1 второго и третьего каналов, первый второй и третий выходы второго блока памяти подключены к управляющим входам мажоритарного элемента, выходы с первого по четвертый вторых блоков памяти являются котрольными выходами устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидатальство СССР

В 383047, кл. G 06 F 9/00, 1971.

2. Авторское свидетельство СССР

Р 318919, кл. Q, 05 В 23/00. .

1005186

Aii 1

Ррг 2

Составитель Т.Зайцева

Редактор С.Тимохина Техред С.Мигунова Корректор И.Шулла

Заказ 1911/71 . Тираж 592 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д . 4/5

Филиал ППП "Патент",г. Ужгород, ул. Проектная, 4