Запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

gij1005193 (61) Дополнительное к авт. сеид-ву (22) Заявлено .26.11. 81 .(21) 3356816/18-24 с присоединением заявки М (23) Приоритет

Р11М. Ка.з

G 11 С 29/00

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано 15.0383. Бюллетень Ко|10

Рз)УДК 681. 327, . б (088.8) Дата опубликовання описания 15 . 03 . 83

В.к.конопелько / "" юфзш т

"Мл л . ю, -, т".ф

Минский радиотехнический институт, (72) Автор изобретения (71) Заявитель

1,54} ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ

Изобретение относится к вычислительной технике и может быть использовано при создании надежных быстродействующих систем памяти на базе больших интегральных микросхем памяти со словарной -организацией.

Известно запоминающее устройство, в котором для автоматического исп- равления ошибок, возникающих из-за отказов интегральных микросхем памяти (ИМП), данные кодируются помехоустойчивым кодом (1 1.

Однако эти устройства требуют большого числа дополнительных разрядов элементов памяти при коррекции 4, 8 отказов в слове, а также сложных кодирующих и декодирующих схем.

Наиболее близким техническим решением к изобретению является запо- минающее устройство, содержащее накопитель, первые входы которого соединены с выходами адресного блока, вторые входы накопителя соединены с шинами записи и входами блока кодирования, третьи входы накопителя соединены с выходами блока кодирования, первые и вторые выходы накопителя соединены с входами блока контроля и первь1ми входами сумматоров по модулю два, выходы блока контроля соединены с входами элемента

ИЛИ и первыми входами первых элементов И, вторыми входами соединен1-. ных с выходами элемента ШП!,.выходы первых элементов Jt соединены с вторыми входами суьвиаторов по модулю два, выходами соединенных с выходами устройства (21

Такое устройство позволяет исправить одиночный блок ошибок длины однако требует при обнаружении ошибки повторной записи в накопитель инвертированного слова и повторного считывания .информации. Это снижает быстродействие устройства. Кроме. того, при коррекции ошибок иэ-за отказа HNII не учитывается тот факт, что отказ приводит к появлению единичных сигналов. на выходах ИИП.

Целью изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем, что запоминающее устройство с . самоконтролем, содержащее накопитель, входы первой группы которого подключены к. выходам адресного бло-. ка, входы второй группы накопителя подключены ко входам шифратора и являются входами устройства, выходы

1005193 в.нфратара подключены ко входам третьей группы накопителя, выходы первой к,второй групп которого подключены к входам блока контроля, выходы блока контроля подключены ко входам зле лента ИЛИ и к первым входам соответствующих элементов И первой группы, выход элемента ИЛИ подключен ко вторым входам элементов И первой группы, выходы которых подключены к первым входам соответствующих сумматоров по модулю два, вторые входы сумматоров по модулю два подключены к соответствующим выходам первой группы накопителя, выходы сумматоров по модулю два яв- 15 ляются выходами устройства, дополнительно содержит вторую группу элементов И, входы которых подключены к соответствующим входам первой группы накопителя, выходы элементов И второй группы подключены ко входам четвертой группы накопителя, и третью группу элементов И, одни входы которых подключены к соответствующим выходам первой группы накопи- д теля,другие входы элементов И третьей группы подключены к соответствующим выходам третьей группы накопителя, выходы элементов И третьей группы подключены к третьим входам соответствующих элементов И первой группы.

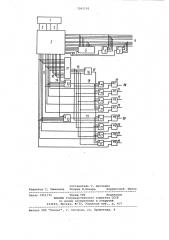

На чертеже приведена структурная схема запоминающего устройства с самоконтролем.

Запоминающее устройство с самоконтролем содержит адресный блок 1, первую группу входов 2 накопителя, накопитель 3, входы 4 устройства, шифратор 5, вторую группу элементов

И 6, третью группу входов 7 и чет- 4О вертую группу входов 8 накопителя, первую группу выходов 9 и вторую группу выходов 10 накопителя, блок 11 контроля, сумматоры 12 по модулю два, первую группу элементов И 13, 4$ третью группу выходов 14 накопителя, выходы 15 блока контроля, элемент

ИЛИ 16, элементы И 17 первой группы, выход 18 элемента ИЛИ, выходы 19 элементов И первой группы и выходы у)

20 устройства. Шифратор 5 и блок 11 контроля состоит из сумматоров по модулю два.

Устройство позволяет исправить одиночные в кратные отказы в каждом слове накопителя из-за отказа ИМП с единичными сигналами на выходах при наличии b + 0 дополнительных разрядов и высоком быстродействии устройства,где 3= — k — число информаци k

Ь онных р=эрядов в слове.

В режиме записи информации устройство работает следующим образом.

Двоичное кодовое слово длины Ф+Ф, первые k=Ъп (и — число микросхем памяти ) разрядов которого являются информационным, а последние Ь разрядов контрольными, через входы 4, 7 помещается в накопитель 3 по адресу, поступающему через шины 2 из адресного блока 1. В шифраторе 5 происходит вычисление контрольных символов путем суммирования по модулю два и блоков по Ь разрядов в каж дом. Одновременно по этому же адресу в накопитель по входам 8 заносит ся для хранения информация с выходов элементов И 6. Эта информация указывает подлежит ли хранению в какойлибо микросхеме памяти данного слова единичный блок информации.

II p и м е р 1 ; Пусть 3с = 16, Ь = 4, и = 16, Ю = n = 4, т.е.

У при построении накопителя с длиной слова в 1,6 разрядов используется четыре ИМП с четырьмя шинами записи-считывания каждая и пусть в накопитель записывается информация

1000 1100 0010 1111.

Тогда в контрольные разряды записывается информация 1001, так как

1 000

0010

1111

1 0 0 1 по модулю два, а в 6 контрольные. разряды .ваписывается информация 0001, так как только в четвертом блоке записи подлежит единичное слово.

Таким образом, в накопитель заносится слово 1000 1100 0010 1111

1001 0001.

В режиме считывания йнформации выходные данные по шинам 9, 10, 14 подаются на блок 11 контроля и одновременно на элементы H 13. Блоком 11 вырабатывается признак (синдром ), который равен нулю, если ошибок нет в ф + b ) разрядах, и не равен нулю в противном случае.

Если в считываемом слове ошибок нет, то на выходе 18 элемента ИЛИ 16 ,будет нулевой сигнал, который установит на выходах элементов И 17 нулевйе сигналы. Тем самым на выходы

20 устройства поступят сигналы с

1 информационных разрядов с выходов

9 накопителя через сумматоры 12 без изменения.

Если в считываемом слове в (+

+ Ь ) разрядах имеются ошибки в Ь разрядах из-за отказа, любой одной

ИМП, что приводит к появлению на

1005193 выходах отказавший ИМП единичных сигналов, то на выходах 15 блока 11 будет ненулевой сигнал, а на выходе

18 элемента ИЛИ 16 — единичный сигнал. Кроме того, единичный сигнал появится на одном из выходов 19 5 элемента И 13, поскольку на выходах

9 у отказавшей HMH накопителя 3 будут единичные сигналы, а на инвертирующем входе элемента И 13 нулевой сигнал. Единичный сигнал с выхода 19 элемента И 13 откроет соответствующие .элементы И 17, относящиеся к отказавшим разрядам. Эти же элементы И 17 будут открыты по другому входу единичным сигналом с 15 выхода 18 элемента ИЛИ 16, на выходах соответствующих элементов И 17 появятся сигналы, отображающие ненулевой синдром. При сложении на сумматорах 12 rio модулю два этого синд- 20 рома с информацией, относящейся к этому блоку (единичной информацией ), происходит коррекция считываемой информации из искаженного блока (отказавшей ИМП ).

Если же искаженныии являются Ь контрольные разряды, то на выходах

19 элементов И 13 будут нулевые сигналы, так как все информационные разряды исправны (корректируется 30 только один дефектный блок разрядов ), и следовательно, элементы И 17 будут закрыты. Информация, считываемая с информационных разрядов накопителя, поступит через сумматоры 12 на выходы 20 устройства без изменения.

Если же искаженными являются контрольные разряды, то на выходе блока 11 будет нулевой синдром. Тогда на выходе 18 элемента ИЛИ 16 40 появится нулевой сигнал, который закроет элементы И 17. Тем самым информация, считываемая с информационных разрядов накопителя, поступят- через суввюаторы 12 на выходы 45

20 устройства без изменения.

Пример 2 . Пусть для вышеприведенного примера информация искажена в первом блоке из-за отказа ИМП, т.е. с выходом 9,. 10, 14 накопителя 3 считывается число 1111

1100 0010 1111 1001 0001. Тогда на выходе 15 блока 11 будет 0111, так как

1 1 1 1 1

1 1 0 0 2

0 0 1 0 3

11114

1 0 0 1 5

0111 60

Кроме того, поскольку первый блок содержит единичные символы, а первый из С контрольных символов нулевой,.то на одном из выходов элементов Й 13 будет единичный сигнал, 65 который откроет соответствующие элементы И 17. Тем самым на выходе этих элементов выделится синдром. Тогда на сумматорах 12 произойдет суммирование синдрома н информации из искаженного блока, т-.е. 0111 > 1

=1000, что соответствует исходной подлежащей хранению информации в этом блоке.

Таким образом, в предлагаемом устройстве отсутствует необходимость проведения записи инвертированного слова и контрольного считывания при обнаружении отказов, что позволяет повысить быстродействие устройства-.

Формула изобретения

Запоминающее .устройство с самоконтролем, содержащее накопитель, входы первой группы которого подключены к выходам адресного блока, входы второй группы накопителя подключены ко входам шифратора и являются входами устройства, выходы шифратора ,подключены ко входам третьей группы накопителя, выходы первой и второй групп которого подключены ко входам блока контроля, выходы блока контроля подключены ко входам элемента ИЛИ и к первым входам соответствующих элементов И первой группы, выход элемента ИЛИ подключен ко вторым входам элементов И первой группы, выходы которых подключены к первым входам соответствующих сумматоров по модулю два, втбрые входы сумматоров по модулю два подключены к соответствующим выходам первой группы накопителя, выходы сумматоров по модулю два являются выходами устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, оно содержит вторую группу элементов И, входы которых подключены к соответствующим входам первой группы накопителя, выходы элементов И второй группы подключены ко входам четвертой группы на копителя, и.третью группу элементов

И, одни входы которых подключены к соответствующим выходам первой группы накопителя, другие входы элементов И третьей группы подключены к соответствующим выходам третьей группы накопителя, выходы элементов

И третьей группы подключены к третьим входам соответствующих элементов И первой группы.

Источники информации, принятые во внимание при экспертизе

1. Самофалов К.Г., Корнейчук B.È., Городний A.B. Структурно-логические методы повышения надежности запоминающих устройств. М., ".Машиностроение", 1976, с. 101 — 106.

2. Авторское свидетельство СССР по заявке 9 3256760/18-24, кл. 4 - 11 С 29/00, 1981 (прототип).

1005193

Составитель С. Шустенко

Редактор С. Тимохина Техред Л.Пекарь КорректорИ. Шулла

Заказ 1911/71 Тираж 592 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП "Патент", г. Ужгород, ул. Проектная, 4