Матричный коммутатор

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

: К АВТОРСКОМУ СВИДИТИЗЬСТВУ

Союз Советскик

Социапистмческик

Республик (l > il 005308 (61) Дополнительное к авт. свнд-ву (22) Заявлено 04.05.81(2l) 3282356/18 21 с присоединением заявки М (23) Приоритет (Sl}N. Кй.

Н 03 К 17/00

Гееудеретеееай кеаетет

СССР ао аееан кзаервтекке н еткрытий

Опубликовано 15,03.83. Бюллетень М 10 (53) УДК621. .382(088.8) Дата опубликования описания 15.03.83

Б. М. Шамес, В. Н. Козлова и Е. А. Хрипин (72) Авторы иэобретения (71) Заявитель (54) МАТРИЧНЫЙ КОММУТАТОР

Изобретение относится к автоматике и может быть использовано в аппаратуре контроля и управления для коммутации сигналов датчиков.

Известен многоканальный коммутатор, содержащий пересчетное устройство с дешифратором 1 1 .

Недостаток - отсутствие избирательности опроса.

Известен также матричный коммутатор, содержащий пересчетные устройства, входы которых соединены с соответствующими входами дешифратора, выходы последних соединены между собой через коммутирующие элементы по матричной . схеме (21.

Недостаток устройства - низкое быстродействие.

Цель изобретения - увеличение бысч родействия. . Для достижения цели в матричный коммутатор, содержащий пересчетные устройства, выходы которых соединены с соответствующими входами дешифраторов, 2 выходы последних соединены между собой через коммутирующие элементы по ,матричной схеме, введены блок управления предустановки, логическйе устройства предустановки и стробирования, при

5 этом выходы блока управления предустановки соединены со входами логических устройств предустановки, выходы которых соединены со входами соответствующих пересчетных устройств, шина тактовых

1о импульсов подключена через соответствуюпше логические устройства стробирования к соответствующим входам соответ ствующих дешифраторов 1т ко входу пер- . вого пересчетного устройства, выход ко торого соединен с соответствующим входом второго пересчетного устройства.

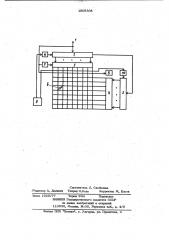

На чертеже изображено предлагаемое устройство.

Устройство содержит шину 1 тактовых импульсов (ТИ), пересчетные устройства 2 и 3, дешифраторы 4 и 5, матричное коммутирующее устройство 6, логические устройства стробирования 7

308 4 ческих элементов И соединены с соо ветствующими выходамн пересчетных устройств или с выходами логических элементов НЕ, а также с выходом логического устройства стробирования. Входы логического элемента HE соединены с соответствующим выходом пересчетного устройства, а выходы — с соответствующими входами И. С выхода логического элемента И сигнал поступает на коммутирующее устройство, которое представляет собой набор реле, которын соединяют столбцы шин дешифратора с строками шин дешифратора 5 по матричной схеме.

Использование предлагаемого коммутатора по сравнению с известным, обеспечивает следующие преимушества: возможность выбора коммутирующего устройства за счет предустановки; за счет связи входа тактовых импульсов со стробируюшими входами дешифраторов вдвое увеличивается количество коммутируемых устройств без увеличения емкости счетчиков и дешифраторов, т.е. появляется возможность варьировать избирательностью опроса и, кроме того, сокращается время опроса.

: Формула изобретения

Матричный коммутатор, содержащий пересчетные устройства, выходы которых соединены с соответствующими входами дешифраторов, выходы последних соединены между собой через коммутирующие элементы по матричной схеме, о т л и— ч а ю шийся тем, что, с целью увеличения. быстродействия, в него введены блок управления предустановки, логические устройства предустановки и стробирования, при этом выходы блока управления предустановки соединены с входами логических устройств предустановки, выходы которых соединены с входами соответствующих пересчетных устройств, шина тактовых импульсов подключена через соответствующие логические устройства стробирования к соответствующим входам соответствующих дешифраторов и к входу первого пересчетного устройства, выход которого соединен с соответствующим входом второго пересчетного устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

% 610302, кл. Н 03 К 17/00, 17.06.76.

2. Авторское свидетельство СССР

М 227381, кл. Н 03 K 17/00, l7.07.1967 (прототип).

3 1005 и 8, блок 9 управления предустановки, логические устройства предустановки 10 и ll.

Шина тактовых импульсов 1 через первое пересчетное устройство 2, счетный ,вход второго пересчетного устройства 3, дешифратор 4 соединена с матричным коммутирующим устройством 6. Шина тактовых импульсов 1 через логическое устройство стробирования 7, дешифратор 5 10 соединена с матричным коммутирующим устройством 6. Выходы блока управлении предустановки 9 соединены параллельно через первое и второе логические устройства предустановки 10, 11 с пере- 15 счетными устройствами 2 и 3. Шина тактовых импульсов 1 через логическое устройство 8 стробирования соединена с дешифратором .4.

Устройство работает следующим об- 26 разом.

С шины тактовых импульсов 1 сигнал поступает на счетный вход первого пере.счетного устройства 2 и на входы логических устройств стробирования 7 и 8, 2S с выходов которых сигналы поступают на соответствующие входы дешифраторов

5 и 4, на которые также поступают сигналы с пересчетных устройств 2 и 3; сигнал переполнения с первого пересчет- щ ного устройства 2 поступает на второе пересчетное устройство 3. Сигналы с блока управления предустановкой 9. поступают через логическое устройство предустановки 10 на пересчетные устройс вва 2 и 3. Сигналы с выходов дешифраторов 4 и 5 поступают- на матричное коммутирующее устройство 6.

Блок управления предустановкой 9 представлен в виде преобразователя десятичного кода номера канала в двоичный и преобразователь напряжения от . 0 до +4,5 В. Логические устройства предустановки 10 и 11 пре ставляют

:собой логический элемент отрицания НЕ, -" 4$ выходы которых соединены со входами

"уст. 1 соответствующих триггеров пересчетных устройств 2 и 3. Логические устройства стробирования 7 и 8 представляют собой логический элемент отрицания НЕ, выходы которого соединены с входами дешифраторов 5 и 4. Пересчетные устройства 2 и 3 представляют собой ряд счетных триггеров с установочными входами 0 и «1, выход .предыдушего счетчика соединен со счет ным входом последующего. Дешифраторы

4 и 5 представляют собой набор логических элементов И и HE. Входы логи1005308

Составитель Л. Скобелева

Редактор А. Долинич Техред О.Неце Корректор М. Коста

Заказ 1925/77 Тираж 934 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/В

Филиал ППП Патент", r. Ужгород, ул. Проектная, 4