Универсальный логический элемент на @ входов

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 10053l2

Союв Советсккк

Соцкалкстическкк

Реслублкк (72) Авторы кзобретенкя

Ю. А. Кочкарев и В. В. Кондрусе

Таганрогский радиотехнический институт дщ„Ц (71) Заявитель (54) УНИВЕРСАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

НА 1 1 ВХОДОВ

Устройство относится к импульсной технике, а именно к логическим устройствам, используемым в различных областях техники, например, в узлах вычисли- . тельных машйн.

Известны программируемые заранее логические устройства, так называемые пороговые элементы, содержащие выходной операционный усилитель и входные логические или аналоговые функциональные элементы 11 . ю

Недостатками пороговых элементов являются функциональная неполнота при отсутствии функциональных преобразователей и недостаточная надежность и через мерная сложность, вытекающая иэ необхо- 15 димости реализации многопороговости.

Наиболее близким техническим решением к предлагаемому является универсальный логический элемент, содержащий усилитель-формирователь и настраиваемую 2о диодную матрицу, в котором фактически обьединены в одном корпусе микросхемы. входная матрица и часть выходной -матри2 цы, необходимая для реализации одной функции ь логических переменных f 2 ) .

Недостатком указанного элемента является большое количество информационных выводов, равное 2n + 1.

Цель устройства — расширение функциональных воэможностей, что позволит в одинаковых с прототипом корпусах микросхем изготавливать логические схемы с большим значением n .

Указанная цель достигается тем, что в универсальном логическом элементе на и входов, содержащем программируемую диодную логическую матрицу, входы которой соединены с входами логического элемента, содержашую входные и выходные шины, соединенные в местах перекрещивания с помощью диодов, выходные шины логической матрицы обьедине» ны в две группы, в каждой иэ которых выходные шины соединены через резисто ры соответственно с инвертирующнм и неинвертирующим входами дифференциаль ного операционного усилителя, выход

3 10053 которого соединен через резистор с инвертирующим входом и с выходной шиной, неинвертирующий вход усилителя соединен через резистор с общей шиной.

За счет специального представления логической функции число входных шин при этом сокращается до и, а общее число информационных выводов — n -2.

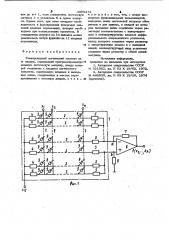

На фиг. 1 приведена принципиальная схема устройства, которое реализует 10 произвольную логическую функцию на и входных переменных; на фиг. 2 — пример конкретной реализации функции 3-х пере- . менных.

Устройство содержит входлую диодную 15 программируемую матрицу 1 с 11 входными шинами 2, на которые поданы входные переменные х,(, Х, ... -,: Хи, и с выходными шинами 3. Первые концы шинЗ через одинаковые резисторы 4 соединены в общий узел и присоединены к источнику питания, а вторые концы разделены на две одинаковые (при четном с ) группы и через одинаковые резисторы 5 соединены в два общих узла с(и b . Указанные узлы присоединены соответственно к инвертируюшему и неинвертируюшему входам дифференциального операционного усилителя 6 с резисторами обратной связи 7 и 8.

Выход усилителя 6 является выходом все-Зо го устройства.

Входные шины 2 соединены с выходными шинами 3 с помощью диодов 9, причем наличие или отсутствие диодного соединения шин определяет ту или иную ло35 гическую функцию предлагаемого элемен.та. Соединение шин может выполняться при изготовлении элемента или использователем известными методами используемыми при программировании логических матриц.

Х1Х (+ Х1 Хз+ Х2ХЗ вЂ” Х.1 Х2Х - Х1 Х2, Х (1-Х )+(1-Х. )Х +Х2Х вЂ” 1-X )Х Х =

=Х -Х Х +ХЗ-Х-1Х3+ Х2/Х -Хд/Х +

2 3 (1 2 1 2 Э) (X„X2+X X ) Устройство работает следующим образом»

Для реализации на нем произвольной логической функции от и переменных, 45 последняя должна быть представлена в так называемой алгебраической форме.

Известно, что все логические операции могут быть заменены некоторыми алгебраическими операциями. В частности, 5О для двух нулевых функций f„(X) и 1 Ь)

E„(X) Vf (X) = f (X)+ f (Х)-f„(X) f (Ê); (a)

f»(x)off(x(=f„(x1f>(x). (Д>

В этих выражениях справа от знака равенства имеет место обычное (алгебраическое) суммирование и умножение.

12 4(Известны также аналогичные выражения и для других логических операций.

Таким образом, любую логическую функцию переменных можно представить в виде алгебраического выражения следующего Вида:

Х )= СО С1 Х.1 С 2+ --+С11Хn

+С Х Х +С Х Х +...+С Х Х С Х А 5

+...+С Х, Х . Х5,-,ХП, Коэффициенты C.< в выражении (3), как правило, принимают значения 0,1 и

-1 и различные варианты коэффициентов полностью задают ту или иную функцию.

Если исходная функция задана в ДНФ, то для получения алгебраической формы достаточно формул (1) и (2) .После получения алгебраической формы реализуемой функции Е (Х. Х2, " хп ) необходимо внутри матрицы 1 соединить шины 2 с шинами 3 диодами 9 так, чтобы от источника питания через резисторы 4 на шинах 3 формировались необходимые конъюнкции или, что то же самое, произведения входных логических переменныМ с соответствующим знаком. Суммирования произведений с соответствующим знаком осуществляется на резисторах 5 с помощью дифференциального усилителя 6, который имеет резисторы 7 и 8 в обратной связи для обеспечения необходимых уровней сигналов.

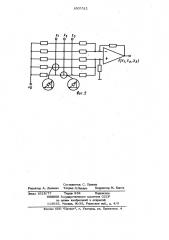

В качестве примера рассмотрим реализацию логической функции

У(Х Х Х )-Х Х VX. X. ЧХ2Х

Преобразуем ее в алгебраическую форму в соответствии с выражениями (1) и (2)

f(Õ,X2 Х )=Х1Х2+Х Х Ч Х2ХЗ

-Х Х2(Х Х» VК х )=Х Х2+Х Х Х2Х

Х Х Х ЫХ Х ГХ Х+ХХ вЂ” ХX Х

12 3 .1 2(1Э 23 1 32

Реализация указанной функции представлена на фиг. 2.

Использование алгебраической формы представления логических функций позволяет уменьшить число внешних информационных выводов микросхемы до 1(+ 2.5 1005312 4 или до и+ 1, если совместить логическую ч а ю шийся тем, что, с целью расматрицу 1 и усилитель 6 в одном корпу- ширения функциональных возможностей, се. Кроме того, при этом отпадает нео -- выходные шины логической матрицы объе ходимость в формировании инверсных зна динены в две группы, в каждой из кото чений входных переменных, которое необ: рых выходные шины соединены через ре ходимо при использовании прототйпа. ц зисторы соответственно с инвертируюстандартном, корпусе на 14 выводов можно шим H неинвертирующим входами диффереализовать. любую функцию на 1 1 входных ренциального- операционного усилителя, переменных. выход которого соединен через резистор

10 с инвертирующим входом и с выходной шиной, неинвертирующнй вход усилителя

Ф о р м у л а и з о 6 р е т е н и я соединен через резистор с общей шиной матрицы.

Универсальный логический элемент на Источники информации, ь входов, содержащий программированную И принятые во внимание при экспертизе диодную логическую матрицу, входы кото- 1. Авторское свидетельство СССР рой соединены с входами логического № 32 1952, кл. Н 03 К 19/02, 1972. элемента, содержащую входные и выход- 2. Авторское свидетельство СССР ные шины, соединенные в местах пере- K 446950, кл. Н 03 К 19/20, 1974 крещивания с помошью диодов, о т л и - 20 (прототип).

Составитель С. Прзнин

Редактор А. йолинич Техред Л,Пекарь Корректор М. Коста

Заказ 1925/77 Тираж 934 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-36, Раушская наб., д. 4/5 филиал ППП "Патент, r. Ужгород, ул. Проектная, 4