Пороговый логический элемент

Иллюстрации

Показать всеРеферат

(72) Автор изобретения

О.Н. Иузыченко (7I) Заявитель (54) ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕИЕНТ

Изобретение относится к автомати-,. ке и вычислительной- технике и может быть использовано для построения различных устройств переработки дискретной информации.

Известен пороговый логический элемент, содержащий многовходовый элемент ИЛИ, входы которого соединены с выходами пяти трехвходовых элементов И, две группы по четыре двухвходовых элемента ИЛИ, соединенных со входами элементов И <1 ).

Недостатком данного элемента является ограниченные функциональные воэможности, так как он реализует . только пороговую функцию семи переменных с порогом 3.

Известен также мажоритарный логический элемент, содержащий преобразователи весов двух входов, состоящие из элемента И и элемента ИЛИ с параллельно соединенными входами,. блок формирования порога и выходной эле мент ИЛИ. Блок формирования порога

2 выполнен двухступенчатым, содержащим два однотипных каскада формирования набора aecos первой ступени, взаимодополняющие весовые выходы которых попарно соединены со входами элемен5 тов И каскада формирования порога второй ступени (2 ;

Недостатком таких устройств явля ется малые функциональные возможнос10

Наиболее близким по технической сущности к изобретению является поро" говый логический элемент, содержащий

К столбцов сумматоров, входы сумматоров первого столбца из которых под" ключены к одним шинам входных сигна îà Г33

Недостатками такого устройства являются сложность технической реалию зации, малые функциональные возможности и быстродействие.

Цель изобретения - повышение быст- родействия и расширение функциональных возможностей.

Для достижения поставленной цели в пороговый логический элемент, содержащий К столбцов сумматоров, входы сумматоров первого столбца подклю чены к шинам входных сигналов, введен элемент ИЛИ, выход которого под" ключен к шине выходных сигналов, а входы - к выходам переноса сумматоров (столбцов от P-го до К-ro, для порога 2Р, выходы каждого из сумма- !О торов столбцов от первого до (P-1)-го подключены к входам одного из сумматоров последующих столбцов, а выходы суммы каждого из сумматоров остальных столбцов подключены к входам од- !5 ного из сумматоров последующих столбцов, при этом входы переноса сумматоров всех столбцов подключены к шинам входных сигналов.

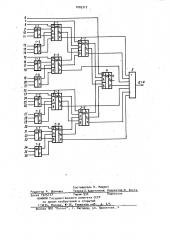

На чертеже изображен предлагаемый пороговый логический элемент для случая числа входов равных тридцати одному и порога a=4.

Предлагаемый пороговый элемент для случая числа входов равных трид- д5 цати одному состоит из сумматоров

1-1-1-8, входы кс-.орых подключены к входным шинам порогового логического элемента, сумматоров 2-1-2-4, 3-1, 3-2 и 4 двухразрядных двоичных чисел, и элемента ИЛИ 5, а также входов 6-36.

Выходы каждых двух сумматоров 1 соединены со входами соответствующего сумматора 2, вход переноса кото35 рого соединен с входом порогового элемента. Выходы суммы сумматоров

2-1 и 2-2 соединены со входами сумматора 3-1, а выходы суммы сумматоров 2-3 и 2-4 — с входами сумматора

3-2. Входы переноса сумматоров 3-1 и 3-2 соединены со входами порогового логического элемента. Выходы суммы сумматоров 3-1 и 3-2 оединены со входами последнего сумматора 4, вход переноса которого соединен со

45 входом порогового логического элемента. Выходы переноса всех сумматоров

P-разрядных двоичных чисел (Р=Iog>a=

=-1og@4=2), т.е. сумматоров 2-1-2-4, 3-1, 3-2, 4, соединены со входами элемента ИЛИ 5, выход которого является выходом порогового логического элемента. функционирование предлагаемого порогового логического элемента про- 55 исходит следующим образом.

На выходах каждого из сумматоров

1 формируется двоичный код числа

317 единичных потенциалов на их входах.

Двоичные коды с выходов каждого из сумматоров 1 поступают на входы соответствующего сумматора 2, на выходах которого при этом формируется двоичный код числа единичных потенциалов на соответствующих семи входах.Так на выходах сумматора 2-1 формируется двоичный код числа m единичных потенциалов на входах 8- 14. Причем на выходе переноса сумматоров

2-1 появляется единичный потенциал, если число m единичных потенциалов на входах 8-14 больше или равно 4.

На выходах суммы сумматора 2-1 появляется код числа t = m-4(m/4).

Двоичные коды с выходов суммы

I сумматоров 2 поступают на входы соответствующего сумматора 3, на выходах которого при этом формируется двоичный код числа t1+tg+tq, где цвоичные коды чисел, поступающие на входы .данного сумматора 3 с выходов суммы соответствующих сумматоров 2, а t3 1, если на вход переноса сумматора 3, соединенный со входом порогового элемента, подан единичный потенциал и tg=0, если на данный вход подан нулевой потенциал. На выходе переноса сумматора 3 появляется единичный потенциал, если t1+tg+t > 4, На выходах переноса сумматора 3 появляется код числа (1+ 2+ з)-4(t„+

+t2+t>)4).

Двоичные коды с выходов суммы сумматоров 3-1, 3-2 поступают на входы сумматора 4, на выходах которого формируется двоичный код числа 1 +С2+й 1 tg двОИ чные кОды чисел

1 t поступающие на входы сумматора 4 с выходов суммы сумматоров 3-1 и 3-2 соответственно, а 1 =1, если на вход переноса сумматора ч подан единичный потенциал, ta 0, если на данный вход подан нулевой потенциал.

На выходе переноса сумматора 4 появляется единичный потенциал, если

t1+ tg+ t 44.

Такйм образом, всякий раз, когда число m единичных потенциалов на входах порогового логического элемента больше или равно 4, на выходах переноса сумматоров 2-х разрядных двоичных чисел 2-1-2-4, 3-1, 3-2, 4 появляется (m/4) единичных потенциалов, например при подаче шИ единичных потенциалов на входы 8-14 порогового элемента единичный потенциал появляется на выходе переноса сумматора

5 10053

2-1. Если на данные входы подано, например, 3 единичных потенциалов, то на выходе переноса сумматора 2-1 будет нулевой потенциал, а на выходах суммы — единичные потенциалы. . s .Если единичный потенциал подан также на один из входов 15-21, это вызы-. вает единичный потенциал на выходе переноса сумматора 3-1. Появление единичного потенциала на любом из выходов переноса сумматоров 2-1-2-4

3-1, 3-2, 4 вызывает единичный потенциал на выходе элемента ИЛИ 5, со входами которого они соединены.

Таким образом, всякий раз, когда число единичных потенциалов на входах порогового логического элемента равно или больше порога о (в рассматриваемом случае а=4), на выходе элемента ИЛИ 5, являющемся выходом 20 порогового логического элемента, появляется единичный потенциал.

Следовательно, предлагаемый пороговый логический элемент обладает значительно большими функциональными возможностями по сравнению с прототипом, так как реализует любую пороговую функцию с порогом а=2 ф=

Ег

=1,2... J!îq (ï+1) (ri-1) от любого числа переменных и. 30

Кроме того, предлагаемый пороговый элемент имеет большее быстродействие, чем прототип. Например, для случая п=31 прототип имеет время задержки Т -†(18-8) ь,где С - время задержки переключения полного сумматора, в зависимости от порядка соединения сумматоров в блоках сложения по модулю два. 8 предлагаемом устройстве при и=-31 и а=4 время задержки равно Т2 3+3 + "3 rAe з время задержки двухразрядного сумматора, ь" — время задержки элемента ИЛИ. В большинстве случаев, можно зз ft принять ь =7 ) с

Ъ 3 3 4$

Например, для элементов серии 155 эти величины составляют ь 480 нс, т (42 нс, 30 нс. При этом т =

=(3-5) еа,т.е. е 2-3 раза меньше, нем

- в прототипе. Причем по мере возрастания п1 выигрыш в быстродействии при использовании предлагаемого устройства возрастает.

Предлагаемое устройство обеспечивает также уменьшение объема обору17 4 дования. дно достигается, во - пер" вых, за счет уменьшения числа оумматоров в схеме, eo - вторых, за счет использования многоразрядных сумматоров, что невозможно в прототипе.

Например, при и =31 прототип соI держит 26 сумматоров (одноразрядных), в то время как предлагаемое устройство для а=4 содержит 22 сумматора (одноразрядных), т.е. на 153 меньше.

При реализации на микросхемах серии

155 прототип требует 26 микросхем, а предлагаемое устройство 15, т.е. почти в два раза меньше.

Таким образом, предлагаемый пороговый логический элемент имеет существенно большие функциональные возможности, большее быстродействие и меньший объем оборудования.

Формула изобретения

Пороговый логический элечент, содержащий К столбцов сумматоров, входы сумматоров первого столбца подключены к шинам входных сигналов, о тл и ч а ю шийся тем, что, с целью повышения быстродействия, упрощения и расширения функциональных возможностей,в него введен элемент

ИЛИ, выход которого подключен к шине входных сигналов, а входы — к выходам переноса сумматоров столбцов от P- го до К-го, для порога 2Р, выходы каждого из сумматоров столбцов от первого до (P- 1)- го подключены к входам одного из сумматоров последующих столбцов, а выходы суммы каждо,го из сумматоров остальных столбцов подключены к входам одного из сумматоров последующих столбцов, при

::этом входы переноса сумматоров всех . столбцов подключены к шинам входных .сигналов.

Источники информации, принятые во внимание при экспертизе

Авторское свидетельство СССР и 598252, кл. н 03 к 19/24, 1.976.

2. Авторское свидетельство СССР и 683025, кл. Н 03 К 19/23, 17,07.79.

3. Авторское свидетельство СССР по заявке И 2782136/21, кл. Н 03 К 19/23, 25. 12.79 (прототип).

1005317

Редактор А. Долинич

Подписное

"/5

7

9

f0

11 г

1В ц

f$

17

19

20, 2f

22

И

2

29

3 ц

Составитель Н. Маркин

Техред E,Харитончик Корректор М. Коста

Заказ 1925/77 1ираж 93

8НИИПИ Государственного комитета СССР по делам изобретений и открытий

113035 Москва Ж- 35 Ра шская наб. филиал ППП "Патент, г. Ужгород, ул. Проектная, 4