Устройство для измерения уровня шума в паузах речи

Иллюстрации

Показать всеРеферат

ОП ИСАНИЙ

Союз Советских

Социалистических

Республик (11 j 1065-321

К АВТОРСКОМУ СВИДЕТЕДЬСМУ (61) Дополнительное к авт. свид-вут" 886264 (56)М%. Кл.

Н 04 В 3/46 (22) ЗаЯвлено 25.03.81 (21) 3264540/18-09 с присоединением заявки ЭЙГэсуттврстеенный ктнннтет (5З) УДК 621.3 ° .052(088.8) (23) Приоритет

Опубликовано 1 .03.83, Бюллетень № 10 по делан изобретений н открытий

Дата опубликования описания 1 5.0 .б„.,;,"; „, 77 a.;;„",, " " /

В,В.Обез, В.М!Смышляев и В.M. орин "Тру., -,.. т

С:,- !; р .. -:, A>: ф,(72) Авторы изобретения (7! ) Заявитель (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УРОВНЯ ШУМА

В ПАУЗАХ РЕЧИ!

Изобретение относится к радиотехнике, может использоваться для определения уровня шума в электроакустических, телефонных и вокодерных системах.

По основному авт. св. V 886264 известно устройство для измерения уровня шума в паузах речи, содержащее генератор импульсов, первый выход которого подключен к входу счетго чика импульсов, а второй выход подключен к первому входу элемента запрета, второй вход которого соединен с выходом сумматора, цифро-аналоговый преобразователь, выход которого

15 подключен ко входу индикатора, последовательно соединенные усилитель, амплитудный детектор и синхронный интегратор, а также импульсно-кодовый модулятор, элемент задержки, эле- щ мент ИЛИ и блок элементов И, при этом и выходов импульсно-кодового модуля-. тора подключены к соответствующим Il входам элемента задержки и к соответ2 ствующим и входам сумматора, и инверсных выходов элемента задержки подключены к соответствующим и входам блока элементов И и к соответствующим другим и входам сумматора, и выходов блока элементов И подключены к соответствующим и входам цифро-аналоговоГо преобразователя, выход счетчика импульсов подключен к и объединенным другим входам блока элементов И и к первому входу элемента ИЛИ, второй вход которого соединен с выходом элемента запрета, выход элемента ИЛИ подключен к тактовому входу элемента задержки, третий выход генератора импульсов подключен к другому входу синхронного интегратора, выход которого подключен к входу импульсно» кодового модулятора Г1.1.

Однако это устройство имеет невысокую точность измерения, Цель-изобретения - повышение точности, 3 10053

Для достижения этой цели в устройство для измерения уровня шума в паузах речи, между выходом блока элементов И и входами цифроаналогового преобразователя, введен блок интерполяции, причем второй выход счетчика импульсов подключен к другому входу блока интерполяции, Причем блок интерполяции содержит последовательно соединенные элемент задержки, вычислитель, первый блок элементов И, блок элементов ИЛИ и второй блок элементов И, а также пороговый блок, выходы которого через компаратор подключены соответственно к входам инвертора, выходы которого подключены к вторым входам первогр блока элементов И и к первым входам третьего блока элементов.И, выходы которого подключенш к другим входам блока элементов ИЛИ, а вторые входы соединены с первыми выходами элемента задержки, инверсные выходы которого подключены к первым входам сумматора, вторые входы которого подключены к входаи элемента задержки, а выходы подключены к входам компаратора, причем входы элемента задержки подключены к другим входам вычислителя, при этом тактовый вход элемента задержки объединен с другими входами третьего блока элементов И, входы элемента задержки и выходы второго блока элементов

И являются соответственно входами и выходами блока интерполяции.

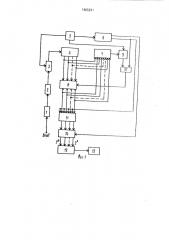

На фиг, 1 представлена структур- ная схема предложенного устройства; на фиг. 2 - структурная схема блока интерполяции.

Устройство для измерения уровня шума в паузах речи содержит усилитель 1, амплитудный детектор 2, синхронный интегратор 3, импульсно-кодовый модулятор (ИКМ) 4, генератор 5 импульсов, счетчик 6 импульсов, сумматор 7, элемент 8 задержки, элемент 9 запрета, элемент ИЛИ 10, блок 11 элементов И, цифро-аналоговый преобразователь. (ЦАП) 12, индикатор 13, блак 14 интерполяции .

Причем блок интерполяции содержит элемент 15 задержки, сумматор

16, компаратор 17, пороговый блок

18, вычислитель 10 среднеарифметического, блоки 20, 21 и 22 эяементов И, инвертор 23, блок 24 элементов ИЛИ.

21

Устройство работает следующим образом.

Синхронный интегратор 3, подсоединенный к входу ИКМ 4, на своем выходе создает дискретизированные сигналы огибающей зашумленной речи, которые следуют с заданной частотой генератора 5 импульсов, При этом частота дискретизации огибающей берется равной 40-50 Гц. С выхода ИКМ 4 сигналы в цифровой форме в параллельном коде поступают на элемент 8 задержки и на первые входы сумматора 7.

В элементе 8 задержки эти сигналы задерживаются на один такт и в инверсном коде подаются на соответствующие другие входы сумматора 7. В результате сложения двух чисел (последующего и инверсного предыдущего) на выходе сумматора 7 появится импульс в том случае, если на первые входы сумматора 7 с ИКМ 4 поступит число большее, чем записанное в элемент 8 задержки. Этот импульс будет запрещать прохождение через элемент 9 запрета тактового импульса на вход элемента 8 задержки и данное число

:не будет в него записано. При посту:,плении с ИКМ 4 числа меньшего, чем записанное в элемейте 8 задержки, на выходе сумматора 7 импульса не будет, и тактовый импульс, пройдя элемент 9 запрета и элемент ИЛИ 10, запишет это число в элемент 8 задержки . Таким образом, в эпемент 8 задержки будет записано минимальное в данном измерительном цикле число, Цикл работы устройства .задается работой счетчика 6 импульсов. При этом время этого цикла должно быть больше вероятного времени следования естественных пауз в речевом сигнале, которое при измерении шума в спектральных каналах вокодера должно быть равным 1,25-1,5 с. С приходом циклового импульса (с первого выхода счетчика 6) в элементе 8 задержки будет записано новое число независимо от того, какое число было записано в нем, и в то же время этот импульс через блок 11 элементов И снимет информацию с элемента 8 задержки, которая поступает в блок интерполяции

14 на элемент задержки 15, на первые входы сумматора 6 и на первые входы вычислителя 19 среднеарифметического, В элементе 15 задержки эта информация задерживается на один такт циклового импульса, который поступает

1005321 формула изобретения

5 со второго выхода счетчика Ь и в инверсном коде поступает на вторые входы сумматора 16, В результате сложения двух чисел (последующего и инверсного предыдущего) на выходе сумматора 16 получается разностное число, которое поступает на схему компаратора 17, на вторые и входовкоторого подается пороговое число с порогового Юлека 18. Порогов« м чис- >0 ло задается путем подключения соответствующих шии к высокому или низкому потенциалу. Если число с выхода сумматора 16 будет больше повоговоt-o числа, то на выходе компаватора

17 будет присутствовать высокий потенциал, который разрешает прохождение через блок 22 элементов И и на блок 24 элементов ВЯИ информации, записаНной в элемент- 15 задержки, в 20 противном случае на выходе комааратора 17 будет присутствовать низкий потенциал, который через инввртор 23 разрешает прехождение через блок 20 элементов И на блок 24 элементов ИЛИ 25 информации с выхода вычислителя 19.

Вычислитель 19 среднеарифметического выполняет операцию сложения предыдущей и последующей информации, а значение среднеарифметического двух щ чисел получается путем отбрасывания младшего разряда полученной суммы.

Подключение информации с выхода блока 24 элементов ВЯИ на вход QAfl 12 через блок 21 элементов И осуществляется цикловым импульсом со второго выхода счетчика 6 импульсов, Таким обрати, на выходе блвка интерполяции 1-4 будет присутствовать кодовая комбннеция N,рввная

В6Н или

N -, если N--N <К, >"" + -1

561 X 2 1

45 где N,N .1- соответственно последующая и предыдущая кодовые комбинации, К - пороговое кодовое число.

Предложенное устройство сохраняет все преимуще ст ва извес тного, и кроме того обеспечивает .точность работы устрой ства, 1. Устройство для измерения уровня шума в паузах речи по авт,,св, Л 886264 о т л и ч а ю щ е е с я тем, что, с целью повышения точности между выходами блока элементов И и входами цифроаналогэвого щюеобразователя введен блок интерполяции, причем второй выход счетчика импульсов подключен к другому вход блока интерполяции.

2, Устрейство по и. 1, о т л и ч а о щ е е с я тем, что блок интер поляции содержит последовательно соединенные элемент задержки, вычислитель, первый блок элементов И,. блок элементов ИМИ и второй блок элементов И, а также пороговый блок, выходы которого через компаратор подключены соответственно к входам инвертора, выхщ ы которого подключены к вторым входам первого блока элементов

И и к первым входам третьего блока элементов И, выходы которого подключены к другим входам блока элементов

ИЛИ, а вторые входы соединены с первыми выходами элемента задержки, инверсные выходы которого подключены к первым входам сумматора, вторые входы которого подключены к входам элемента задержки, а выходы подключены к входам компаратора, причем входы weмента задержки подключены к другим входам вычислителя, при этом тактовый вход элемента задержки объединен а с другими вжодами третьего блока элементов И, входы элемента задержки и выходы второго блока элементов И являются соответственно входами и выходами блека интерполяции.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Ю 886264, кл. H 04 В 3/46, 1981. (прототип), 1005321

10053 21

8ыхо

Фиг2

Составитель Т.Колпикова

Редактор А.Долинич. Техред С.Иигунова Корректор Ю.Иакаренко

Заказ 1927/78 Тираж 675 Подписное

ВНИИПИ Государственного. комитета СССР по делан изобретений и открытий

113035, Москва, Ж-35, Рвушская наб., д. 4/5

Фил ал ППП "Патент", r. Ужгород, ул. Проектная, 4