Устройство для ввода информации

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ , содержащее клавиатуру, выходы которой соединены с входами шифратора , выходы которого соединены с входом первого блока памяти и одними входами второго блока памяти, элементы И, ИЛИ, группы элементов И, ИЛИ, отличающееся тем, что, с целью повышения надежности устройства, в него введены счетчик, делители частоты, триггер и распределитель импульсов, выходы группы которого соединены с другими входами второго блока памяти и первыми входами элементов И группы, вторые входы которых соединены с выходами делителей частоты, выходы элементов И группы соединены с входами элемента ИЛИ, выход которого соединен с первым входом счетчика, выход которого соединен с вторым входом распределителя импульсов и вторым входом счетчика, первый выход распределителя импульсов .соединен с первым входом триггера, второй вход которого является первым входом устрой-, ства, выход триггера соединен с первым входом распределителя импульсов и первым входом элемента И, второй вход которого является аторым вхо дом устройства выход, элемента И соединен с входом делителя частоты и является выходом-устройства, выходы второго блока памяти соединены поразрядно с входами элементов ИЛИ группы, выходы которых соединены с входами группы счетчика, а В191ходы , первого блока памяти соединены с входа ми группы распределителя импульсов. СО О)

СОЮЗ СОВЕТСНИХ СОЦИАЛИСТИЧЕСКИХ

РЕСПУбЛИК, Я0„„100709

Зщ) а 06 F 3/02

ОПИСАНИЕ ИЗОБРЕТЕН И с йМ

К ABTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21 ) 2992204/18-24 (22) 10. 10. 80 (46) 23.03.83 Бюл. Н 11 (72) А.К. Мерзляков, Л.А. Фомин

Л.И. Жук и Ю.С. Пономарев (53)681.327.11 (088.8) (56) 1. Авторское свидетельство СССР

Р 744535, кл. G 06 F 3/02» 1978

2. Авторское свидетельство СССР

N 744536, кл. G 06 F 3/02, 1980 (npoyox n l .. (54)(57) УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ, содержащее клавиатуру, выходы которой соединены .с входами шифрато-. ра, выходы которого соединены с входом первого блока памяти и одними входами второго блока памяти, элементы И, ИЛИ, группы элементов И, ИЛИ, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, в него введены счетчик, делители частоты, триггер и распределитель импульсов, выходы группы которого соединены с другими входа.- ми второго блока памяти и первыми входами элементов И группы, вторые входы которых соединены с выходами делителей частоты, выходы элементов

И группы соединены с входами элемен" та ИЛИ, выход которого сьединен с первым входом счетчика, выход кото рого- соединен с вторым входом распределителя импульсов и вторым входом счетчика, первый выход распределителя импульсов .соединен с первым входом триггера, второй вход кото" рого является первым входом устрой-:.. ства, выход триггера соединен с пер" вым входом распределителя импульсов и первым входом элемента И, второй вход которого является вторым вхо:дом устройства» выход. элемента И соединен с входом делителя часто" ты и является выходом устройства, выходы второго блока памяти соеди" иены поразрядно с входами элементов

ИЛИ группы, выходы которых соединены с входами группы счетчика, а выходы

riepsoro блока памяти соединены с входами группыраспределителя импульсов. ства для ввода информации.

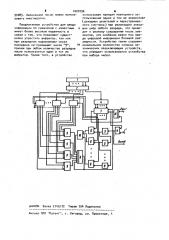

Устройство содержит клавиатуру

1 набора чисел, шифратор 2, второй блок 3 памяти, первый блок 4 памяти е а элементы ИЛИ р счетчик б (перестра 1ваемый), распределитель 7 импульсов (управляемый), элементы И 8 группы, делители 9 (декадные), элемент ИЛИ

10, элемент И 11, триггер 12.

Первый блок 4 памяти является блоком памяти нулей, второй блок 3 памяти является блоком памяти чисел.

Устройство работает следующим образом.

Заданное число набирается на клавиатуре 1 и кодируется в шифраторе 2. Каждый значащий разряд записывается в элемент второго блока 3 памяти, который может быть выполнен как линейка триггеров для записи чисел от 1 до.9. Каждый разряд запи сывается в свою ячейку;

Выход каждого элемента второго блока 3 памяти подключен через элементы ИЛИ 5 группы на вход счетчика

33

-6. На чертеже показаны четыре выхода каждого элемента второго блока 3 памяти, так как для записи числа

"9" требуется четыре двоичных элемента. Элементы второго блока 3 памяти осуществляют хранения значащих цифр каждого разряда. Нули записываются в свой элемент первого блока

4 памяти. Такой подход связан с тем, ij что соответствующий разряд, в котором записан "нуль", необходимо исключить из счета. Это достигается следующим образом. При записи в какой-либо разряд нуля с элемента памяти нулей .появляется управляющий сигнал, воздействующий на основной вход распределителя 7 импульсов, Задачей этого распределителя является поочередное подключение тех разрядов, в которых имеются значащие цифры и исключение тех разрядов, в которых записаны "нули". С шифратора 2 сигналы, соответствующие нулям какого-то разряда воздействуют на

1 1

Изобретение относится к вычислительной технике и может быть исполь зовано в вычислительных устройствах для ввода цифровой информации s последовательном коде.

Известно устройство для ввода информации, содержащее блоки памяти, клавиатуру, регистры для записи чисел, шифраторы, элементы И, ИЛИ, блоки управления 51 1 .

Недостатком известного устройства является недостаточная надежность, Наиболее близким техническим ре.шением к изобретению является устрой ство для ввода информации, содержаще клавиатуру, выходы которой соединены с входами шифратора, выходы которого соединены с входом первого блока памяти и одними входами второго блока памяти, .элементы И, ИЛИ, блоки индикации, коммутатор, преобразователь кодов и дешифратор (2 j .

Недостатком известного устройства является недостаточная надежность г ри последовательном считывании информации, Цель изобретения - повышение надежности устройства.

Указанная цель достигается тем, что в устройство для ввода информации, содержащее клавиатуру, выходы которой соединены с входами шифратора, выходы которого соединены с входом первого блока памяти и одними входами второго блока памяти, элементы И, ИЛИ, группы элементов

И, ИЛИ, дополнительно введены счетчик, делители частоты, триггер и распределитель импульсов, выходы группы которого соединены с другими входами второго блока памяти и первы ми входами элементов И группы, вторые входы которых соединены с выходами делителей частоты, выходы элементов И группы соединены с входами элемента ИЛИ, выход которого соединен с первым входом счетчика, выход которого соединен с вторым входом распределителя импульсов и вторым входом счетчика, первый выход распределителя импульсов соединен с первым входом триггера, второй вход которого является первым входом устройства, выход триггера соединен с первым входом распределителя импульсов и первым входом элемента И, второй вход которого является вторым входом устройства, выход элемента

И соединен с входом делителя часто007096 2 ты и является выходом устройства, выходы второго блока памяти соединены поразрядно с входами элементов

ИЛИ группы, выходы которых соединены с входами группы счетчика, а выходы первого блока памяти соединены с входами группы распределителя импульсов.

На чертеже показана функциональ1ф ная блок-схема предложенного устрой07096 (дополнительный ) вход распределитеt0 6 через элемент ИЛИ 5 группы. ИмИмпульсы подаются на второй вход устройства (f). Считывание числа в данном устройстве осуществляется в последовательном коде.

При подаче сигнала "Пуск" на второй (единичный) вход триггера 12 последний срабатывает и высокий потенциал прикладывается к второму.в входу элемента И 11. Импульсы поступают на делитель 9, соответствую-щий старшему разряду, в .котором имеется значащая цифра. Одновременно сигнал поступает на выход устройства - клемму "Выход". Сигнал с триггера 12 поступает также,на первый

3 -10 свой управляющий вход распределителя

7 импульсов. На основном выходе распределителя импульсов не появляется сигнал, который при. наборе значащей цифры приложен к первому входу элемента И 8 группы соответствующего разряда, за счет чего исключается соответствующий декадный делитель

9, а также осуществляется переход через элементы второго блока 3 памяти рассматриваемого разряда. Таким. образом, на выходах группы распределителя 7 импульсов, а также на первых входах элементов И 8 группы в . соответствии с набранным числом нулевых разрядов отсутствуют управляющие сигналы, и соответствующие им делители 9 исключается из счета. Например, при наборе числа 90085 на втором и третьем выходе не появляется управляющих сигналов, они исключаются — в первый элемент второго блока 3 памяти записывается число

"9", в четвертый и пятый элементычисла "8" и "5" соответственно.

Механизм образования набранного, числа состоит в поразрядном сложении числа импульсов. Так, для рассмотренного ранее примера число

90085 будет, получено путем суммирования чисел 90000+80+5. Э о достигается счетом импульсов с помощью счетчика, образованного четырьмя делителями 9 и перестраиваемым счетчиком 6, т.е. 10 ° 10-10-10 9, затем счетчиком, образованным одним декадным делителем 9, последовательно включенным с перестраиваемым счетчиком 6, т.е. 10 8, и, наконец, перестраиваемым счетчиком, в котором записано число "5". Таким образом, на. выходе будет полученное число, записанное в память чисел 3 и нулей 4.

И

3$

43

35 ля 7 импульсов, осуществляя его hepeход в первое состояние. В этом случае на выходах группы (если имеется значащая цифра в данном разряде ) появляется управляющий сигнал, который прикладывается к списывающим входам второго блока 3 памяти, осуществляя списывание из него числа в счетчик пульсы подсчитываются делителями 9, которые включены последовательно.

При этом на входе элемента ИЛИ 10 появляются импульсы последнего делителя 9, так как на соответствующем ему втором входе элементов И 8 группы приложен высокий потенциал, снимаемый с распределителя 7 импульсов..

С выхода элемента ИЛИ 10 импульсы поступают на вход счетчика 6, в котором в данном случае записано число

В результате получен первый член суммы — 90000.

По окончании счета первой суммы появляется сигнал с выхода счетчика

6, который устанавливает себя в исходное состояние и выдает сигнал на второй (дополнительный) вход рас" пределителя 7 импульсов. Распределитель 7 импульсов выдает сигнал для счета очередного разряда, в котором есть значащая цифра. В данном случае в следующих двух разрядах записаны нули, поэтому на выходах группы распределителя 7 импульсов появляется сигнал, который нрикладывается к первому входу элементов И 8 группы соответствующего счету четвертого разряда. Одновременно сигнал подается на другие (считывающие) входы второго блока 3 памяти, в котором записано для данного Примера число

"8". Это число переписывается в счетчик 6. Счет очередного члена суммы осуществляется аналогично.

Таким же образом получают и последний член суммы. После .образования всей суммы счетчик 6 устанавливается в исходное состояние, с первого выхода распределителя 7 импульсов снимается сигнал на первый ..(установочный) вход триггера 12, который опрокидываясь, снимает высокий потенциал с первого входа элемента

И ll. Импульсы с второго входа (x") устройства не поступают в схему, В результате, на выходе устройства появляется число импульсов, записанное в памяти, в данном случае

5 1007096 е

90085. Записанное число можно исполь- использован. принцип повторного ис" зовать многократно. пользования одних и тех же элементойг (декадных делителей и перестраивае-

Предлагаемое устройство для ввода мого счетчика) лри реализации знача" информации по сравнению с известным s щих цифр любого разряда, что привоимеет более высокую надежность в дит к резкому сокращению числа элесвязи с тем, что позволяет сущест- ментов, что особенно важно при ввовейно упростить шифратор, так как де цифровой информации большой разори разрядном кодировании чисел рядности. Устройство также содержит последние не превышают число "9", 1© минимальное количество сложных мепричем при любом количестве разрядов ханических переключающих устройств, числа используется один и тот же что упрсицает использование устройства шифратор. Кроме того, в устройстве при наборе чисел. оНИИПИ Заказ 2140/72 Тираж 704 Подписное филиал ППП "Патент", r. Ужгород, ул, Проектная> 4