Устройство для изменения частоты следования импульсов

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ИЗМЕНЕНИЯ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ, содер|Жащее элемент ИЛИ, делитель частоты, счетчик, блок , генератор опорной частоты, первый выход которого соединен с входом счетчика, выходы блока коммутгщии подключены к входам элемента ИЛИ, выход которого соединен с входом делителя частоты, выход которого подклк чен к выходной шине устройства, отличающееся тем, что, с целью повьшения точности, в него введены дешифратор , п элементов ИЛИ и блок временной задержки, вход которого,подключен к второму выходу генератора опорной частоты, разрядные выходы счетчика соединены с входгьми дешифратора , выходы которого соединены с входами п элементов ИЛИ, выходы которых подключены к первым входам блока коммутации, вторые входы которого (Л соединены с выходами блока временной задержки. ш о ф

QQO3 ССВЕТСНИХ

hNUAI

PEQAVSlNH

3(5

ГОСУДАРСТВЕННЫЙ НОНИТЕТ СССР

Д 9 рЮ

ОПИСАНИЕ ИЗОБРЕ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3308788/18-21 (22) 02.07.81 (46) 23.03.83. Вюл. В 11 (72) И. Г. Комин и В. И. Елфимов (71) Уральский ордена Трудового Красного Знамени политехнический институт им. С. N. Êèðîâà (53) 621.317 ° 7(088.8) (56) 1. Авторское свидетельство СССР

В 570203, кл. Н 03 К 23/00, 1975.

2. Князев Ю. N. и Петров Н. С.

Цифровой свип-генератор. Сб. "Методы и аппаратура спектрального и корреляционного анализа сложных сигналов". Таганрог, 1974, вып. I, с. 197-202 (прототип), (54)(57) УСТРОЙСТВО ДЛЯ ИЗМЕНЕНИЯ

ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ, содер:,жащее элемент ИЛИ, делитель частоты, счетчик, блок коммутации, генератор

„„SU„„1007199 опорной частоты, первый выход которого соединен с входом счетчика, выходы блока коммутации подключены к входам элемента ИЛИ, -выход которого соединен с входом делителя частоты, .выход которого подключен к выходной шине устройства, о т л и ч а ю щ ее с я тем, что, с целью повыаеиия точности, в него введены дешифратор, и элементов ИЛИ и блок времЕнной задержки, вход которого.подключен к второму выходу генератора опорной частоты, разрядные выходы счетчика соединены с входами дешифратора, выходы которого соединены с входами и элементов ИЛИ, выходы которых подключены к первым входам блока Е, коммутации, вторые входы которого соединены с выходами блока временной задержки.

С.

1007199

Изобретение относится к импульсной технике и может быть использовано как источник импульсной последовательности с изменяющейся частотой по заданному закону, а также для формирования сигналов со сложной 5 частотной модуляцией.

Известно устройство для изменення частоты следования импульсов по линейному закону, содержащее опорный генератор, счетчик, дешифратор, коммутатор (1) .

Однако это устройство формирует только импульсы кусочно-линейной функциональной зависимости.

Наиболее близким к изобретению 15 является устройство для изменения частоты следования импульсов, содержащее опорный генератор, счетчик, дифференцирующие цепочки, блок коммутации, дополнительный счетчик, 20 элемент ИЛИ и выходной делитель. Выход опорного генератора соединен с входом счетчика, выходы разрядов которого через дифференцирующие цепочки подключены к блоку коммутации, вторая группа входов которого соеди-, нена с выходами дополнительного счет-! . чика, вход которого соединен с выхо; дом счетчика, выходы блока коммутации соединены с входами элемента

ИЛИ, выход которого подключен к входу делителя частоты, выход которого соединен с выходом устройства(2).

Однако это устройство не обеспечивает высокой точности формирования заданного закона изменения частоты из-за дискретности переключения частоты следования импульсов и наличия в выходном сигнале паразитных составляющих, возникающих при неравномерном распределении импуль- 40 сов во времени.

Целью изобретения является повышение точности.

Поставленная цель достигается тем, что в .устройство для изменения 45 частоты следования импульсов, содержащее элемент ИЛИ, делитель частоты„ блок коммутации, счетчик, генератор опорной частоты, первый выход которого соединен с входом счетчика, выходы блока коммутации подключены к входам элемента ИЛИ, выход которого соединен с входом делителя частоты, выход которого подключен к выходной шине устройства, введены дешифратор, и элементов ЙЛИ и блок временной задержки, вход которого подключен к второму выходу генератора опорной частоты, разрядные выходы счетчика соединены с входами дешифратора, выходы которого оеди- 60 нены с входамл и элементов ИЛИ, выходы которых подключены к первым входам блока коммутации, вторые входы которого соединены с выходами блока временной задержки.

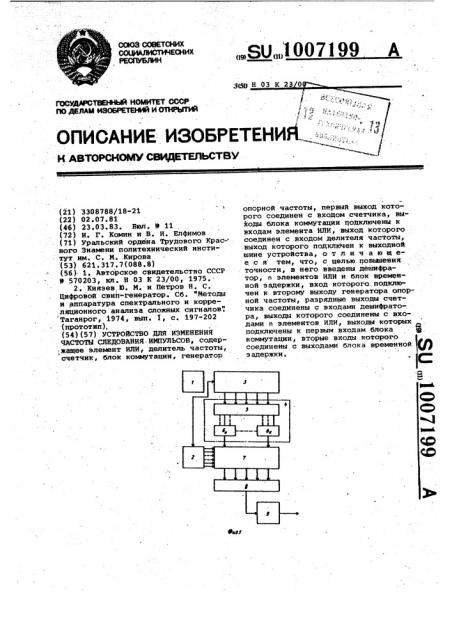

На фиг. 1. приведена блок-схема предлагаемого устройства; на фиг.2временные диаграммы работы устрой ства.

Устройство содержит генератор 1 опорной частоты, блок 2 временной задержки, счетчик 3, вычислитель 4, состоящий из дешифратора 5 и и элементов ИЛИ б, блок 7 коммутации, элемент ИЛИ 8 и делитель 9 частоты. р и м е р. Пусть закон изменения времени появления импульсов на выходе устройства определяется выражением

d (; )x < (1) где 1 = О, 1, 2 ° .. k — номер импульса на выходе с начала отсчета

О

d — коэффициент пропорциональности, x - целое число.

В частном случае формирователя сигнала при х = 1 выражение (1) принимает вид

d(i) (2)

В каждом интервале времени t с начала отсчета укладывается число и импульсов 1

I (3)

При п= 01 си d = 1 с, n = 10 i где = О, 1, 2, ... k число опорных импульсов íà i-ом интервале времени равно па О, п = 100, п2 14 1," и = 17 3 п = 22,4; п = 24,5 .. ° п4 = 10 - k

Числа п2, п, п, и© ... имеют

Дробную часть. Счетчик 3 считает целые числа импульсов, которые укладываются между нулевым и 1-ым моментом времени. На выходах дешифратора

5 появляются импульсы длительностью о после подсчета числа импульсов в соответствии с выражением и ° - Епй (n„J Епй (10 -P) (4) где Епс (х) - целая часть числа х.

Импульсы появляются на соответствуницих выходах дешифратора 5 oiañле подсчета следующего. числа импульсов (4) mî О, m 10, @2= 14, а = 17, m4= 20, в = 22, Часть моментов времени t будет точно соответствовать выражению (2)

О, 1, 4., 9, 16 ... или m = О, m<= 10 m = 20, Назначением вычислителя 4, состоящего цз дешифратора 5 и п элементов

ИЛИ б, является формирование на выходах и элементов ИЛИ 6 управляющих импульсов, поступающих на первые

1007199

65 входы блока 7 коммутации, в соответствии с сигналами разрядных выходов счетчика 3. Выходы дешифратора 5 разбиты на группы. В первую группу вклю» чаются выходы, которые соответствуют точному значению временных интервалов t,ã пгр 0; в = 10; m<= 20; а также близкйе к ним интервалы времени, например в 14.

Другие группы выходов дешифрато-ра 5 организуются s.соответствии с выражением

М = Ent tp(n i - Ent (пг1 ) + 0,5 =

Ent (p(n„ - m„) + 0,51 . (5)

Вторая группа выходов соответствуе™ - 1 m - 17г щ 5= 22 ms= 28, Э

° ° ° °

Третья группа образуется из выходов дешифратора 5, для которых М" 2 в = 24; п1 =, 26 пг„о= 31 и т.д. Кажцая из групп выходов дешифратора 5 подключается к своему элементу ИЛИ из и элементов ИЛИ бг первая — к элементу ИЛИ с нулевым номером, вторая к элементу ИЛИ с первым номером, третья - к элементу ИЛИ с вторым номером и т.д.

В соответствии с заложенным в вычислителе 4 алгоритмом с выхода генератора 1 импульсы опорной часто. ты с периодом следования о поступают на счетчик 3, увеличивая величину

его кода. Дешифратор 5 формирует импульсы согласно кодовым сигналам разрядных выходов счетчика 3.

На фиг. 2 представлены временные диаграммы: CI — напряжение на выходе генератора 1; S — напряжение на выходе элементов ИЛИ б с нулевым номером; Ь вЂ” напряжение на выходе элемента ИЛИ б с перзым номером;

- напряжение на выходе элемента

ИЛИ б со вторым номером; g — напряжение на выходе элемента ИЛИ б с третьим номером.

Импульсы с входов и элементов

ИЛИ 6 поступают на первые входы блока 7 коммутации, на вторые входы которого поступают импульсы с соответствующих выходов блока 2 временной задержки. Блок 2 обеспечивает на выходах импульсы опорной частоты с задержкой, определяемой из выражения

I " + ) р (6) где М„ находится из формулы (5) для каждого временного интервала с момента начала отсчета.

Для блока 2 р 3 (фиг. 2) приведены -следующие временные диаграьвай:

8. - напряжение опорной частоты, импульсы которой имеют нулевую задержку с момента начала отсчета (нулевой выход блока 2 временной задержки); Ж - напряжение опорной час5

40 тоты на первом выходе блока 2, импульсы которого задержаны относительно исходных на вРемЯ g ег ьр/(Р+1)г, напряжение опорной частоты на втором выходе блока 2," и †.напряжение опорной частоты на третьем выходе блока 2 временной задержки. Каждая из данных последовательностей (фиг. 2,8 — U ) .отличаются друг от друга величиной задержки от и tn О до гг tg = 3с р/(p+1) 3 2р/4, В блоке 7 коммутации происходит сравнение временного положения импульсов с выходов элементов ИЛИ 6 и с выходов блока 2 временной задержки. Так как на выходе элемента ИЛИ 6 с нулевым номером имеется импульсная последовательность, представленная на фиг. 2 5 а соответствукщая ей последовательность с выхода блока 2 приведена на фиг. 2Â, поэтому на выход блока 7 коммутации проходят импульсы опорной частоты в интервалы времени, соответствующие выходам дешифратора 5г во, m<, m<, m4, . ° .

Также импульсная последовательность на выходе элемента ИЛИ 6 с пер-. вым номером (фиг. 25) сравнивается в блоке 7 коммутации с напряжением первого выхода блока 2 (фиг. ЗЖ ) и на выходе 7 коммутации проходят импульсы опорной частоты, задержанные на время ггпу = со/(р+1), в интервалы времени, соответствующие выходам дешифратора 5г аЗ m5 m8 ° ° акое же сравнение задержанной импульсной последовательности. опорной частоты и выходных сигналов элемен-; тов ИЛИ происходит в блоке 7 коммутации и для других номеров. В ре зультате на выходе элемента ИЛИ 8 имеется импульсная последователь- ° ность вида фиг. 2 к . Делитель 9 пре,образуют импульсы фиг. 2к в последо-. вательность вида фиг. 2д.

Таким образом происходит формирование импульсной последовательности с заданным законом изменения частоты,. причем перггод повторения закона изменения частоты определяется объемом счетчика 3.

Использование в устройстве вычислителя и блока временной задержки позволяет повысить точность формирования импульсной последовательности импульсов в заданные моменты времени.

Ввиду отсутствия в выходной импульсной последовательности побочных, (паразитных) составляющих, устройство позволяет снизить коэффициент деления делителя до двух для формирования сйгнала, представленного на фиг. 2 А, что приводит к увеличению в k/2 раз верхней граничной частоты формируемого сигнала, где

1007199

Составитель Н. Каплин

Редактор Г. ус Техред T.Маточка Корректор A.Äýÿòêî

Заказ 2154/74 Тираж 934 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская иаб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 коэффициент деления выходного делителя известного устройства.

Изобретение позволяет формировать

cHríàëû с большими значениями скорости изменения частоты следования импульсов и девиации частоты. Уст ройство может формировать импульсы с изменяющейся частотой следования по любому закону

f(e) i st + f о

5 путем изменения алгоритма работы вычислителя согласно формуле (1) .