Синтезатор частоты

Иллюстрации

Показать всеРеферат

1. СИНТЕЗАТОР ЧАСТОТЫ, со держащий последовательно соединенны опорный генератор, делитель частоты и частотно-фазовый детектор, последовательно соединенные фазовый корректсф , интегратор, фильтр нижних частот, управляемый генератор и делитель частоты с переменным коэффициентом деления, выход которого сое динен с другим сигнальным входом ча тотно-фазового детектора, а также формирователь импульсов, вход и выход которого соответственно соеди нены с другим выходом делителя частоты и управлякицим входом фазового корректора, отличающийся тем, что, с целью уменьшения потреб ления энергии питания, введены первый и второй ключи и последовательн соединенные датчик синхронизма, формирователь управляющих сигналов и третий ключ, другой вход которого подключен к шине питания, первые управляющие входы частотно-фазового детектора, делителя tacToxtj рователя импульсов и делителя частоты с nepeffieHHfcJM коэффициентом деления объединены и подключены , к выходу третьего ключа, вторые управляющие входы частотно-фазового детектора, делителя частоты, формирователя импульсов и делителя частоты с переменным коэффициентом деления объединены и подключены к второму выходу формирователя управляктщх сигнгшов, первый ключ включен между первым выходом частотнофазового детектора и первым входом фазового корректора, а второй ключ включен между вторым выходом частотно-фазового детектора и вторым входом фазового корректора, управляющие входы первого и второго ключей объединены и соединены с третьим выходом формирователя управляющих сигналов, а входы датчика синхронизма подключены соответственно к первому и второму выходам частотно-фазового детектс« )а.

09) Ol) ЗСЮ Н 03 L 718

ГОСУДАРСТВЕННЫЙ KOMHTKT ССОР

fO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

OnN0AHNE NS06PETE ."".

К ABTOPCKOMV СНИДЕТЕЛЬСТВУ (21) 3309790/18-09 (22) 18.06.81 . (46) 23.03. 83. Бюл. 9 11 (72 ) С.К. Романов, В. Н. Малиновский, Н.М. Тихомиров и С.К. Синюков (53) 621 373,.42(088.8) (56) 1 . Патент Франции Р 2148920, кл. Н 03 К 1/00, 23.03.73.

2. Патент CtQA Р 4023116, кл. 331-17, 10.05.77 (прототип). (54) (57) 1. СИНТЕЗАТОР ЧАСТОТЫ, содержащий последовательно соединенные опорный генератор, делитель частоты и частотно-фазовый детектор, последовательно соединенные фазовый корректор, интегратор, фильтр нижних частот, управляемый генератор и делитель частоты с переменным коэффициентом деления, выход которого соединен с другим сигнальным входом частотно"фазового детектора, а также формирователь импульсов, вход и выход которого соответственно соединены с другим выходом делителя частоты и управляющим входом фазового корректора, отличающийся тем, что, с целью уменьшения потреб-. леийя энергии питания, введены пер- . вый и второй ключи и последовательно соединенные датчик синхронизма, формирователь управляющих сигналов и третий ключ, другой вход которого подключен к шине питания, первые управляющие входы частотно-фазового детектора, .делителя частоты> форми-рователя импульсов и делителя частоты с переменным коэффициентом деления объединены и подключены, к выходу третьего ключа, вторые управляющие входы частотно-фазового детектора, делителя частоты, формирователя импульсов и делителя частоты с переменным коэффициентом деления объединены и подключены к второму выходу формирователя управляющих сигналов, первый ключ вклю- Я чен между первым выходом частотнофазового детектора и первым входом фазового корректора, а второй ключ включен между вторым выходом частот но-фазового детектора и вторым входом фазового корректора, управляющие входы первого и второго ключей объединены и соединены с третьим выходом формирователя управляющих сигналов, а входы датчика синхронизма подключены соответственно к первому и второму выходам частотно-фазового де,тектора.

1007202

2. Синтезатор по п.1, о т л и ч а ю шийся тем, что формирователь управляющих сигналов содержит последовательно соединенные элемент задержки, первый формирователь импульсов и первый элемент ИЛИ, последовательно соединенные второй формирователь импульсов и второй элемент ИЛИ и последовательно соединенные третий формирователь им пульсов и элемент И, а также р-триггер, 5-вход. которого является входом формирователя управляющих сигналов, Изобретение относится к радиотехнике и может быть использовано, например, в приемопередающей аппара- . туре связи.

Известны синтезаторы частоты, 5 содержащие группу перестраиваемых генераторов с коммутируемой цепью управления, включающей в себя делитель частоты с переменным коэффициентом деления, фазовый детектор, фильтр10 нижних частот и ключи j1) .

Недостатком этого синтезатора является большое потребление энергии питания.

Наиболее близким по технической сущности к изобретению является синтезатор частот, содержащий последовательно соединенные опорный генератор, делитель частоты и частотнофазовый детектор, последовательно соединенные фазовый корректор, интегратор, фильтр нижних частот, управляемый генератор и делитель частоты с переменным коэффициентом деления, выход которого соединен с другим сигнальным входом частотно-фазового детектора, а также формирователь импульсов, вход и выход которого соответственно соединен с другим выходом делителя частоты и управляющим входом фазового корректора $2(.

Однако известный синтезатор. также потребляет большое количество энергии от источника питания.

ЦелЬ изобретения — уменьшение потребления энергии питания.

Поставленная цель достигается тем, что в синтезатор частоты, содержащий последовательно соединенные опорный генератор, делитель частоты, и частотно-фазовый детектор, после- 40 довательно соединенные фазовый корректор, интегратор, фильтр нижних частот, управляемый генератор и делитель частоты с переменным коэффициентом деления, выход которого сое- 45 прямой выход 0-триггера подключен к другим входам первого и второго элементов ИЛИ, а инверсный выход

U-триггера соединен с другим входом элемента И, тактовый вход О-триггера и входы элемента задержки, второго и третьего формирователей объединены и подключены к выходу мультивибратора, при этом выходы элемента H„ второго элемента ИЛИ йпервого эле-. мента ИЛИ являются соответственно первым, вторым и третьим выходами формирователя управляющих сигналов. динен с другим сигнальным входом час тотно-фазового детектора, а также формирователь импульсов, вход и выход которого соответственно соединены с другим выходом делителя частоты и управляющим входом фазового корректора, введены первый и второй ключи и последовательно соединенные датчик синхронизма, формирователь управляющих сигналов и третий ключ, другой вход которого подключен к ши не питания, первые управляющие входы частотно-фазового детектора, делителя частоты, формирователя импуль6сов и делителя частоты с переменным коэффициентом деления объединены и подключены к выходу третьего ключа, вторые управляющие входы частотнофазового детектора, делителя частоты, формирователя импульсов и делителя частоты с переменным коэффициентом деления объединены и подключе,, ны к второму выходу формирователя управляющих сигналов, первый ключ включен между первым выходом частотно-фазового детектора и первым входом фазового корректора, а второй

-ключ включен между вторым выходом частотно-фазового детектора и вторым входом фазового корректора, управляющие входы первого и второго ключей объединены и соединены с третьим выходом формирователя управляющих сигналов, а входы датчика

:синхронизма подключены соответственно к первому и второму выходам частотно-фазового детектора.

Кроме того, формирователь управ ляющих сигналов содержит последовательно соединенные элемент задержки, первый формирователь импульсов и первый элемент ИЛИ, последователь но соединенные второй формирователь импульсов и второй элеМент ИЛИ и последовательно соединенные третий формирователь импульсов и элемент И, 1007202а также D-триггер, .S-вход которого, является входом формирователя управляющих сигналов, прямой выход 0-триггера подключен к другим входам первого и второго элементов

ИЛИ, а инверсный выход D -триггера соединен с другим входом элемента И, тактовый вход D-триггера и входы элемента задержки, второго и третьего формирователей объединены и подключены к выходу мультивибратора, при этом выходы элемента И, второго элемента ИЛИ и первого элемента ИЛИ являются соответственно первым, вторым и третьим выходами формирователя управляющих сигналов;

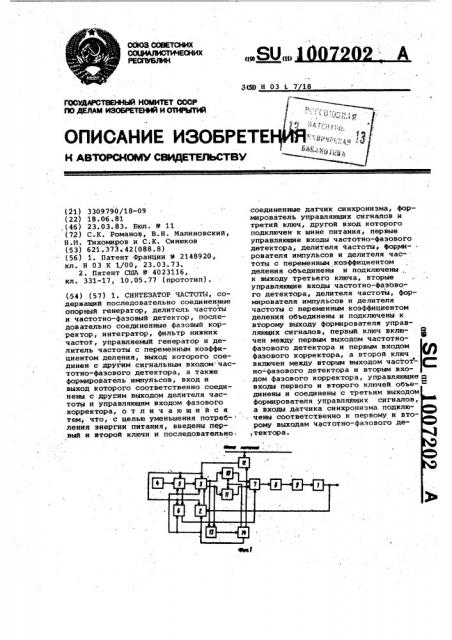

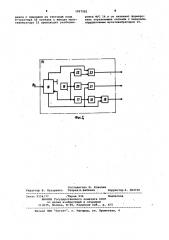

На фиг. 1 приведена структурная схема синтезатора частоты; на. фиг. 2 — схема формирователя управляющих сигналов.

Синтезатор частоты содержит управляемый генератор 1, делитель с переменным коэффициентом деления (ДПКД) 2, частотно- фазовый детектор (ЧФД) 3, опорный генератор 4, делитель частоты 5, формирователь импульсов б, фазовый корректор 7, интегратор 8, фильтр нижних частот (ФНЧ) 9, первый ключ 10, второй ключ 11, третий ключ 12, датчик синхронизма 13, формирователь управляющих сигналов (ФУС) 14.

Формирователь управляющих сигналов содержит мультивибратор 15, D-триггер .16, элемент 17 задержки, первый формирователь импульсов 18, первый элемент ИЛИ 19, второй формирователь импульсов 20, второй элемент ИЛИ 21, третий формирователь импульсов 22, элемент И 23.

Синтезатор частоты работает следующим образом.

В отсутствии режима синхронизма на выходе датчика синхронизма 13 появляется сигнал, блокирующий работу ФУС 14. При этом с первого и второго выходов ФУС 14 на управляющие входы первого ключа 10, второго ключа 11 и третьего ключа 12 поступают сигналы, под действием которых эти ключи замыкаются и работает коль цо фазовой автоподстройки.

В режиме синхронизма с выхода датчика синхронизма 13 на вход

ФУС 14 поступает сигнал блокировки и ФУС 14 формирует на своих выходах, периОдические сигналы. После появления на входе ФУС 14 сигнала блокиров ки ключи 10 и 11 размыкаются, разрывая тем самым цепь кольца фазовой автоподстройки. Сигналы на входы фазового корректора 7 не поступают и напряжение, запомненное интегратором 8, поддерживает частоту управляе мого генератора 1 соответствующей частоте синхронизма, достигнутого системой автоподстройки до момента ее отключения.

После размыкания ключей 10 и 11 размыкается третий ключ 12 и отключает напряжение питания с ДПКД 2, делителя частоты 5, частотно-фазового детектора 3 и формирователя импульсов б. Потребление энергии питания синтезатором в этом состоянии сокращается. (Через определенный момент времени на первом выходе ФУС 14 появляется сигнал, под действием которого третий ключ 12 замыкается и напряжение питания вновь подается на цифровые узлы синтезатора. Одновременно с этим со второго выхода ФУС 14 подается сигнал на установку в исходное состояние ДПКД 2, частотно-@a3oaoro детектора 3, делителя частоты 5 и . формирователя импульсов б. По истечении некоторого времени, достаточного для завершения переходных процессов, связанных с включением питания и установки цифровых элементов в исходное состояние, появляется сигнал на третьем выходе ФУС 14 и первый и второй ключи 10 и 11 замыкаются. После этого сигнал установки в исходное состояние на втором выходе ФУС 14 исчезает и ДПКД 2 и делитель частоты 5 одновременно на30 чинают полный цикл счета. Так как частота управляемого генератора 1 с помощью интегратора 8 поддерживалась равной частоте с)о, а фазы импульсов ДПКД 2 и делителя частоты 5

35 за счет одновременности начала цикла счета делителей совмещены, то при подключении кольца фазовой автоподстройки синхронизм в системе не нарушается. Затем через некоторое время

40 работы системы автоподстройки подаются сигналы на ключи 10, 11, 12, кольцо разрывается и напряжение питания снимается с цифровых устройств синтезатора.

45 Минимальное время работы кольца автоподстройки ограничено длительностью периода импульсов частоты сравнения на входе частотно-фазового детектора 3, так как для нормальной работы необходим хотя бы один полный цикл счета ДПКД 2 и делителя частоты 5 после каждого подключения кольца автоподстройки частоты. Один из вариантов выполнения ФУС 14 приведен на фиг. 2. При появлении на выходе датчика синхронизма положительного потенциала на прямом выходе D-триггера 16 устанавливается сигнал с уровнем логической единицы, который поступает на входы первого и второго элементов ИЛИ 19 и 21 совместно с сигналом, приходящим с инверсного выхода D-триггера 16 на вход элемен1 та И 23, и блокирует работу ФУС 14.

При отсутствии на выходе датчика

65 синхронизма 13 положительного потен1007202

Составитель Ю. Ковалев

Редактор В. Лазаренко Техред A.Áàáêíåö Корректор А. Дзятко

Заказ 2154/77 . Тираж 934 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 циала с приходом на тактовый вход

0-триггера 16 сигнала с выхода мультивибратора 15 происходит разблокировка ФУС 14.и он начинает формировать управляющие, сигналы с периодом, определяемым мультивибратором 15.