Управляемый делитель частоты следования импульсов

Иллюстрации

Показать всеРеферат

УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ, содержащий делитель частоты, N -разрадный счетный блок, вьгходы которого соединены с соответствующими входами N -разрядного блока сравнения, выходы ( N -1) разрядов которого со&|динены с первыми входами соответствуюпдах ( N -1). триггеров, которых соединены с первыми Тзходамза соответствующих элементов И, отличающийся тем, что, с цепью повышения точности, в него введен формирователь импульсов, вход которого соединен с выходом последнего разряда N -li разрядного блока сравнения, а выход - с вторыми входами ( N -1) трш геров и установочными входа1«(И N -раэ Р5здного счетного блока, при этом вход делителя соединен со счетипым входом первого разряда N - разрядно-1 1Х)счетного блока, счетные входы ооггальных разрядов которого соедицены с вь содами соотвег ггвуюпщх элемеотов И вторые входы которых соединены с соответствуюпшмн выходами делителя частоты. 2. Депхггель по п. 1, отличающий с я тем, что каждый разряд разрядного блока сравнення содержит демультиплексор, первая rpyntib входов которого является входами да1 кого разряда, вторая группа входов соединена с вЫхода ф переклю теля, а-выход является выходом данного раэ р5ща N -ра:фядного блока сравнения.. 00 со

1 100

Изобретение относится к устройствам импульсной и цифровой. техники и может быть использовано в цифровых измерительных приборах и программных задающих устройствах для получения интервалов времени.

Известен управляемый делитель частоты следования импульсов, содержащий счетчик импульсов, элементы И и управляющий триггер Pl)

Недостаток данного устройства — не- высокая точность деления.

Наиболее близким к предлагаемому является управляемый делитель частоты следования импульсов, содержащий блоки сравнения, управляющие входы каждого из которых соединены с.выходами декад делителя частотыри счетчи, ки, триггеры и элементы И, элемент ИЛИ входы которого подключены к выходам элементов И, управляющий вход каждого из которых соединен с выходом соответствующего блока сравнения, информационный вход первого элемента И соединен с входом первого делителя частоты, а информационные входы других элементов И - с единичными выходами триггеров, тактирующие вхоJ ды которых подключены к входам соответствующих декад делителя частоты, а установочные входы объединены и подключены к входу первой декады делителя частоты t2)

Недостатком известного устройства является низкая точность из-за неравномерности следования импульсов в выходной последовательности.

Цель изобретения - повышение точности деления.

Поставленная цель достигается тем, что в управляемый делитель частоты следования импульсов, содержащий делитель частоты, N -разрядный очи ный блок, выходы которого соединены с соответствующими входами -разрядного блока сравнения, выходы (N»l) разрядов которого соединены с первыми входами соответствуюших (N -1) триггеров, выходы которых соединены с первыми входами соответствующих элементов И, введен формирователь импульсов, вход которого соединен с выходом последнего разряда N -разрядного блська сравнения, а выход - с вторыми входами (Й -1) триггеров и установоч;ными входами Й -разрядного счетного блока, при этом вход делителя частоты соединен со счетным входом первого

89ii

so

9 го г5 зо

4О

55 разряда N -разрядного счетного блока, счетные входы остальных разрядов кс торого соединены с выходами соответствующих элементов И, вторые входы которого соединены с соответствующими вы.ходами делителя частоты.

При этом каждый разряд N -разрядного блока сравнения содержит демультиплексор, первая группа входов которого является входами данного разряда, вторая группа входов соеди-. нена с выходами переключателя, а выход является выходом данного разряда hl -разрядного блока сравнения.

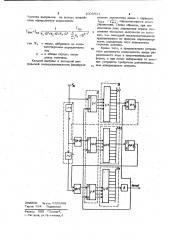

На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит делитель 1 частоты, вкпючаюший в себя декады (1-1) - 1 -(N-l), N -разрядный счетный блок 2, включающий в себя счетчики (2-1) - (2- N),,N -разрядный блок 3 сравнения, включающий в себя демультиплексоры (4»1) — (4- Й ) и переключатели (5-1) - (5 - Al ), триггеры (6-1 - 6-(Ц -1), элементы И 7 -(g 2) 7 (g 1) и формирователь 8 импульсов.

Устройство работает следующим образом. йелитель 1 обеспечивает на выходах декад частоты "" И ", очи о

Аналогично вышеописанному после поступления в счетчик 2-(N -1) числа импульсов, равного набранному на пере ключателе 5 - (-1), в единичное состояние устанавливается триггер 6(Я -1). Процесс продолжается до появления выходного сигнала на последнем разряд.е блока 3, поступающего на формирователь 8. Последний формирует короткий выходной импульс, который устанавливает счетчики блока 2 и триггеры (6-1) - 6 (Я -1) в нулевое состояние. На этом цикл работы устройства заканчивается. Йалее вышеописан: Яае процессы циклически повторяются, 3 10089

Частота импульсов на выходе устройства определяется выражением ВХ

" " Sx N, а +Ы 10 И 0

7 5 з и„ а

<-1 где N - число, набранное на соответствующем переключателе;

- в общем случае. число декад счетчика.

Каждый импульс в выходной импульсной последовательности фиксирует

ВНИИПИ За каз 2359/6

Тираж 934 Подписное

Филиал ППП "Патент, г. Ужгор од, ул. Нр кт ная, 4

1 !

t

I

t момент завершения цикла с периодом

Т и в„„определяющимся кодо управления. Таким образом, п1Ж неизменном коде управления период сле-дования выходных импульсов не изменен, т.е. выходной последовательности пр1щцнпиально не присуща неравномерность вследствие чего повышается точность деления.

Кроме того, в предлагаемом устройстве достигнута возможность ввода управляющего кода в число-импульсной форме, а при вводе информации от внеш.них устройств требуются дополнительные аппаратурные затраты.