Компаратор

Иллюстрации

Показать всеРеферат

1. КОМПАРАТОР, содержащий счетчик, генератор импульсов и блок анализа, причем выход генератора импульсов соединен со счетным входом счетчика, а выходы блока анализа являются выходами компаратора, отличающийся тем, что, с целью упрощения и повышения достоверности результата, содержит первый, второй и третий блоки сравнения, выходы которых соединены с соответствующими входами блока анализа, первые группы входов блока сравнения соединены с группами соответствующих информационных входов компаратора, вход последовательного ввода числа компаратора соединен со счетным входом счетчика, инверсные выходы разрядов которого соединены с вторыми группами -входов блоков сравнения. 9

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

3 G 06 F 7 04 с

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К AB TOPCHOMY CBNQETEJlbCTB Y

° °

° В

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР пО делАм изоБРетений и ОтнРытий (21) 3339619/18-24 (22) 29.09.81 (46) 07.04.83. Вюл. Р 13 (72) В.И.Глушков, В.А.Гаврилов, В.Н.Бойко и В.В.федоренко (53) 681.325.66(088.8) (56) 1. Авторское свидетельство СССР

9 34103?, кл. G 06 F 7/02, 1970.

2. Авторское свидетельство СССР

Р 468237, кл. G 06 F 7/02, 1974.

3., Авторское свидетельство СССР

Р 375641, кл. G 06 F 7/04, 1971 (прототип). (54)(57) 1. КОМПАРАТОР, содержащий счетчик, генератор импульсов и блок анализа, причем выход генератора им„„Я0„„ 1010614 А пульсов соединен со счетным входом счетчика, а выходы блока анализа являются выходами компаратора, о т ли чающий ся тем, что, сцелью упрощения и повышения достоверности результата, содержит первый, второй и третий блоки сравнения, выходы которых соеди иены с со ответ ст вующими входами блока анализ а, первые группы входов блока сравнения соединены с группами соответствующих информационных входов компаратора, вход последовательного ввода числа компаратора соединен со счетным входом счетчика, инверсные выходы разрядов которого соединены с вторыми группами входов блоков сравнения. 8

1010б14

2. Компаратор по п. 1, о т л и ч аю щ и и сятем,,что блок сравнения содержит резистор смещения напряжения высокого уровня, vl коммутирующих диодов, и реле с нормально разомкнутыми контактами, причем отрицательная шина источника питания соединена с первыми клеммами обмоток реле, вторые клеммы которых соединены с первой группой входов блока, вторая группа входов блока соединена через контакты реле с катодами соответствующих коммутиру— ющих диодов, аноды которых соединены между собой и являются выходом блока, между отрицательной шиной источника питания и выходом блока включен резистор смещения напряжения высокого уровня.

3. Компаратор по п. 1, о т л и ч а— ю шийся тем, что блок анализа содержит первый, второй и третий триггеры, первый, второй и третий элементы И, элемент ИЛИ, причем входы установки триггеров в единичное состояние

Изобретение относится к автомати— ке и вычислительной технике и может быть использовано в автоматизирован— ных системах контроля и управления при осуществлении допускового контро- 5 ля величин, представленных во всех разновидностях взвешенных двоичных кодов (двоичный, двоично-десятичный и т.д.).

Известно устройство для сравнения чисел, содержащее генератор, триггер, О последовательно соединенных поразрядных узлов сравнения, каждый из которых состоит из элементов И, ИЛИ-НЕ, элемент НЕ, элементы индикации Е 13.

Недостатками этого устройства являются его малые фун кциональные воз можности, так как сравнение производится только с одним числом. Чтобы опреде — 2О лить, находится ли сравниваемое число в з аданных пределах, необходимо использовать два этих устройства.

Известно устройство, обеспечивающее допусковый контроль чи сел, содержащее yq блок сравнения, входы которого соединены с выходами реверсивного счетчика и регистра, формирователь поля допуска, вход которого соединен с выходом

"Равно" сравнивающего блока, а выход через элемент ИЛИ вЂ” с входом реверсивного счетчика, входы управления которого через элементы ИЛИ соединены с выходами "Больше" и "Меньше" блока сравнения.

Недостатком этого устройства является его сложность. соедине ны с сооТ вет ст вующими входами блока, единичный выход первого триггера соединен с первым входом первого элемента И, выход которого является первым выходом блока, нулевой выход первого триггера соединен с первыми входами второго и третьего элементов И, единичный выход второго триггера соединен с вторыми входами элементов И, единичный выход третьего триггера соединен с третьими входами первого и второго элементов И, нуле— вой выход третьего триггера соединен с третьим входом третьего элемента И, выход которого является вторым выходом блока и соединен с входом установки третьего триггера в нулевое состояние и первым входом элемента ИЛИ, выход второго элемента И является третьим выходом блока и соединен с вторым входом элемента ИЛИ, выход которого соединен с входом установки первого триггера в нулевое состояние.

Наиболее близким к предлагаемому является компаратор для сравнения двоично †десятичн чисел, позволяющий производить ввод измеряемой величины как в последовательном, так и в па— раллельном коде, который содержит два двоично †десятичн счетчика, состоящих из n декад каждый, пороговый элемент, 4 vl формирователей импульсов, выполненных в виде ждущих многофазных мультивибраторов, 4 1 элементов И и генератор тактовых импульсов j Çj.

Недостатками известного компаратора являются era сложность и низкая достоверность результата сравнения, связанная с тем, что при поступлении числа, большего, чем верхний допуск, возможно срабатывание порогового устройства только при переполнении счетчика нижнего допуска до переполнения счетчика верхнего допуска. При этом будет сформирован ложный выходной си гн ал НОРМА.

Кроме того, известное устройство предусматривает работу только с числами, представленными в двоично-десятичном коде. Для работы с другими кодами необходимо перестраивать блоксхему устройства (изменяются связи между формирователями импульсов и счетчиками, а также схемы формирова— телей>.

Цель изобретения — упрощение уст— ройства и повышение достоверности ре— зультата сравнения (за счет устранения возможности ложных ср абатыв ан ий) .

1010614

65

Поставленная цель достигаетcR тем, что компаратор, содержащий счетчик, генератор импульсов и блок анализа, причем выход генератора импульсов соединен со счетным входом счетчика, а выходы блока ан али з а являют ся выходами компаратора, содержит первый, второй и третий блоки сравнения, вы— ходы которых соединены с соот вет ствующими входами блока анализ а, первые группы входов блоков сравнения соеди- 0 нены с группами соответствующих информационных входов компаратора, вход последовательного ввода числа компаратора соединен со счетным входом счетчика, инверсные выходы разрядов 15 которого соединены с вторыми группами входов блоков сравнения.

Блок сравнения содержит резистор смещения напряжения высоко о уровня, коммутирующих диодов,и реле с нормально разомкнутыми контактами, причем отрицательная шина источника питания соединена с первыми клеммами обмоток реле, вторые клеммы которых соединены с первой группой входов блока, вторая группа входов блока соединена через контакты реле с катодами соответствующих коммутирующих диодов, аноды которых соединены между собой и являются выходом блока, между отрицательной шиной источника питания и выходом блока включен резистор смещения напряжения высокого уровня.

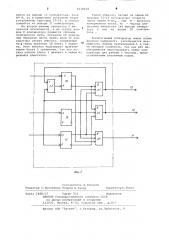

Блок анализа содержит первый, второй и третий триггеры, первый, второй

35 и третий элементы И, элемент ИЛИ, причем входы установки триггеров в единичное состояние соединены с соответствующими входами блока, единичный выход первого триггера соединен с 40 первым входом первого элемента И, вы- . ход которого является первым выходом блока, нулевой выход первого триггера соединен с первыми входами второго и третьего элементов И, единичный вы-45 ход второго триггера соединен с вторыми входами элементов И, единичный выход третьего триггера соединен с третьими входами первого и второго элементов И, нулевой выход третьего триггера, соединен с третьим входом третьего элемента И, выход которого является вторым выходом блока и соединен с входом установки третьего триггера в нулевое состояние и первым входом элемента ИЛИ, выход второго

55 .элемента И является третьим выходом блока и соединен с вторым входом элемента ИЛИ, выход которого соединен с входом установки первого триггера в нулевое сост ояние .

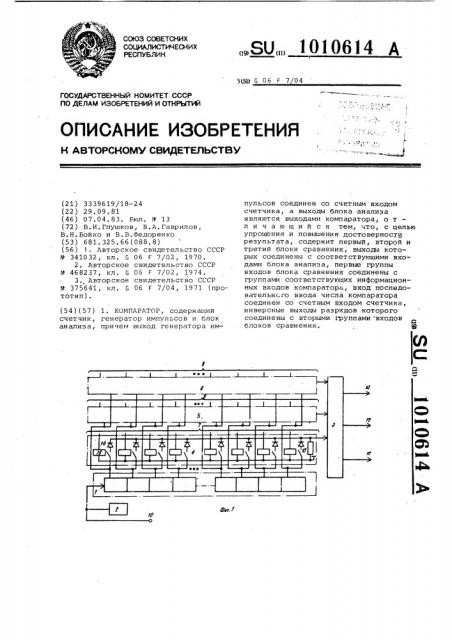

На фиг. 1 представлена блок-схема компаратора; на фиг. 2 — блок-схема блока анализа.

Компаратор содержит -разрядный счетчик 1, генератор 2 импульсов, 5, 4, 6

4, 5, б

И< Н

Н< И< В

В< И 5, б, 4

Если И < Н, то сигнал от блока 5 сравнения поступит на второй вход блока анализа и установит триггер 18 в единичное состояние, Сигнал с единичного выхода этого триггера поступит на элемент ИЛИ 22, и через него— на выход 12 компаратора, сигнализируя, что измеряемое число меньше,чем нижний допуск. Одновременно этот сигнал поступит на нулевые входы триггеров 17 и 19, блокируя их установку в единичное состояние. Если Нс И < В, то в единичное состояние будут установлены триггеры 17 и 18, а сигнал пояблок 3 анализа, первый, второй и третий блоки 4-6 сравнения, первую, вторую и третью группу информационных входов 7-9 компаратора, информационный вход 10 комп аратора, первый, второй и третий выходы 11-13 компаратора. Блок сравнения содержит группу диодов 14, резистор 15, группу реле 16.

Блок анализ а содержит первый, вто. рой и третий триггеры 17-19, первый, второй и третий элементы И 20-22, элем нт ИЛИ 23.

Компаратор работает следующим образомм.

В начальный момент счетчик 1 и триггеры 17-19 устанавливаются в нулевое состояние. Ha группы входов 7 и

9 поступают параллельным кодом значения верхнего и нижнего допусков соответственно. Измеряемое число может быть введено параллельным или числоимпульсным кодом. В первом случае оно подается по группе входов 8, а во втором — через вход 10 устройства.

Рассмотрим первый режим.

Импульсы от генератора 2 непрерывно увеличивают находящееся в счетчике

1 число. В момент, когда находящееся в счетчике 1 число станет равным чис лу, поступающему на какую-либо группу входов 7-9, в соответствующем блоке

4-6 сравнения сработаю те реле 16, на которые подан сигнал логической единицы. Это приведет к тому, что все диоды 14 окажутся запертыми, и на выходе этого блока сравнения появится низкий потенциал, соответствующий си гн алу ло гиче ской еди ницы.

В з ави симо ст и от соот ношения нижнего допуска"Н", верхнего допуска "В" и измеряемого числа "И" блоки 4-6 сравнения будут срабатывать в следующей последовательности:

Соотношение Последовательчисел ност-ь срабатывания

10 10614

Составитель H.Ãîðîõîâ

Редактор С.Крупенина Техред М.Тепер

Корре ктор. Е . Рошк о

Заказ 2488/37 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", г.ужгород, ул.Проектная, 4 вится на выходе 13 компаратора. Если

И> В, то в единичное состояние будут уст ановле ны триггеры 17-19, и сиги ал появится на выходе 11 компаратора.

Ва втором режиме генератор 2 им—

5 пульсов отключается, а на группу входов 8 компаратора подаются сигналы логического нуля. Сигналом об окончании передачи числа через вход 10 ком— паратора служит импульс, подаваемый на g -вход триггера 18 блока 3 анализа. Этот импульс модулирует срабатывание блока 5 сравнения, так что логика работы блока 3 анализа в любом из режимов идентична.

Таким образом, сигнал на одном из выходов 11 — 1 3 комп ар ат ор а поя вит ся через время Т=г Ьл, где ю — величина измеряемого числа, +и — ериод следо вани я импульсов на выходе генератора 2 или на входе 10 компаратора

Предлагаемый компаратор. имеет более высокую надежность (исключается возможность ложных срабатываний ), а также меньшую сложность, так как нет необходимости перестраивать схему компаратора для работы с числами, представлен ными различным кодом.