Квадратор

Иллюстрации

Показать всеРеферат

КВАДРАТОР, содержащий первый счетчик, 2п-разрядный накопитель и группу элементов И, от ли ч d ющ и и с я тем, ч-Ьо, с целью повышения быстродействия, в него введены второй счетчик, две схемы сравнения, вторая и третья группы элементов И, триггер, элемент 2И-ИЛИ, элемент ИЛИ и йять элементов И, выходы эле«яентов И первой, второй и третьей групп соединены соответственно с (п-ь1)...(п+2), с п...(+2) и с (). ..2 входами накопителя, ()-й вход накопителя соединен с выходом элемента 2И-ИЛИ, быходы первого счетчика соединены с информационными входами элементов И первой группы и с первой группой входов первой схемы сравнения, вторая группа входов которой соединена: с йД входами старших разрядов кода аргумента квадратора, выход первой схемы сравнения соединен с первыми входами первого второго и третьего элементов И, тактовый вхол накопителя , первый вход четвертого элемента И соединены с тактовым входом квадратора, третий вход.третьего элемента И соединен с первым входом пятого элемента И, с вторым входом четвертого элемента И и с выходом второй cxehojсравнения, первая группа входов которой соединена с hji входами младших разрядов кода аргумента квадратора, а вторая группа входов соединена с информационньшк входами элементов И второй и третьей групп и с выходами йторого счетчика, стробирукяцйе входы элементов И первой группы соединены с выходом второго элемента И и с первым и вторым входами элемента 2И-ИЛИ, третий,вход которого соединен с выходом Старшего разряда второго счетчика, а четвертый вход элемента 2И-ИЛИ подключен к прямому выходу триггера и к стробирующему входу элементов И второй группы, инверсный выкод триггера подключен к вторым входам второго и пятого элементов И, выход пятого элемента -И соединен со стробируюцими входами элементов И третьей группы , и с первым входом накопителя, счет ные входы первого и второго счетчиков соединены соответственно с выходами первого и четвертого элемеЯ ; О тов И, выход третьего элемента И подключен к счетному входу триггера ф ft к первому входу элемента ИЛИ, . второй вход которого, входы установки триггера и.второго с4втчя ка соединены с установочным входом квадратора, установочный бход первого счетчика соединен с выхо1;ом элемента ИЛИ.

СОКИ СОВЕТСНИХ

РЕСПУБЛИК

3<50 6 06 f 7>

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСНОМУ СВИДЕТЕЛЬСТВУ (21) 3356172/18-24

„ 22) 11,11 81 (46) 07.04.83. Бюл..Р 13 (72) Е.Ф.Киселев и Л.A.Êîæèðíîâà (53) 681.325(088.8) ,(56) 1.Авторское свидетельство СССР

9 780005, кл. С 06 F 7/38, 1980.

2 ° Авторское свидетельство СССР

В 475619, кл. 6 06 Р 7/38, 1975 (прототип) . (54) (57) КВАДРАТОР, содержащий первый счетчик, 2п-разрядный накопитель и группу элементов И, о т л и ч а юшийся тем, что, c целью повышения быстродействия, в него введены второй счетчик, две схемы сравнения, вторая и третья группы элементов И, . триггер, элемент 2И-ИЛИ, элемент

ИЛИ и йять элементов И, выходы элементов И первой, второй и третьей групп соединены соответственно с (п+1) .. (и+2), с n... (ф +2) и с (л +1)...2 входами накопителя, (й+1)-й вход накопителя соединен с выходом элемента 2И-ИЛИ, Выходы первого счетчика соединены с информационными входами элементов И первой группы и с первой группой входов первой схемы сравнения, вторая группа входов которой соединена с йф входами старших разрядов кода аргумента квадратора, выход первой схемы сравнения соедйнен с первыми входами первого, второго и третьего .элементов И, тактовый вход накопителя, первый вход четвертого элемента И соединены с тактовым входом

„„SU„„1010620 А квадратора, третий вход третьего элемента И соединен с первым входом пятого элемента И, с вторым входом четвертого элемента И и с выходом второй схема сравнения, первая группа входов которой соединена с й/2. входами младших разрядов кода аргумента квадратора, а вторая группа входов соединена с инФормационньвщ входами элементов И второй и третьей групп и с выходами второго счетчика, стробирующие.входы элементов И nepsoN группы соединены с выходом вторрго элемента И и с первым и вторым входами элемента: 2И-ИЛИ, третий .вход которого соединен с находом старше« го разряда второго счетчика, а чет- 3 вертый вход элемента 2И-ИЛИ подклю« чен к прямому выходу триггера и к стробиру ацему входу элементов И второй группы, инверсный выход триггера подключен к вторым входам второго и пятого элементов И, .выход пятого элемента И соединен со стробируищими входами элементов И третьей группы и с первым входом накопителя, счет- ные входы первого и второго счетчи ков соединены соответственно с выходами первого и четвертого элемент», тов И, выход третьего элемента И подключен к. счетному входу триггера и к первому входу элемента ИЛИ, второй вход которого,- входи установки триггера и .второго с4етчика соединенй с устаиовочным входом квадратора, установочный Вход первого счетчика соединен с выходом .элемента ИЛИ.

1010620

Изобретение относится к цифровой вычислительной технике и предназначено для воспроизведения по коду аргумента х функции (1) 5 у - х

2 у, =x =х + 2V. +1

1 1 14 1-1

x=х+!

1 1-л

) где i — номер итерации, принимающий значения О, 1, 2,...n-1.

Быстродействие алгоритма (2) определяется выражением (2)

Т =X-t 2 t =Т 3 и прот ) и проТ,и)ах(, где t период частоты следования импульсов приращения аргумента х„.

Недостатком известного квадратора является низкое быстродействие, обусловленное недостаточно полным использованием функциональных возможностей накопителя.

Цель изобретения — повышение 40 быстродействия квадратора.

Поставленная цель достигается тем, что в квадратор, содержащий первый счетчик, 2п-разрядный накопитель и группу элементов И, допол- 45 нительно введены второй счетчик, две схемы сравнения, вторая и третья группы элементов И, триггер, элемент 2И-ИЛИ, элемент ИЛИ и пять элементов И, выходы элементов И 50 первой, второй и третьей групп соединены соответственно с (— п+1)... (и+2)) с n...(+2) и с (»- +1)...2 входами накопителя, (и+1)-й вход накопителя соединен с выходом элемента 2И-ИЛИ, выходы первого счетчи55 ка "îåäèíåíû с информационными входами элементов И первой группы и с первой группой входов первой схемы сравнения, вторая группа входов ко тсрой соединена с и 2. входами старших разрядов кода аргумента квадратора, выход первой схемы сравнения соединен с первыми входами первого, второго и третьего элементов И, тактовый вход накопителя, первый вход 65

Для воспроизведения функции (1) наиболее простыми являются устройства, работа которых связана с числоимпульсной обработкой информации.

Известно устройство для .возведения в квадрат 1 1 )..

Однако данное устройство отличается сложностью и невысоким быстро- действ ием. 15

Наиболее близким по технической сущности к предлагаемому является квадратор Р 2 3) содержащий счетчик,элемент задержки, ключи, накопитель и реализует функцию (1) на основе 20 итерационного алгоритма

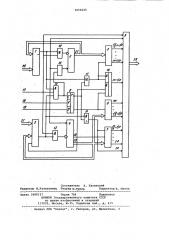

На чертеже приведена структурная схема предлагаемого квадратора.

Квадратор содержит схемы 1 и 2 сравнения, счетчики 3 и 4, группы элементов И 5-7, накопитель 8, триггер 9, элементы И 10-14, элемент

ИЛИ 15, элемент 2И-ИЛИ 16, тактовый вход 17, вход 18 установки, вход 19 . логической единицы, входы 20 и 21 соответственно старших и младших разрядов кода аргумента квадратора, разрядные выходы 22 счетчика 3 и 23 младших разрядов счетчика 4, выход

24 старшего разряда счетчика 4 и выход 25 накопителя 8. .Предлагаемый квадратор реализует функцию (1) при х,.представленном в виде л л и)Х л х =x 2 +x4 с) (4) ° л разрядность кода х; разрядные коды, полученные соответственно из старших и младших разрядов п-разрядного кода

x = Д 2" a„. {a„.а 10,1)- разрядная цифра i-ro разряда кода x) .. где пл, . л и х и .x- ——

1 2. четвертого элемента И соединены с тактовым входом квадратора, третий вход третьего элемента И соединен. с первым входом пятого элемента И, с вторым входом четвертого элемента

И и .с выходом второй схемы сравнения, первая группа входов которой соединена с и(2 входами младших разрядов кода аргумента квадратора, а вторая группа входов соединена с информационными входами элементов И второй и третьей групп и с выходами второго счетчика, стробирующие входы элементов И первой группы соединены с выходом второго элемента И и с первым и вторым входами элемента 2И-ИЛИ, третий вход которого соединен с выходом старшего разряда второго счетчика, а четвертый вход элемента 2ИИЛИ подключен к прямому выходу триггера и к стробирующему входу элемен" та И второй группы, инверсный выход триггера подключен к вторым входам второго и пятого элементов И, выход пятого элемента И соединен со стробирующими Входами элементов И третьей группы и с первым входом накопителя, счетные входы первого и второго счетчиков соединены соответственно с выходами первого и четвертого элемен-. тов И, выход третьего элемента И подключен к счетному входу триггера и к первому входу элемента ИЛИ, второй вход которого, входы установки триггера и второго счетчика соединены с установочным входом квадратора, установочный вход первого счетчика соединен с выходом элемента ИЛИ, 1010620

При условии (5) функция (1 j при» нимает вид .

ЛД Ь И Л Л Л у =.х =х„° .2" + х + хх - 2 .(5)

Работает квадратор циклически, В течение каждого цикла можно выделить два периода Т1 и Т2 работы квадраторапо формуле (5). В течение Т1.происходит вычисление суммы квадратов

2 " + х, à в течение Т2 вычисля1 Я 1 л л ир+ ется произведение х х . 2

Перед началом каждого цикла вычислений на разрядные входы 20 и 21 квадратора соответственно подаются . коды ф 20 = и ф 20 =, период . 15

Т1 начинается с поступленйя на вход

18 импульса установки, по которому. триггер 9, счетчик 4, накопитель 8, счетчик 3 через элемент HJIH 15 устанавливаются в ноль. После окончания 20 импульса, установки на вход 17 начинают поступать тактовые импульсы, которые при нулевых выходных сигналах со схем 1 и 2 сравнения. через элементы

И 10 и 13 поступают на счетные входы 25 счетчиков 3 и 4 соответственно. При этом на разрядных выходах 22 счетчика л

З„формируется код х„.„., поступающий на информационные входы группы элементов

И 5 и на первую группу входов схемы

1 сравнения, а на выходах 24 и 23 счетчика 4 формируются соответственно. код старшего разряда ф 24 и код младл ших разрядов ф ЕЗ кода 1 ;. Код х« поступает на информационные входы группы элементов И 7 и первую группу. входов схемы 2 сравнения, Кроме того, коды ф 24 и ф 23 поступают соответственно на вход элемента 2И-ИЛИ

16 и на информационные входы группы элементов И 6. Схема 1(2) сравнения 40 вырабатывает сигналы "единица" при

Ф 2 (12., ) = ф 20 fy 21) и "ноль" при ф22 (Q;) фф20 (ф21) .

В начале вычислений триггер 9 находится в нулевом состоянии, поэтому 45 элементами 11 и 14 И разрешено. прохождение выходных кодов счетчика

3 и 4 через группы элементов И 5 и 7 и соответственно на входы с (— n+1} по (n+2) и с (†" +1} по два накопителя 8, а также прохождение единичных сигналов через элемент 2И-ИЛИ 16 на вход (n+l)-го разряда, а через элемент И 14 — на вход младщего разряда накопителя 8.

При этом одновременно реализуется алгоритм (2) для функций л з. л у„= х„и у = х .

Период Т1 заканчивается, когда произойдет сравнение на обоих схемах сравнения и вырабатываются сигналы, равные "1", по которым элемент И 12 формирует импульс, устанавливающий триггер 9 в "1", а счетчик 3 через элемент ИЛИ 15 — в "0".

Таким обравом, за время

Т1 и 2 (6} на кодовых выходах 25 накопителя 8 формируется код ф25. = х,, ° 2 + х .

AQ, и h2

Состояние "1" триггер 9 разрешает работу квадратора в периоде Т2, т.е. запрещает работу элементов И 11 и 14, групп элементов И 5 и 7 и через элемент 2И-ИЛИ 16 группы элементов И 6 подключает на соответствующие входы л накопителя 8 код х 2 " ""

Таким образом формируется произведение х . Й,„. 2 до тех пор, ь.. и пока выход схемы 1 сравнения не станет равным "1".

Процесс вычисления заканчивается при единичном состоянии выходов схем

1 и 2 сравнения и триггера 9, при этом прекращается подача тактовых импульсов на вход 17 квадратора, а с выходов 25 накопителя 8 можно снимать код функции (1) до прихода следующего импульса установки.

Длительность периода Т2 определяется так

Т2 2 tè. (7)

ИФ

Из сказанного выше следует, что общее время вычисления функции (1) определяется выражением

И 1+1

Т = Т1+ Т2 2 .1„= Т . (S)

Сравнивая выражения (3) и (8) получим (9) и а

Так, при n = 8

, ю. з

1оХ

Таким образом, быстродействие предлагаемого квадратора (см. оценку (9) выше быстродействия известного.

1010б20

Составитель A. Каэанский

Редактор M.Ðà÷êóëèíåö Техред M. Teriep Корректор И, йулла

Закаэ 2488/37 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раутаская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул, Проектная, 4