Устройство для задания тестов

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

3 5р G 06 P 11/26

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABT0PGHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3355520/18-24 (22) 20.11.81 (.46) 07.04.83. Бюл. В 13 (72) Л.Э. Друзь и Ю.П. Рукоданов (53) 681.3(088.8) (56) 1; Авторское свидетельство СССР

В 694863, кл. G 06 F 11/04, 1976.

2. Авторское свидетельство СССР

9 826357, кл. G 06 F 11/20, 1979. (54)(57) 1, УСТРОЙСТВО ДЛЯ ЗАДАНИЯ

ТЕСТОВ> содержащее генератор импульсов, счетчик, первый элемент И, элемент задержки, регистр.и задатчик тестов, причем выход генератора импульсов соединен с первым входом первого элемента И, выход которого соединен с входом элемента задержки и с входом обнуления счетчика, о т— л и ч а ю щ е е с я тем; что, с целью расширения функциональных возможностей устройства путем обеспечения различных тестовых последовательностей, в него введены блок приоритета, блок задержки включения, группа элементов И, шифратор, блок памяти, триггер, второй элемент И, элемент ЙЛИ, причем выходы задатчика тестов соединены с единичными входами соответствующих разрядов регистра, единичные выходы которого соединены с входами блока приоритета, выходы блока приоритета через блок задержки включения соединены с первыми входами соответствующих элементов И группы и с соответствующими входами шифратора, выходы которого соединены с установочными входами счетчика, информационные вы ходы счетчика соединены с адресными входами блока памяти и с входами элемента ИЛИ, выход которого . соединен с входом. разрешения генеÄÄSUÄÄ 101 0632 A ратора импульсов, выход генератора импульсов соединен с первым входом второго элемента И, выход которого соединен с входом чтения блока памяти, первый и второй управляющие выходы блока памяти соединены соответственно со счетным входом счетчика и с единичным входом триггера,, группа информационных выходов блока памяти является группой информационных выходов устройства, выхоц элемента задержки соединен с нулевым входом триггера, нулевой и единичный выходы которого соединены соответственно с вторыми входами второго и первого элементов-. И, выход первого элемента И соединен с вто- . Q рыми входами элементов И группы, выходы которых соединены d нулевыми входами соответствующих разрядов регистра.

2. Устройство по и. 1, о .т л sч а ю щ е е с я тем, что блок при- Я оритета содержит группу элементов И, группу .элементов ИЛИ и группу элемен- тов НЕ, причем группа входов блока )(ф приоритета, кроме первого, соединена с первыми входами соответствующих элементов И и ИЛИ группы, выход каждого предыдущего элемента ИЛИ группы соединен с вторым входом каждого последующего элемента ИЛИ группы и через соответствующий элемент НЕ группы с вторым входом соответст- вуннцего элемента И группы, выходы элементов И группы являются груп- пой выходов устройства, первый вход группы входов блока является первым выходом группы выходов блока и соединен с вторым входом первого элемента ИЛИ группы и черед первый элемент НЕ группы с вторым входом первого элемента И группы;

1010632

Изобретение относится к автомати- ке и вычислительной технике и может быть использовано для контроля дискретных устройств, работающих с информацией, представленной в виде кодовых комбинаций. 5

Известно устройство для тестового контроля, содержащее запоминаю.щий блок хранения тестов, блок записи информации, регистр, коммутатор блок управления и блок сравнения f1 3. 10

Недостаток данного устройства зак;лючается в невозможности формирования различных последовательностей тестов и обусловлен постоянным заданием одного тестового набора в блоке памяти и в постоянной неизменяемой связи блока управления и коммутатора, соединяющего контролируемые цепи с тестовым регистром, что ограничивает возмож- 20 ность использования устройства для проверки различных типов объектов.

Наиболее близким к предлагаемому является устройство для контроля ло гических блоков, содержащее генера- 25 тор импульсов, регистр, счетчик, блок сравнения элементы И и задатчик тестов 2 ).

Недостатком данного устройства является. то, что оно не позволяет gp изменять последовательность комбинаций в тесте и использовать эти комбинации в различных сочетаниях, т.е. не обеспечивает формирование последовательности различных тес- 35 товых наборов. Такие различные последовательности тестов и их комбинации необходимы при поиске неисправностей, когда их локализация проводится по все более сужающейся области и каждая проверка по данному тесту ограничивает область, в которой проводится следующая проверка. . Таким образом, недостаток известного устройства заключается В ограниченности его функциональных возможнос» 45 для локализации неисправностей в про веряемом объекте. цель изобретения — расширение функциональных воэможностей устройст- 5р ва путем формирования различных тестовых последовательностей.

Поставленная цель достигается тем, что в устройство для задания тестов, содержащее генеРатоР импульсов, счетчик, первый элемент И, элемент задержки, регистр и задатчик тестов, причем выход генератора импульсов соединен с первым входом первого элемента И,выход которого соединен с входом элемента задержки и с входом обнуления счетчика, введены блок приоритета, блок задержки включения, группа элементов И, шифратор, блок памяти, триггер, второй элемент И, элемент ИЛИ, при- 65 чем выходы задатчика тестов соединены с единичными входами соответствующих разрядов регистра, единичные выходы которого соединены с входами блока приоритета, выходы блока приоритета через блок задержки включения соединены с первыми входами соответствующих элементов И группы и соответствующими входами шифратора, выходы которого соединены с установочными входами счетчика, информационные выходы счетчика соединены с адресными входами блока памяти и с входами элемента ИЛИ, выход которого соединен с входом разрешения генератора импульсов, выход генератора импульсов соединен с первым входом второго элемента И, выход которого соединен с входом чтения блока памяти, первый и вторбй управляющие выходы блока памяти соединены соответственно со счетным входом счетчика и с единичным входом триггера, группа информационных выходов блока памяти является группой информационных выходов устройства, выход элемента задержки соединен с нулевым входом триггера, нулевой и единичный выходы которого соединены соответственно с вторыми входами второго и первого элементов И, выход первого элемента И соединен с вторыми входами элементов И группы, выходы которых соединены с нулевыми входами соответствующих разрядов,регистра.

Кроме того, поставленная .цель достигается, тем, что блок приоритета содержит группу элементов И, группу элементов ИЛИ и группу элементов

НЕ, причем группа входов блока приоритета, кроме первого, соединена с первыми входами соответствующих элементов И и ИЛИ группы, выход каждого предыдущего элемента ИЛИ группы соединен с вторым входом каждого последующего элемента ИЛИ группы и через соответствующий элемент НЕ группы с вторым входом соответствующего элемента И группы, выходы элементов И группы являются группой выходов устройства, первый вход группы входов блока является первым выходом группы выходов блока и соединен с вторым входом первого элемента ИЛИ группы и через первый элемент НЕ группы с вторым входом первого элемента И группы.

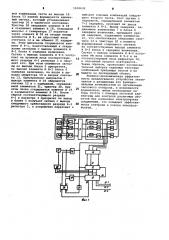

На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2 вЂ,схема блока приоритета.

Устройство содержит задатчик 1 тестов с клавишами 2-1, 2-2, 2-К, регистр 3 с разрядами 4-1, 4-2, 4-К, блок 5 приоритета, блок 6 задержки включения с элементами 7-1, 7-2, 7-К задержки и элементами H 8-1, 8-2,.8-К, группу элементов И 9-1, 1010632

Устройство работает следующим образом.

Б исходном положении триггер 20, счетчик 12 и регистр 3 обнулены. С

9-2, 9-К, шифратор 10 с выходами 11р счетчик 12, блок 13 памяти с выходами 14,15-1, 15-2, 15-К, 16, генератор 17 импульсов, первый элемент

И 18, второй элемент И 19, триггер

20, элемент 21 .задержки и элемент .5 ,ИЛИ 22.

Блок 5 приоритета содержит элементы И 23, ИЛИ 24, НЕ 25 и обеспечивает приоритетный опрос входных сигналов таким образом, что, например, 0 сигнал, действующий на предыдущем входе, блокирует на время своего действия все сигналы, действующие на. всех последующих входах1 т.е. приоритет на avxop HMeeT cHrHan на 15 предыдущем входе по отношению к сигналам на последующих входах. При этом блок всегда формирует выходной сигнал только на одном из выходов, соответствующем сигналу на входе большего приоритета. 20

Блок .13 памяти представляет со бой, например, постоянное запоминающее устройство с адресным принципом выборки информации и имеет адрееные входы и управляющий вход счи- 25 тывания данных. Блок памяти хранит тесты, состоящие из наборов кодовых комбинаций, причем каждому тесту соответствует определенная область памяти, которая определяется на- 30 чальным адресом соответствующей ячейки. Тесты представляют собой например, кодовые наборы символов русских, латинских, цифровых, чеРедующихся симВОлО — русских, латин-З5 ских, цифровых, определенное число одного какого-либо символа и т.д.

Считанные из блока памяти наборы тестов подаются на кодовые выходы

15-1, 15-2, 15-К, .число которых определяется числом разрядов кодовых 40 комбинаций тестов. Дополнительный разряд — управляющий выход 16 ис- пользуется в качестве указателя окончания данного теста, причем последняя кодовая комбинация каждого 45 теста содержит единичное значение разряда 16 и нулевое его значение для всех предыдущих кодовых комбинаций данного теста. Управляющий выход

14 блока 13 памяти предназначен для 50 управления адресным счетчиком 12 после чтения каждой кодовой комбинации.

Блок 6 задержки включения содер:.жит для каждого входного сигнала элемент 7 задержки и элемент И 8, которые обеспечивают задержку выходГ ного сигнала по отношению к входно му при подаче входного сигнала и снятие без задержки выходного сигнала при снятии входного сигнала. помощью клавиш 2-1, 2-2, 2-К набирают необходимую комбинацию тестов для контроля заданного объекта.

Каждая из клавиш 2 соответствует определенному тесту, записанному в определенной области памяти блока 13 памяти и заданному определенным начальным адресом. При нажатии на клавиши на их входах формируются импульсы, устанавливающие в единичные состояния соответствующие разряды 4 регистра 3. После набора состояние регистра 3 соответствует требуемой комбинации тестов. Сигналы с выходов сработанных разрядов 4 регистра 3 подаются на входы блока 5 приоритета, который формирует сигнал только на одном из своих выходов, соответствующем входному сигналу большего приоритета, например разряду 4-1. Этот сигнал с выхода блока 5 приоритета проходит через соответствующие эле менты задержки 7-1 и И 8-1 блока б задержки включения на первый вход соответствующего элемента И 9-1 и на. соответствующий вход шифратора 10.

При возбуждении входа шифратора 10 на его кодовых выходах формируется код начального адреса, соответствующий первому выбираемому по .приоритету тесту. Укаэанный код поступает на установочные входы счетчика 12 и записывается в нем. Таким образом, на выходах счетчика 12 устанавливается код начального адреса, который поступает на адресные входы блока 13 памяти. Кроме того, сигналы кода с выходов счетчика 12 через элемент ИЛИ 22 запускают ге-, нератор 17 импульсов. Импульсы с выхода генератора 17 поступают на входы элементов И 18, 19. Элементы И 18, 19 управляются сигналами с выходов триггера 20, причем в нулевом положении триггера 20 открыт элемент И 19 и закрыт элемент

И 18. Поэтому импульсы с выхода генератора 17 поступают через элемент

И -19 на.считывающий вход блока 13 памяти. Каждый импульс генератора 17, считывает одну кодовую комбинацию данного теста из блока памяти, начиная с адреса, указываемого счетчиком 12. Считанная кодовая комбинация теста подается с выходов 15 блока 13 памяти на проверяемый объект. После чтения каждой тестовой комбинации на выходе 14 блока памяти формируется импульс, поступающий на счетный вход счетчика 12.

При этом содержимое счетчика каждый раз увеличивается на +1 и соответствует адресу следующей ячейки области памяти данного теста. Таким образом, происходит последовательная выборка всех комбинаций первого теста из ячеек данной области памяти. При выборке последней кодо-.

1010632 вой комбинации теста на выходе 16 блока 13 памяти формируется единичный сигнал, который устанавливает триггер 20 в единичное состояние.

Триггер 20 закрывает элемент И 19 и открывает элемент И 18. Очередной 5 импульс с генератора 17 подается через элемент И 18 на вторые входы элементов И 9, на сбросовый вход счетчика 12 и на элемент 21 задержки. Этим импульсом открывается эле- 10 мент И 9-1, подготовленный к открыванию сигналом с выхода элемента И

8-1 блока 6 задержки включения.

Сигнал с вЫхода элемента И 9-1 поступает на нулевой вход соответствую-. 15 щего разряда 4-1 регистра 3 и обнуляет его. При этом снимаются сигналы на выходе блока 5 приоритета, на выходе элемента И 8-1 блока 6 задержки включения, на входе и выходах шифратора 10 и входах счетчика 12. Одновременно импульсом с выхода элемента И 18 обнуляется счетчик 12 и с задеракой, определяемой элементом 21, триггер 20. При этом снова открывается элемент И 19 и закрывается элемент И 1&. После сброса соответствующего разряда

4-1 в регистре 3 приоритет на выход в блоке 5 получает сигнал с выхода следующего сработанного разряда 4-2 ЗО регистра 3, и устройство переходит к выборке кодовых комбинаций следующего второго теста. Этот сигнал с задержкой, определяемой элементом

7-2 задержки, проходит на выход элемента И 8-2. Время задержки, задаваемое элементами 7 в блоке 6 задержки включения, превышает время задержки, задаваемое элементом

21, что обеспечивает обнуление счет.— чика 12 и триггера 20 к моменту формирования очередного сигнала на соответствующем выходе элемента

И 8-2 блока 6 задержки включения.

Сигнал с выхода элемента И 8-2 поступает нЪ вход элемента И 9-2 и на соответствующий вход шифратора 10, и описанный процесс повторяется.

Таким образом, происходит последовательная выборка заданных тестовых комбинаций требуемых тестов и их выдача на проверяемый объект.

Технико-экономическая эффективность .предлагаемого устройства заключается в расширении его функциональных возможностей по организации тестового контроля, в возможности формировать любые необходимые наборы тестов с помощью тестовой клавиатуры для контроля различных объектов без изменения электрических

Ф соединений, что повышает эффективность контроля и поиска неисправностей.

1010632 дихаРы

&dAI

Фиг.8

Составитель, .. И. Сигалов техредж.кастелевич Корректорф. Рошко

Редактор А. Ворович

Заказ 2490/38 Тираж 704 Подписное

ВНИИПИ Государственного комнтета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4