Запоминающее устройство с блокировкой неисправных элементов памяти

Иллюстрации

Показать всеРеферат

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С БЛОКИРОВКОЙ НЕИСПРАВНЫХ ЭЛЕМЕНТОВ ПАМЯТИ, содержащее регистр ввода информации , регистр вывода информации, блок памяти, генератбр импульсов, счетчики, дешифратор и накопитель, причем выходы регистра ввода информации подключены к информационным входам блока памяти, выходы которого соединены с входами регистра вывода информации, а адресные и управляющие входы - с адресными выходами первого и второго счетчиков и с выходами дешифратора соответственно, выход генератора импульсов подключен к счетному входу первого счетчика, выход переполнения которого соединен .со счетным входом второго счетчика, выход переполнения которого подключен к счетному входу третьего счетчика, выходы которого соединены с входами дешифратора, отличающееся тем, что, с целью повышения надежности устройства, в него введены четвертый счетчик, элементы ИЛИ и элементы И, причем первый и второй входы первого элемента ИЛИ подкл19чены соответственно к выходам переполнения первого и второго счетчиков , а выход соединен с установочным входом четвертого счетчика, выход переполнения которого подключен к информационному входу, накопителя, адресные входы и выход которого соединены соответственно с выходами дешифратора и с первым.управляющим входом третьего счетчика, первый вход и выход второго элемента ИЛИ подключены соответственно к первому входу первого элемента И и установочному входу первого счетчика и к первому входу второго элемента И;. выход и второй вход которого соединены соответственно ,со счетйымвз одом четвертого счетчиками выходом регистра вывода информации, второй вход и выход первого, элемента И подключены соответственно к выходу генератора И14пульсов и к управляющему входу второго счетчика, устаноВОЧ1ШЙ вход которого соединен с вторьт входом второго элемента ИЛИ и первым входом третьего элемента И, О второй вход которого подключен к выходу переполнения первого счетчика, ел ; а выход - к второму. управл5«ощему ND входу третьего счетчика, первые входы первого и третьегр элементов И являются входами контроля устройстваi

„„SU„„1010652 . A

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

3ДН G 11 C 11/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

:В

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЭОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3360247/18-24 (22) 05.12.81 (46) 07.04.83. Бюл. 9 13 (72) В.A. Васильев и И.Д. Соболев (53) 681. 327(088. 8 ) (56) 1. Авторское свидетельство СССР

9 600618, кл. G 11 С 29/00, 1976.

2. Авторское свидетельство СССР

В 641503, кл. С 11 С 29/00, 1976 (прототип). (54) (57) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С

БЛОКИРОВКОЙ НЕИСПРАВНЫХ ЭЛЕМЕНТОВ

ПАМЯТИ, содержащее регистр ввода информации, регистр7 вывода информации, блок памяти, генератор импульсов, счетчики, дешифратор и накопитель, причем выходы регистра ввода информации подключены к информационным входам"блока памяти, выходы которого соединены с входами регистра вывода информации, а адресные и управляющие входы - с адресными выходами первого и второго счетчиков и с выходами дешифратора соответственно, выход генератора импульсов подключен к счетному входу первого счетчика, выход переполнения которого соединен .со счетным входом второго счетчика, выход переполнения которого подключен к счетному входу третьего счетчика, выходы которого соединены с входами дешифратора, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, в него введены четвертый счетчик, элементы ИЛИ и элементы И, причем первый и второй входы первого элемента ИЛИ подклЮчены соответственно к выходам переполнения первого и второго счетчиков, а выход соединен с установочным входом четвертого счетчика, выход переполнения которого подключен к информационному входу, накопителя, адресные входы и выход которого соединены соответственно с выходами дешифратора и с первым. управляющим входом. третьего счетчика, первый вход и выход второго элемента ИЛИ подключены соответственно к первому входу первого элемента И и установочному входу первого счетчика и к 9 первому входу второго элемента И", выход и второй вход которого соединены соответственно,со счетным вхо-,даю дом четвертого счетчика.и выходом регистра вывода информации, второй вход и выход первого элемента И B подключены соответственно к выходу риыа генератора импульсов и к управляющему входу второго счетчика, установочный вход которого-соединен с вто- liaaaL рым входом второго элемента ИЛИ и первым входом третьего элемента И, второй вход которого подключен к вы- ф,) ходу переполнения первого счетчика, а выход — к второму управляющему входу третьего счетчика, первые вхо- )Я ды первого и третьего элементов И являются входами контроля устройства, 1010652 сов, счетчики, дешифратор и накопитель, причем выходы регистра ввода информации подключены к информационным входам блока памяти, выходы которого соединены с входами регистра вывода информации, а адресные и управляющие входы — с адресными выходами первого и второго счетчиков и с выходами дешифратора соответственно, выход генератора импульсов подключен к счетному входу первого счетчика, выход переполнения которого соединен со счетным входом второго счетчика, выход переполнения которого подключен к счетному входу третьего счетчика, выходы которого соединены с входами дешифратора, введены четвертый счетчик, элементы ИЛИ и элементы И, причем первый и второй входы. первого элемента ИЛИ подключены соответственно к выходам переполнения первого и второго счетчиков, а выход соединен с установочным входом четвертого счетчика, выход переполнения которого подключен к информационному входу накопителя, адресные входы и выход которого соединены соответственно с выходами дешифратора и с первым управляющим входом третьего счетчика, первый вход и выход второго элемента ИЛИ подключены соответственно к первому входу первого элемента И и установочному входу первого счетчика и к первому входу второго элемента И,.выход и второй вход которого соединены сОответственно со счетным входом четвертого счетчика и выходом регистра вы- вода информации, второй вход и выход первого элемента И подключены соответственно к выходу генератора импульсов и .< Управляющему входу второго счетчика, установочный вход которого соединен с вторым входом второго элемента ИЛИ и первым входом третьего элемента И, второй вход которого подключен к выходу переполнения первого счетчика, а выход — к второму управляющему входу третьего счетчи-. ка, первые входы первого и третьего элементов И являются входами контроля устройства.

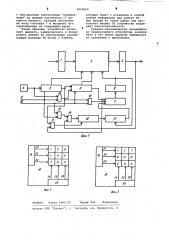

На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 и 3 — упрощенные структурные схемы запоминающей матрицы со .встроенным электронным "обрамлением".

Устройство содержит (фиг. 1) регистр 1 ввода информации, блок 2 памяти, выполненный на запоминающих матрицах с встроенными схемами управления, регистр 3 вывода информации, генератора 4 импульcos, первый 5 и второй б счетчики, предназначенные соответственно для счета строк и столбцов запоминающих матриц, тре-. тий счетчик 7, предназначенный для выбора запоминающих матриц, дешифратор 8. На фиг. 1 обозначены вход 9

Изобретение относится к вычисли— тельной технике и может быть применено в системах числового программного управления технологическим оборудованием.

Известно запоминающее устройство 5 с блокировкой неисправных элементов памяти, содержащее накопитель, элементы ИЛИ, дешифратор, регистр адреса, регистр слова, блок кодированиядекодирования, блок обнаружения и () анализа неисправностей и блок формирования управляющего кода (1 g.

Недостатками этого устройства являются сложность и невозможность диагностического контроля дешифратора. 5.

Из известных устройств наиболее близким техническим решением к предлагаемому является запоминающее устройство (ЗУ) с блокировкой неисправных элементов памяти, содержащее накопитель, адресный вход .которого подключен к адресному входу дополнительного накопителя и выходу регистра адреса, а выход — к одному из входов регистра числа, дешифратор, входы которого соединены соответственно с выходами дополнительного накопителя и блока контроля, а выход — с другим входом регистра числа, выход которого подключен к входу блока контроля, блок управления, дополнительный регистр, формирователь кодов, счетчик и коммутатор, первый вход которого подключен к выходу счетчика и входу дополнительного накопителя, второй вход — к выходу дополнительного ре- 35 гистра, а выход — к одному из входов блока управления, вход дополнительного регистра соединен с выходом накопителя, информационный вход которого подключен к выходу формирова- 4р теля кодов, входы которого .соединены со входом устройства и одним из выходов блока управления, другие выходы блока управления подключены к управляющему входу дополнительного 45 регистра и выходу счетчика (2 .

Недостатком устройства является низкая надежность, так как оно не позволяет определить неисправность встроенных схем управления запоминающих матриц, дешифраторов строк и столбцов, усилителей записи и считывания и т.д., что может привести к неправильному функционированию

ЗУ в целом и полной потери информации, а также вследствие ограниченнос-55 ти диагностического контроля ЗУ и больших аппаратурных затрат.

Цель изобретения — повышение надежности устройства. ,Поставленная цель достигается тем, что в запоминающее устройство с блокировкой неисправных элементов памяти, содержащее регистр ввода информации, регистр вывода информации, блок памяти, генератор импуль1010652 контроля строк и вход 10 контроля столбцов устройства.

Устройство содержит также (фиг.1) первый 11 и второй 12 элементы ИЛИ, первый 13, второй 14 и третий 15 элементы И, четвертый счетчик 16 и 5 накопитель 17, запоминающую матрицу .18 (фиг. 2 и 3), дешифратор 19 строк и дешифратор 20 столбцов, входящие в блок памяти, с выходами 21-23 и выходами 24-26 соответственно. На. 10 фиг. 2 показан пример распределения информации в запоминающих ячейках (ЗЯ) после записи тестового кода 111 000 000 при неисправности дешифратора столбцов по выходу 25 (в случае неисправности по выходу

24 во все ЗЯ матрицы записываются

"0"). На фиг. 3 для примера показано распределение информации в ЗЯ после записи тестового кода 100100100 при неисправности дешифратора строк по выходу 22(в случае неисправности по выходу 21 во все ЗЯ матрицы запишется,"0").

Устройство работает следующим образом.

В режиме подготовки к диагностическому контролю в блок 2 памяти записываются тестовые коды, которые подаются на вход регистра 1 (фиг. 1).

На входах 9 и 10 импульсы отсутству- ЗО ют, импульсы от генератора 4 поступают на счетный вход счетчика 5, им-. пульсы переполнения с которого поступают на счетный, вход счетчика б, импульсы переполнения с которого пос-35 тупают на,счетный вход счетчика 7, который через дешифратор 8 осуществляет выбор запоминающих матриц в блоке 2. Дпя контроля встроенных дешифраторов 19 и 20 (фиг. 2) исполь-4р зуют тестовый код, который обеспечивает запись в первый столбец запоминающих матриц 18 ™1" ("0"), а в остальные — "ой ("1")

Ь

В режиме диагностического контро- 45 ля производится считывание тестового кода. Для проверки дешифраторов 20 на вход 10 (фиг. 1) подается сигнал (логическая "1"). При этом работа счетчика 6 блокируется и он устанавливается в положение выбора первого столбца в блоке 2, через элемент И 15 разрешается работа счетчика 7, через элемент ИЛИ 12 и элемент И 14 раэрешается работа счетчика 16. Импульсы от генератора 4 поступают на счетный вход счетчика 5 и происходит опрос первой матрицы блока 2, импульс пере- полнения с выхода счетчика 5 через элемент И 15 производит переключение счетчика 7 и через элемент ИЛИ 11 60 сбрасывает счетчик 16, при этом происходит опрос второй матрицы блока 2 и т.д. Если в опрашиваемой матрице дешифратор 20 исправен, то будет считываться только первый столбец (фиг. 2), т.е. "1" ("0") . Если дешифратор 20 неисправен, т. е. один из его выходов (например, 25) является генератором "1", то одновременно будут считываться два столбца (первый и второй). В результате на выходе блока 2 (фиг. 1) импульс появится "0" ("1"), который через регистр 3 и элемент И 14 поступит на счетный вход счетчика 16 и переключит его. Если при опросе одной из матриц 18 в режиме диагностического контроля будет считано число "0" ("1"), большее коэффициента пересчета счетчика 16 (равное примерно половине числа разрядов в столбце), то импульс переполнения с выхода счетчика 16 запишется в накопитель 17 по адресу опрашиваемой матрицы 18, т.е. в накопителе 17 запишется адрес неисправной матрицы. Для контроля встроенных дешифраторов 19 используется тестовый код, который обеспечивает запись в первую строку матриц 18 "1" ("0"), а в остальные

"0" ("1") (фиг. 3). Для проверки дешифраторов 19 на вход 9 подается импульс (логическая "1") (фиг. 1). Чри этом работа счетчика 5. блокирует-. ся и он устанавливается .в положение выбора первой строки, через элемент И 13 разрешается работа счетчика б от генератора 4, через элемент ИЛИ 12 и элемент И 14 разрешается работа счетчика 16..

Импульсы от генератора 4 через элемент И 13 поступают на счетный вход. счетчика 6 и происходит опрос первой матрицы, импульс переполнения с выхода счетчика б производит переключение счетчика 7 и через элемент HJIH 11 сбрасывает счетчик,16.

Происходит опрос второй матрицы 18 блока 2 и т.д. Если в опрашиваемой матрице 18 дешифраторы 19 исправны, то будет считываться только первая строка (фиг. 3), т.е. "1" ("0".).

Если дешифратор 19 неисправен, т.е. один из его выходов (например, 22) является генератором "1", то одновременно будут считываться две строки (первая и вторая), в результате на выходе блока 2 (фиг. 1) появится

"0" ("1"), который через регистр 3 и элемент H 14 поступит на счетный вход счетчика 16 и переключит его.

Если при опросе одной из матрицы 18 в режиме диагностического контроля будет считано число "0" ("1".), большее коэффициента пересчета счетчика

16, то импульс переполнения с его выхода запишется в накопитель 17, таким образом, в накопителе 17 зафиксируется адрес неисправной матрицы 18 блока 2.

В режиме записи или считывания информации с блока 2 при появлении на дешифраторе 8 адреса матрицы 18

1010б52

Фм. 1

ВНИИПИ Заказ 2495/39 Тираж 592 Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 с неисправным электронным "обрамлением" на выходе накопителя 17 появится импульс, который поступает на вход счетчика 7 и вызывает. его переключение на следующий адрес.

Таким абразом, устройство позволяет выявить, зафиксировать и блокировать именно те неисправные запоминающие матрицы 18 блока 2 памяти, которые ведут к искажению и полной потере информации при работе ЗУ.

При выходе из строя одной или нескольких матриц 18 устройство сохраняет работоспособность.

Технико-экономическое преимущество предлагаемого устройства эаключается в его более высокой надежности по сравнению с прототипом.