Устройство ввода поправок в аналого-цифровой параллельно- последовательный следяной преобразователь

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ВВОДА ПОПРАВОК В АНАЛОГО-ЦИФРОВОЙ ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ СЛЕДЯЩИЙ ПРЕОБРАЗОВА ,ТЕЛЬ, содержащее п первых элементов ИЛИ, соответствующих п разрядам преобразователя , BxotoJ которых подключены к соответствующим входным числовым шинам, первые элементы И, первый вход каждого --из которых подключен к выходу соответствующего первого элемента ИЛИ, а выход каждого элемента И, кроме первого разряда, : подключен к первому входу соответствующего второго элемента ИЛИ, второй и третий входы которого подсоединены к шинам .положительного и отрицательного превышения декадного интервала, а выход подключен к соответствующей выходной шине, вторые и третьи элементы И, первые входы которых в каждом разряде, кроме первого , подключены соответственно к первым шинам полярности последующих разрядов, вторые входы - к второй шине знакового разряда, а выходы в каждом разряде, кроме первого, подключены к входу соответствующего третьего элемента ИЛИ, четвертые элементы Ив каждом разряде, кроме последнего и знакового, первые входы -Х ГЛ .- -;t- „ 5 Л 7j : г ;::-,а у .,1 J - l;,.- .г; f г i. S: 1 t ufeiJ;fb3J:;;4i которых в разрядах, кроме первого, подключены к шинам знака О последующих разрядов, отличаю,г щ е е с я тем, что, с целью расширения рабочего диапазона вводимых поправок, во все разряды, кроме последнего и знакового, введены четвертые элементы ИЛИ, а разряды , кроме первого, последнего и знакового J - пятые элементы ИЛИ,-а в первый разряд - второй и третий элементы И, выходы которых подключены к входу третьего элемента ИЛИ, выход которого соединен с первым входом четвертого элемента ИЛИ, первые входы - к шинам полярности второго разряда, а вторые входы - к второй шине знакового разряда, причем перСО вый вход четвертого элег Лента ИЛИ в каждом разряде соединен с выходом третьего элемента ИЛИ, а второй вход к выходу четвертого элемента И, первый вход которого в первом разряде подключен к шине знака О второго разряда, а второй вход в каждом разряде - к выходу пятого элемента ИЛИ последующего разряда,, первый вход которого в каждом разряде подключен к первому входу четвертого элемента ИЛИ , второй - к второму входу 1С четвертого элемента ИЛИ, первый и второй входы второго элемента ИЛИ в первом разряде подключены к шинам положительного и отрицательного превышения декадного интервала, выходы - к выходной шине, а третий вход соединен с выходом первого элемента И, второй вход которого в каждом разряде, кроме последнего и знакового , подключен к выходу четвертого элемента ИЛИ.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТ) ИЕСКИХ

РЕСПУБЛИК

З(51) Н 03 К 13 02

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕЛ=НИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Й лвторском г свиднтнпьствы

21) 2995472/18-21

22) 20. 10. 80

° ° °

46) 07.04.83. Бюл. Р 13

72) Л..П.Петренко (53) 681.325(088.8) (56) .1. Цифровые измерительные приборы ° Под. ред. В.И.Шляндина. М., "Энергия", 1972, с. 292-205,рис.8-2.

2. Авторское свидетелЬство СССР

Р 866487, кл. Н 03 К 13/02, 04.10.79 (прототип}. (54)(57) УСТРОЙСТВО ВВОДА ПОПРАВОК

В АНАЛОГО-ЦИФРОВОЙ ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ СЛЕДЯЩИЙ ПРЕОБРАЗОВА,TEJIb содержащее ту первых элементов

ИЛИ, соответствующих и разрядам преобразователя, входы которых подключены к соответствующим входным числовым шинам, первые элементы И, первый вход каждого из которых подключен к выходу соотнетствующего перного элемента ИЛИ, а выход каждого элемента И, кроме перного разряда,,подключен к первому входу соответствующего второго элемента ИЛИ, второй и третий входы которого подсоединены к шинам положительного и отрицательного превышения декадного интервала, а выход подключен к соответствующей выходной шине, вторые и третьи элементы И, первые входы которых в каждом разряде, кроме первого, подключены соответственно к первым шинам полярности последующих разрядов,.вторые входы — к второй шине знакового разряда, а выходы в каждом разряде, кроме первого, подключены к входу соответствующего третьего элемента ИЛИ, четвертые элементы И в каждом разряде, кроме последнего и знакового, первые входы

„„SU„„1010721 А которых в разрядах, кроме первого, подключены к шинам знака "0" последующих разрядов, о т л и ч а ю ;, щ е е с я тем, что, с целью расширения рабочего диапазона вводимых поправок, но все разряды, кроме последнего и знакового, введены четвертые элементы ИЛИ, а разряды, кроме первого, последнего и знакового, — пятые элементы ИЛИ,"а в первый разряд — второй и третий элементы И, выходы которых подключены к входу третьего элемента ИЛИ, выход которого соединен с первым входом четвертого элемента ИЛИ, первые входы — к шинам полярности второго разряда, а вторые входы — к второй шине знакового разряда, причем первый вход четвертого элемента ИЛИ в каждом разряде соединен с выходом третьего элемента ИЛИ, а второй вход к выходу четвертого элемента И, первый вход которого в первом разряде подключен к шине знака "0" второго разряда, а второй вход в каждОм разряде — к выходу пятого элемента ИЛИ последующего разряда, первый вход которого в каждом разряде подключен к первому входу четвертого элемента ИЛИ; второй — к второму входу четвертого элемента ИЛИ, первый и второй входы второго элемента ИЛИ в первом разряде подключены к шинам положительного и отрицательного превышения декадного интервала, выходы — к выходной шине, а третий нКод соединен с выходом первого элемента

И, второй вход которого н каждом разряде, кроме последнего и знакового, подключен к выходу четвертого элемента ИЛИ.

1010721

Изобретение относится к цифровой измерительной и вычислительной технике, а именно к конструкции устройства ввода поправок в аналогоцифровые преобразователи (АЦП),используемые при измерении напряжений.

Известен АЦП с устройством ввода поправок, разряды которого содержат цифровой амплитудный анализ атор ДАА), делитель напряжения, блок ввода поправок и вычитающее устройство (1 )."О

Недостатком указанного преобразователя является низкая точность.

Известен также аналого-цифровой параллельно-последовательный следящий преобразователь, в котором уст- »5 ройство ввода поправок содержит г» первых элементов ИЛИ, соответствующих разрядам преобразователя, входы которых подключены к соответствующим входным числовым шинам, первые элементы И, первый вход каждого из которых подключен к выходу соответствующего первого элемента ИЛИ, а выход каждого элемента И, кроме первого, разряда подключен к первому входу соответствующего второго элемента

ИЛИ, второй и третий входы которого подсоединены к шинам положительного и отрицательного превышения декадного интервала, а выход подключен к соответствующей выходной шине, вторые и третьи элементы И, входы которых в каждом разряде, кроме первого, подключены соответственно к первым шинам полярности последующих разрядов, вторые входы - к второй шине знакового разряда, а выходы в каждом разряде, кроме первого, подключены к входам третьего элемента ИЛИ, четвертые элементы И в каждом разряде, кроме первого, подключены к шинам 40 знака "0" последующих разрядов 2 .

Недостатком известного устройства ввода поправок является ограниченность рабочего диапазона, так как при определении поправки в ЦАА преобразователя, величина которой больше или равна интервалу разрешающей способности ЦАА очередного разряда, устройство ввода поправок не может внести поправку в соответствующие разряды преобразователя.

Цель изобретения — расширение рабочего диапазона ввода поправок, Поставленная. цель достигается .тем, что в устройство ввода попра- э5 вок в аналого-цифровой параллельнопоследовательный следящий преобразователь,содержащее и первых элементов ИЛИ, соответствующих и разрядам преобразователя, входы которых 60 подключены к соответствующим входным числовым шинам, первые элементы

И, первый вход каждого из которых подключен к выходу соответствующего первого элемента ИЛИ, а выход каж- у дого элемента И, кроме первого разряда, подключен к первому входу соответствующего второго элемента

ИЛИ, второй и третий входы которого подсоединены к шинам положительного и отрицательного превышения декадного интервала, а выход подключен к . соответствующей выходной шине, вторые и третьи элементы И, первые входы которых в каждом разряде, кроме первого, подключены соответственно к первым шинам полярности последующих разрядов, вторые входы — к второй шине знакового разряда, а выходы— в каждом разряде, кроме первого, подключены к входу соответствующего третьего элемента ИЛИ, четвертые элементы И в каждом разряде, кроме последнего и знакового, первые входы которых в разрядах, кроме первого, подключены к шинам знака "0" последующих разрядов, во все разряды, кроме последнего и знакового, введены четвертые элементы ИЛИ, в разряды, кроме первого, последнего и знакового, — пятые элементы ИЛИ, а в первый разряд — второй и третий элементы И, выходы которых подключены к входу третьего элемента ИЛИ, выход которого соединен с первым входом четвертого элемента ИЛИ, первые входы — к шинам полярности второго разряда, а вторые входы — к второй шине знакового разряда, причем первый вход четвертого элемента ИЛИ в каждом разряде соединен с выходом третьего элемента ИЛИ б, а второй вход - z выходу четвертого элемента И, первый вход которого в первом разряде подключен к шине знака "0" второго разряда, а второй вход в каждом разряде — с выходом пятого элемента ИЛИ последующего разряда, первый вход которого в каждом разряде подключен к первому входу четвертого элемента ИЛИ, второй вход — к второму входу четвертого элемента ИЛИ, первый и второй входы второго элемента ИЛИ в первом разряде подключены к шинам положительного и отрицательного превышения декадного интервала, выход — к выходной шине, а третий вход соединен с выходом первого элемента И, второй вход которого в каждом разряде, кроме последнего и знакового, подключен к выходу четвертого элемента ИЛИ.

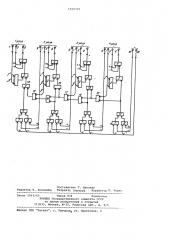

На чертеже изображена блок-схема предлагаемого устройства.

Устройство содержит входные клеммы 1, соответствующие знакам "0" и от "1" до "9" во всех разрядах, кроме последнего, подключенные к входам первых элементов ИЛИ 2, первые элементы И 3, первые входы которых подключены к выходам первых элементов

ИЛИ 2, а выходы во всех разрядах, кроме последнего, подключены к пер1010721 вым входам вторых элементов ИЛИ 4, второй и третий входы элемента

ИЛИ 4 подсоединены к клеммам 5 поло жительного (+х } н отрицательного -х ) превышения декадного интервала, а выход подключен к выходной клемме б своего разряда, входы вторых и третьих элементов 7 и 8 подключены соответственно к клеммам 9 отрицательной н положительной полярности входного сигнала последующих разрядов, а их вторые входы подключены к клеммам 10 положительной и отрицательной полярности дополнительного входа последнего разряда. Выходы второго и третьего элементов И 7 и

8 подключены к входам третьего элемента ИЛИ 11, первые входы четвер тых элементов И 12 подключены к клеммам 1 знака "0" последующих разрядов, во все разряды, кроме двух последних, введены четвертые .элементы ИЛИ 13, а в разряды, кроме первого и двух последних — пятые элементы ИЛИ 14.

Вторые входы первых элементов

И 3 подключены к выходам четвертых элементов И 13, первые входы которых соединены с выходами третьих элементов ИЛИ 11, а вторые - подключены к выходам четвертых: элементов И 12. Вторые входы четвертых элементов И 12 соединены с выходами пятых элементов ИЛИ 14 последующих разрядов, первые входы которых.под- ключены к первым входам четвертых элементов ИЛИ 13. Вторые входы пятых элементов ИЛИ 14 соединены с вторыми входами четвертых элементов ИЛИ 12

Устройство работает следующим образом.

Предположим, что на вход АЦП подан входной сигнал USÕ= 24,0 В, а он .зафиксировал выходйой код, который соответствует 23,7, В этом случае с учетом принципа работы параллельно-последовательного преобразователя, если входной сигнал равен 24,0 В и первый разряд зафиксировал знак "2", то на очередной разряд обработки AIIII поступают два сигнала - это входной +24,0 В и компенсирующий — 20,0 В, в результате этого формируется разностный сигнал (24,0 - 20,0 4,0 В).

Предположим, что во втором разряде обработки вместо знака "4". АЦП зафиксировал знак "3" (23-,7 В ) и на

5 очередной третий разряд обработки

АЦП поступает два.сигнала - входной

+24,0 В и компенсирующий — 23,0 В, в результате разностный сигнал будет равен 24,0 — 23,0 = 1,0 В.

10 Если учесть диапазон этого разряда, то величина 1,0 В для него будет выходить .за его пределы„ что приводят к зашкаливанию в ЦАА, вследствие чего сигнал появится на шинах

15 +х, а коррекрирующий сигнал через элемент HJIH 4 третьего разряда пос,тупает на один из входов ЦАА соответствующего разряда обработки

AOJI, в котором на выходе установится близким к .разностному сигналу 1,0 В знак "9"., В результате информационный сигнал корректировки погрешности с выхода +х третьего разряда исчезает.

На четвертый разряд АЦП поступают сигналы — входной +24,0 В и компен сирующий — 23,9 ф,разностый сигнал будет равен 0,1 В (24,0 - 23,9

= 0,1 В) и т;д. В конечном счете

ЗО с помощью предлагаемого устройства

АЦП зафиксирует выходной под эквивалентный сигналу в 23,999 ... В, т.е. с минимальной погрешностью.

В случае, если пороги срабатыва35 ния ЦАА дрейфуют, то устройство ввода поправок также может исправлять, результат преобразования АЦП. Например, дрейф порогов срабатывания

ЦАА соседних разряцов происходит в

40 одном направлении + и +, — и — . в случае, когда при входном сигнале

30,0 В будет зафиксирован в первом разряде знак 4, В результате разностный сигнал в Mgt очередного раз45 :ряда будет равен -10,0 В (30,0— 40,0 = -.10,0 ), что приводит к no— явлению сигнала на двух входах элемента И 7 и через элементы ИЛИ 11 и

13, И 3 и ИЛИ 13 корректирующий сигнал поступает на дополнительный вход ЦАА первого разряда.

1010721 юозас

Составитель Г. Наповал

Редактор Н. Ковалева Техред М. Коштура Корректор . Рошко

E Рошко

Заказ 2503/43 Тираж 934 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.. 4/5

Филиал ППП "Патент", r. ужгород ул. Проектная, 4