Преобразователь уровня сигналов

Иллюстрации

Показать всеРеферат

1. ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ СИГНАЛОВ, содержавший входной дифференциальный переключатель тока на первом и втором транзисторах, эмиттеры которых подключены к генератору тока, базы - к входам устройства, и выходной ТТЛ каскад, эмиттер нижнего транзистора которого подключен к общей шине, а коллектор верхнего транзистора через резистор - к шине питания j отличающийся тем, что,- с целью повьшения быстродействия и уменьшения потребляемой мощности, коллекторы первого и второго транзисторов подключены соответственно к эмиттерам третьего и четвертого транзисторов , базы которых подключены к общей шине, а коллекторы - соответственно к базам верхнего и нижнего транзисторов выходного ТТЛ каскада, коллектор нижнего транзистора которого подключен к выходу и через диод к эмиттеру верхнего транзистора, база которого через резистор подключена к шине питания, коллекторы пятого и шестого транзисторов подключены к ши .не питания, базы - к источникам опорных напряжений, а эмиттеры соответственно через резистор и непосредственно подключены к коллекторам второго и третьего транзисторов. 2. Преобразователь по п.1, -о т л и ч а ющ и и с я тем, что, с целью его расширения функциональных возможностей, введен управляющий дифференциальный каскад, базы транзисторов которого подключены к стробируюсл щим входам устройства, эмиттеры - к генератору тока, а коллекторы - соответственно к эмиттерам транзисторов входного дифференциального переключателя тока и эмиттерам транзисторов триггера с непосредственными коллекторно-базовыми связями, коллекторы транзисторов которого подключены соответственно к коллекторам транзисторов входного дифференциального переключателя тока.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

1 5 А (1Ю (И) (59 4 Н 03 К 19/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

°, ° °, ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ! (21) 3232603/18-21 (22) 09.01.81 (46) 15. 11.88. Бюл. № 42 (72) Е.А.Рябов и Ц.В.Сотский (53) 621.375.083(088.8) (56) Авторское свидетельство СССР №- 411644, кл. Н 03 К 19/08, 1972.

Авторское свидетельство СССР

¹ 617844, кл. Н 03 К 19/00, 1977. (54) (57) 1. ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ

СИГНАЛОВ, содержащий входной дифференциальный переключатель тоха на первом и втором транзисторах, эмиттеры которых подключены к генератору тока, базы - к входам устройства, и выходной ТТЛ каскад, эмиттер нижнего транзистора которого подключен к odщей шине, а коллектор верхнего транзистора через резистор — к шине питания, отличающийся тем, что; с целью повышения быстродействия и уменьшения потребляемой мощности, коллекторы первого и второго транзисторов подключены соответственно к эмиттерам третьего и четвертого транзисторов, базы которых подключены к общей шине, а коллекторы — соответственно к базам верхнего и нижнего транзисторов выходного ТТЛ каскада, коллектор нижнего транзистора которого подключен к выходу и через диод— к эмиттеру верхнего транзистора, база которого через резистор подключена к шине питания, коллекторы пятого и шестого транзисторов подключены к шине питания, базы — к источникам опорных напряжений, а эмиттеры соответственно через резистор и непосредственно подключены к коллекторам второго и третьего транзисторов.

2. Преобразователь по п. 1, .о т— л и ч а ю шийся тем, что, с целью его расширения функциональных воэможностей, введен управляющий дифференциальный каскад, базы транзисторов которого подключены к стробирующим входам устройства, эмиттеры — к генератору тока, а коллекторы — соответственно к эмиттерам транзисторов входного дифференциального переключателя тока и эмиттерам транзисторов триггера с непосредственными коллекторно-базовыми связями, коллекторы транзисторов которого подключены соответственно к коллекторам транзисторов входного дифференциального переключателя тока.

101 1025

Изобретение относится к импульсной технике и может быть использовано в компараторах напряжения, в выходных регистрах хранения, в частности в ин- 5 тегральных аналого-цифровых преобраз ователях, Известно устройство, содержащее входной дифференциальный каскад, выходы которого подключены к входам двух выходных ТТЛ каскадов.

Недостатком устройства является низкое быстродействие и большая потребляемая мощность.

Известен также ТЛЭС-ТТЛ преобра- 15 зователь, содержащий входной дифференциальный переключатель тока на двух транзисторах, эмиттеры которых подключены к источнику тока, базы— к входам устройства, и выходные ТТЛ 20 каскады, эмиттеры нижних транзисторов которых подключены к общей шине, а коллекторы верхних транзисторов через резистор — к шине питания.

Недостатком такого преобразователя 25 является низкое быстродействие и большая потребляемая мощность.

Цель изобретения — повышение быстродействия и уменьшение потребляемой мощности преобразователя. 30

Для достижения поставленной цели в преобразователе„содержащем входной дифференциальный переключатель тока на первом и втором транзисторах, эмиттеры KoTop6Ix подключены к Генера тору тока, базы - к входам устройства и выходной ТТЛ каскад„ эмиттер нижнего транзистора которого подключен к общей шине, а коллектор верхнего транзистора — к шине питания, кол-рр лекторы первого и второго транзисторов подключены соответственно к эмиттерам третьего и четвертого транзисторов, базы которых подключены к общей шине, а коллекторы - соответственно к базам верхнего и нижнего транзисторов выходного ТТЛ,"каскада, коллектор нижнего транзистора которого подключен к выходу и через диод к эмиттеру верхнего транзистора, база которого через резистор подключена к шине питания, базы - к источникам опорных напряжений, а эмиттеры соответственно через резистор, и непосредственно подключены к коллекторам второго и третьего транзисторов, а кро- ме того,. введен управляющий дифференциальный каскад, базы транзисторов которого подключены к стробирующим входам устройства, эмиттеры — к генератору тока, а коллекторы — соответственно к эмиттерам транзисторов входного дифференциального переключателя тока и к эмиттерам транзисторов триггера с непосредственными коллекторно-базовыми связями, коллекторы транзисторов. которого подключены соответственно к коллекторам транзисторов входного дифференциального переключателя тока.

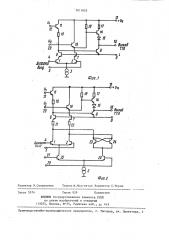

На. фиг.1 приведена принципиальная схема преобразователя дифференциальных сигналов в ТТЛ уровни; на фиг.2— принципиальная схема стробируемого преобразователя дифференциальных сигналов в ТТЛ уровни.

Преобразователь уровня (фиг.1) содержит входной дифференциальный переключатель тока на первом и втором транзисторах 1, 2, эмиттеры которых подсоединены к генератору постоянного тока 3, их базы являются входами

4 и 5 преобразователя, базы третьего и четвертого транзисторов 6, ? соединены с общей шиной 8, их эмиттеры соединены соответственно с коллекторами первого и второго транзисторов 1, 2 коллектор третьего транзистора 6 соединен с базой нижнего транзистора 9 выходного ТТЛ каскада и через резистор 10 с эмиттером пятого транзистора 11, на базу которого подается опорное напряжения от источника опорного напряжения 12, ограничивающее степень насыщения нижнего транзистора 9, коллектор пятого транзистора 11 подключен к шине питания 13, коллектор третьего транзистора 7 подключен к базе верхнего транзистора 14, эмиттер которого через прямосмещенный диод 15 подключен к коллектору нижнего транзистора 9, являющегося выходом

16 преобразователя уровня, коллектор верхнего транзистора 14 через резистор 17 подключен к шине питания 13, кроме того, коллектор транзистора 17 соединен через резистор 18 с шиной питания 13 и с эмиттером шестого транзистора 19, на базу которого подается опорное напряжение от источника опорного напряжения 20, а его коллектор соединен с шиной питания 13.

В схему преобразователя уровня (фиг.1) введен стробирующий триггерзащелка (фиг.2), содержащий входной дифференциальный переключатель тока на первом и втором транзисторах 1, 2, з «0110 базы которых являются входами 4 и 5 преобразователя, а коллекторы соединены соответственно через резисторы

21 22 с эмиттерами третьего и четФ

5 вертого транзисторов 6, 7, коллекторы транзисторов 23, 24 триггера непосредственно коллекторно-базовыми связями подключены соответственно к коллекторам первого и второго транзис- 10 торов 1, 2, эмиттеры которых подключены к коллектбру одного иэ транзис, торов 25 управляющего дифференциального каскада, коллектор другого транзистора которого 26 подключен к эмит- 15 терам транзисторов 23 и 24 триггера, эмиттеры транзисторов 25, 26 управляющего дифференциального каскада соединены с генератором постоянного тока 3, а их базы подключены к строби- 2р рующим входам 27, 28 устройства.

Преобразователь (фиг.1) работает следующим образом.

При подаче на входы 4, 5 дифференциального логического сигнала, напри- 25 мер на вход 4 — логического "О", а на вход 5 — соответственно логической весь ток генератора постоянного тока 3 потечет через второй и четвертый транзисторы 2, 7 и создаст на ре- З0 зисторе 13 падение напряжения, при этом потенциал на базе верхнего тран. зистора 14 будет снижаться до величины, зафиксированной эмиттером шестого транзистора 19, у которого на базе установлено напряжение U< равное

0,7 В, таким образом верхний транзистор 14 будет надежно заперт.

База нижнего транзистора 9 через токоограничивающий резистор 10 под- 40 ключена к эмиттеру пятого транзистора 11, на базе которого установлено напряжение U, равное 1,7 В при этом нижний транзистор 9 открывается, и на выходе преобразователя уровня 16 бу- 4 дет низкий потенциал, соответствующий логическому "О" ТТЛ элементов при изменении сигнала на дидк9еренциальных входах 4, 5 на обратный, т.е. на вход 4 подается уровень, соответству- БО ющий логической "1", а на вход 5— соответствующий логическому "О", тог- да ток генератора тока 3 потечет через первый и третий транзисторы 1, 6 и создаст на резисторе 10 падение напряжения, достаточное для залирания нижнего транзистора 9, через резистор 18 ток отсутствует, и на базе верхнего транзистора 14 будет высокий потенциал, верхний транзистор 14 открыт, при этом на выходе преобразователя будет высокий потенциал, соот- . ветствующий логический "1" ТТЛ элементов.

Работа стробируемого преобразователя уровня, приведенного на фиг.2, практически не отличается от приведенного на фиг.1, за исключением наличия возможности хранения информа- . ции, управление работой триггера с непосредственными коллекторно-базовы-ми связями осуществляется сигналом, подаваемым на стробирующне входы 27, 28. Например, на вход 27 подан сигнал, соответствующий логической "1", а на вход 28 — логическому "0", ток генератора тока 3 потечет через транзистор 25 к эмиттерам первого и второго транзисторов 1, 2, при этом устройство будет находиться в режиме слежения за информацией, подаваемой на входы 4, 5. При изменении сигнала управления на стробирующих входах 27;

28 на обратные, т.е. на вход 27 подан логический "О", а на вход 28 - логическая "1", ток от генератора тока 3 потечет через транзистор 26 на эмиттеры транзисторов 23, 24 триггера и триггер переключится в режим хранения информации, которая была на входах

4, 5, и преобразователь уровня перестает принимать информацию по этим входам, пока не изменится управляющий сигнал на стробирующих входах 27, 28.

Предлагаемый преобразователь уровня сигналов может быть реализован в интегральном исполнении в регистре последовательного приближения быстродействующего аналого-цифрового преобразователя в качестве выходного регистра хранения информации, это позволит уменьшить потребляемую мощность каждой ячейкой выходного регистра хранения примерно до 10 мВт, при этом частота обновления информации достигает 40 мГц.

1011025

Дар

Уход

Техред М.Моргентал Корректор С.Черни

Редактор Н.Сильнягина

Тираж 929 Подписное

Заказ 5574

ВНИИПИ Государственного комитета СССР по делам изо6ретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4