Множительно-делительное устройство

Иллюстрации

Показать всеРеферат

МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО , содержащее множитёльно-делительный блок с токовым выходом, входы которого являются аналоговыми входакм устройства, а выход соединен со входом операционного усилителя,Шход которого является аналоговый выходом устройства, о т л и ч а ю щ е е с я TGMi 4TOi с целью повышения точностиработы устройства и расширения динамического диапазона изменения переменных за счет представления их в гибри : ной аналого-цифровой форме, е него введены цифроуправляемая проводикюсть, компаратор, реверсивный счетчик и два цифровых сумматора, причем входы пёр вого из цифровых сумматоров являются цифровыми .входами устройства., а выход подключён к первому входу второго «ифрового сумматора, выход которого является цифровым выходом ycTpoJicTBa, а второй вход второго цифрового сумйа тора соединен с первым выходом рев сивного счетчика, подключенного вто рым выходом к управляющему входу 1|(ф роуправляемой проводимости, подклпченной между выходом и входсм4 операционного усилителя, выход компаратера соединен со входом реверсивного счетчика, а выход операционного yqiлителя подключен к вход компа| атора . - -.- . - :.

СОЮЗ СОВЕТСКИХ

Ц

РЕСПУБЛИК ущр С 06 С 7/16

ГОСУДАРСТВЕННЫЙ .КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTHA (21) 3362111/18-24 (22) 10 ..12.81 (46),15.04.83. 6юл. И 14 (72) А.А.Шкиль и А,H.Äèãóí (71) Институт гидромеханики АН Ук .раинской CCP " (53) 681335(088.8) (56) 1 ° Алексенко A.Ã., Коломбер Е,А,, :Стародуб Г.И. Применение прецизион ных аналоговых И.С. И,, "Радио и связь!, 1981, с. 92 104, 2. Патент США N 3940603, кл. 235-. 195,- опублик. 1976 (прото- тип) . (54) (57) ИНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее множительно-делительйый блок с токовым выходом, входы которого являются аналоговыми вхо-. дами устройства, а выход соединен co входом операционного усилителя, выход которого является аналоговым выходом устройства, о т л и ч а ю.щ е е с я, тем, что; с целью повышения точностй работы устройства и расширения динамического диапазона изменения перемен" ных за счет представления их в гибрйдной аналого-цифровой форме, в него введены цифроуправляемая проводимость, компаратор, реверсивный счетчик и два. цифровых суэннатора, причем входы первого из цифровых сумматоров является цифровыми, входами устройства, а выход подключен к первому входу второго цифрового сумматора, выход -которого является цифровым выходом устройства, а второй вход второго цифрового сумма" тора соединен с первым выходом ревер» сивного счетчика, подключейного вторым выходом к управляющему входу циф» роуправляемой проводимости., подклю-, ченной между выходом и входом операционного усилителя, выход компарато.ра соединен со входои реверсивного счетчика, а выход операционного уси- . e O лителя подключен к входу компаратоI ра.

1011622

Изобретение относится к аналоговой и гибридной вычислительной темни ке.

Известны устройства для перемноже-., ния - деления аналоговых величин, со--5 держащие множительно-делительные блоки и операционные усилители $1)

Эти устройства характеризуются недостатo4HG высокой точностью.

Наиболее близким техническим решением к изобретению является множительио-делительное устройство, содержащее входной множительно-делительный блок с токовым выходом и операционный усилитель (2).

Известное устройство характеризует; ся недостаточно высокой точностью и узким диапазоном изменения переменных.

Целью изобретения является повыше-щ ние точности работы устройства и рас- . ширение динамического диапазона изме" нения переменных за счет представле" ния их в гибридной цифро"аналоговой,форме. 25

Поставленная цель достигается тем, что в множительно-делительное устрой" ство, содержащее множительно-делительный блок с токовым выходом, входы которого являются аналоговыми входа- 30 ми усройства, а выход соединен со входом операционного усилителя, выход которого является аналоговым выходом устройства, дополнительно введены цифроуправляемая проводимость, компаратор, реверсивный счетчик и два цифро" вых сумматора, причем входы первого из цифровых сумматоров являются цифровыми входами устройства, а выход подключен к первому входу второго циф4, рового сумматора, выход которого является цифровым выходом устройства, а второй вход второго цифрового сумматора соединен с первым выходом реверсивного счетчика, подключенного вто" 45 рым выходом к управляющему входу цифроуправляемой проводимости, подключен" ной между выходом и входом операционногь усилителя, выход компаратора соединен со входом реверсивного счетчика, а выход операционного усили=

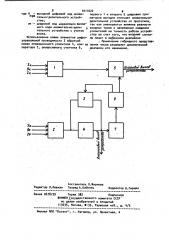

50 теля подключен к входу компаратора, На чертеже приведена структурная схема множительно-делительного устройства.

Устройство содержит первый цифро- 5 вой сумматор 1умножительно-делительный блок 2 с токовым выходом, цифроуправляемую проводимость 3, операци-. онный усилитель 4, второй цифровой сумматор 5, реверсивный счетчик 6 и компаратор 7.

Входным величинам ставится в соответствие произведение

Х=х„ ч где Х „- аналоговая часть входной величины Х, которая изменяется в пределах t U );

U - максимально допустймое напряжение для представления аналоговой, части, K - основание, Х - цифровая часть входной веЦ ! личины Х.

Выходной ток входного множительноделительного блока 2 описывается, выражением

I где 11, - ток, пропорциональный входной величине Х;

1 - ток, пропорциональный входу ной величине ;

1 - ток, пропорциональный входной величине Z.

Сигнал с выхода операционного усилителя подается на вход компаратора 7. В случае,.если выходное напряжение операционного усилителя не ле- . жит. в выбранном диапазоне (U », компаратор вырабатывает сигнал,, под действием которого изменяется выходное состояние реверсивного счетчика 6, который, управляя цифроуправляемой проводимостью 3 в обратной связи операционного усилителя 4, возвращает выходной сигнал операционного усилителя в выбранный диапазон.

Одновременно со второго выхода реверсивного счетчика 6 на первый вход второго цифрового сумматора 5 поступает код коррекции порядка выходного числа.

На выходе первого цифрового сумматора 1 вырабатывается код в соответствии с математическим выражением

1 -.=Х +3 -z

Этот код поступает на второй вход второго цифрового сумматора 5, ko»

l Ф торый на выходе вырабатывает цифровой код в соответствии с выражением мд - LJ, ) - Е. +- 1и, 3 1011622 4 где К " выходной цифровой код множи- первого 1 и второго 5 цифровых сум

МЫу тельно-делительного устрои- маторов выгодно отличает множительно -.

v ства", делительное устройство от прототипа„

tn цифровой код корреляции выход так как уменьшается влияние разности ного кода множительно-дели- у входных токов и напряжения .смещения тельного устройства с учетом усилителей на точность работы устройзнака. ства за счет того, что входные сигнаИспользование новых элементов цифро- лы лежат в выбранном диапазоне управляемой проводимости 3 обратной . Применение гибридного лредставсвязи операционного усилителя 4, ком- 1в ления числа расширяет динамический паратора 7, реверсивного счетчика 6, диапазон его изменения.

1 X4

Jg

2ц хе и

Составитель В.Жирнова

Редактор Л.Повхан Техред А.Бабинец Корректор В,Гирняк е ааа а ° » е ее е е е е ее а еааеееаееееаа

Заказ 2678)29 Тираж 382 Подписное

ВНИИПИ «„осударственного комитета СССР по делам изобретений и бткрытий

113035, Москва, Ж-35, Рауаская неб., д. 4/5 а а еа ww wþ v

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4