Устройство для записи информации

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ЗАПИСИ ИНФОРМАЦИИ, содержвшее блок синхронизалив , подкпючевяый Куствновочвойу входу делителя, модуляторы, выходы котих: рых соединены через элемент ИЛИ с счвт . ным входом делителя, один из выходов которого соединен с головкой записи, о гличаюшееся тем, что, с целью повышения достоверноств воспровэведения по отдельным каналам, в него введет дешифратор, вкоды которого со€Шн нены с другими выходами делителя, a . выход - с входами управления модулято рами.

СООЗ СОВЕТС (W@Wlgl

РЕСПУБЛИК

Э ц -Й 11 В 5/04

ГОСУДАРСТНЕННЬЙ КОМИТЕТ СССР ПО ДКЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ.(21) 3345387/1Ъ-10 (22) 08.10.81 (46) 15.04.83. Бюп. Щ 14 (72) Г. М. Павлов и К. Е. Чуприн (53) 681.84.001.:2 (088.8) (56) 1. Авторское свидетельство СССР

М 354454, кл.C 11 В 5/02, 1970.

2. Авторское свидетельство СССР

М 870085, кл.G 11 В 5/04, 1977. (прототип) . .: (54) (57) УСТРОЙСТВО ДЛЯ ЗАПИСИ

:HHCOPNAUHH, содержащее блок синхроS

„SU„„j 0123

I низапии, подключенный к установочноМу входу делителя, модуляторы, выходы которых соединены через элемент ИЛИ с c . иым входом делителя, один из выходов которого соединен с головкой записи, о rличающееся тем, что,с пелью повышения достоверности воспроизведения по отдельным каналам, в нж о введен дешифратор, входы ксеорого соедннены с другими выходами делителя, а выход - с входами управления модуляторами е

1012334

Изобретение относится к приборостроению, а именно к многоканальным устройствам для записи с частотной модуляцией.

Известно устройство для магнитной записи, содержащее схему И, блок синхронизации, частотные модуляторы, - выходы которых подклточены к блоку зтктиси P1) .

Недостатками этого устройства яв=

, ляются ограниченное число регистрируе мых каналов, невозможность изменения времени подключения каждого канала в суммарном времени подключения всех каналов.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее блок синхронизации, двухвходовую схему И, модуляторы, между.выходом и шиной управления каждого из которых подключена цепь из первого триггера, счетный ттход которого соединен с выходом модулятора, дифференцируюптего звена, вход которого соединен с выходом первого триггера и второго триггера с раздельными входами, выход которого псдюпочен к шине управления . модулятора, установочные входы всех триг геров. всех цепей соединены с выходом бпока синхронизации, а раздельные вхо- З0 ды вторых триттеров всех цепей соединены в кольцо, так, что первый из раздельных входов второго триггера каждой цепи, выход дифференцируюшего звена этоЯ же цепи и второй из раздельных входов З5 второго триггера соседней, по напряжению

:обхода кольца, цепи соединены вместе и, ! кроме того, выход и один из входов двухвходовой схемы И включены в разрыв шины управления одного из модуляторов, 0 а второй иэ входов схемы И потткпючей( к выходу 6noza синхронизации P2 ) .

Увеличение числа регистрируемых каналов без расширения полосы частот значительно усложняет устройство, кроме 45 этого, запись за сумморное время цодклю-, чения всех каналов только четырех перепадов импульсного сигнала модулятора каждого канала ограничивает функциональные воэможнюс ти устройства.

Белью изобретения является повышение достоверности воспроизведения по отдельным каналам.

Цель достигается тем, что s устройств ве, содержащее блок синхронизации под55 ключенный к установочному входу делителя модуляторы выходы zm отжх соединены через элемент ИЛИ со счетным ттхoдом делителя, один из выходов которого соединен с головкой записи, введен дешифратор, входы которого соединены с друл4ми выходами делителя, а выходы— с входами управления модуляторами.

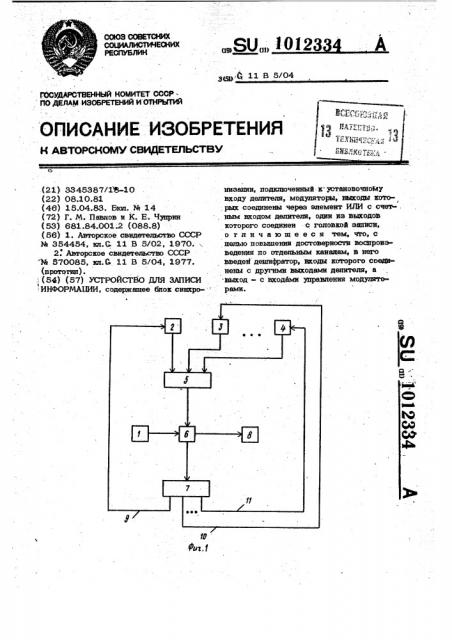

На фиг. изображена структурная схема предлагаемого устройства; на фиг. 2временные- диаграммы сигналов.

Устройство (см. фиг. 1) содержит блок 1 сихронизации, частотные модуляторы 2,3 и 4, схему ИЛИ 5, делитель

6, дешифратор 7, головку записи 8, причем дешифратор имеет выходы 9, 10 и

11.

Блок 1синхронизации подключен к установочному входу делителя 5, счетный вход делителя 6 через элемент ИЛИ 5 подютючен к выходам частотных модулятоpos .2,3 и 4 выходы разрядов делителя

6 подключены к входам дешифратора 7, выход первого разряда делителя 6 подключен к головке записи 8, а выходы 9, 10 и 11 дешифратора 7 подключены к входам управления каждым частотным модулятором 2,3 и 4.

На фиг. 2 введены следуккцтте обозначения: сигнал 12 на выходе модулятора

2; сигнал 13 на вькоде модулятора 3; сигнал 14 на выходе модулятора 4; сигнал 15 на выходе 9 дешифратора 7; сигнал 16 на выходе 10 дешифратора 7;. сигнал 17 на выходе 11 дешифратора 7; сигнал 18 на выходе элемента ИЛИ 5; сигнал 19 на выходе первого разряда делителя 6; суммарное время Т. подключения модуляторов 2,3 и 4; время Т2 подключения модулятора 2; время Т подт кпючения модулятора 3; время Т подключения модулятора 4.

Устройство работает следуютцим образом.

При включении питания блок-1 синхронизации устанавливает делитель 6 в исходное положение, выходы разрядов делителя 6 подключены к входам дешифратора 7, на выходе 9 дешифратора 7 форми руется сигнал (поз. 15, фиг. 2) разрешения работы частотного модулятора 2.

Модулятор 2 вырабатывает импульсный сигнал (поэ. 12 фит . 2) частота которого промодулирована регистрируемым сигналом первого канала. Перепады импульсного сигнала через схему ИЛИ-5 поступают на счетный вход делителя 6, после записи необходимого чттола импульсов в делтттель 6 на выходе 9 дешифратора

7 формируется сигнал запрета работы частотного модулятора 2 (поз. 15, фиг. 2) и разрешения работы частотного модулятора 3 (поэ. 16, фиг. 2), Моду1012334

Фиг.2

ВНИИПИ Заказ 2776/64 Тираж 592: Подписное

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

3 лятор 3 вырабатывает импульсный сщ» нал, частота которого промодулирована регистрируемым сигналом второго кана, ла (поз 13, фиг. 2). Перепады импульсного напряжения через элемент ИЛИ 4 поступак г на счетный вход делителя 6, после записи необходимого числа импуль= сов в делитель 6, на выходе 10 дешифратора 7 формируется сигнал (поэ. 16, фнг. 2) запрета работы частотного модулятора 3 и разрешение для работы следукщего канала (мпдулятор 4, вькод

11 дешифратора 7, поз 17, фиг. 2) и так далее цо кольцевой схеме. Сигнал (поз. 19, фиг. 2) с выхода первого разряда делителя 6, поделенный по частоте в два раза для увеличения плотности за. писи, поступает в головку 8 записи.

Изменяя > диагРамму формирования сигналов на выходах 9, 10 и 11 дешифратора 7 в зависимости от частотного диапазона регистрируемых сигналов каждого канала, можно изменить число записьЖаемьас периодов несушей частоты ре,гистрируемого сигнала любого. канала за суммарное время 1 подключения Bc8r, 1 каналов и тем самым повысить достоверность воспроизведения по отдельным каналам по сравнению с прототипом, который являеп:я и базовым объектом, при этом исключение счетного триггера, дифференцирукпцей цепочки, статического триггера, элемента И значительно упростило устройство.

Испытания предложенного устройства с записью сигналов по трем каналам, при записи по третьему каналу восьми пере-, падов напряжения, а по второму каналу и первому каналу по четыре перепада напряжения, увеличивают достоверность записи высокочастотного регистрируемого сигнала по третьему каналу на

23%р по сравнению с базовым устрой -т вом.

Предлагаемое устройство может найти широкое применение в тех случаях, когда требуется получить высокую достоверность записи информации по одному или несколькиж каналам.