Накапливающий сумматор

Иллюстрации

Показать всеРеферат

союз советсних социАлистичесних

РЕСГ)УБЛИН (19) (11) З(Я) 0 06 Р 7/50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ госудм ственный номитет ссср по делАм изОБРетений и отнрытий (21) 3377578/18-24 (22) 29.12.81 (46) 23.04..83. Бюл. В 15 (72) A.A.Ñîðîêèí, A.A.Ñåëèâàíoâ., В.В.Румянцев и Л.A.Кондес (53) 681.325.5(088.8) (56) 1. Авторское свидетельство СССР

В 703810, кл. С 06 Г 7/50, 1977.

2. Авторское свидетельство. СССР

9 557362, кл. G 06 P 7/50, 1976 (прототип). (54)(57) НАКАПЛИВА(ощИЯ СуИ1щтОР, содержащий в каждом разряде триггер, два элемента И и элемент ИЛИ, причем первый вход первого элемен-. та И соединен с входом накапливающего сумматора, а прямой выход триггера соединен с выходом суммы ,накапливающего сумматора, о т— л и ч а ю шийся тем, что, с. целью расширения функциональных возможностей путем осуществления операции вычитания, он содержит s каждом разряде два сумматора по.модулю два, причем счетный вход триггера соединен с шиной считывания накапливающего сумматора, а управляющий вход - с выходом первого сумматора по модулю два и первым входом второго элемента И, первый вход первого сумматора по модулю два соединен с первым входом первого элемента И, . а второй вход - с вторым входом первого элемента И и входом переноса (заема) накапливающего сумматора, инверсный выход триггера соединен с первым входом второго сумматора по модулю два, второй вход которого соединен с управляющей .шиной накапливающего сумматора, а выход под- g ключен к второму входу второго эле". мента И, выход которого подключен к первому входу элемента ИЛИ, второй вход которого соединен с выхб- С дом первого элемента И, выход элемента ИЛИ соединен с выходом переноса, (заема) накапливающего.сумматора. !

1013947

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах и в цифровых системах сбора и обработки информации.

Известен накапливающий сумматор, содержащий в каждом разряде триггер и элементы И, ИЛИ, И-НЕ (1 ).

Недостатком его являются ограниченные функциональные возможности, выражающиеся в невозможности выпол- 10 нения операции вычитания.

Известен также накапливающий сумматор, содержащий в каждом разряде триггер, два элемента И, два элемента ИЛИ и элемент НЕ (2 j. 15

Недостатком известного устройства является его функциональная ограни- . ченность, заключающаяся в невозможности выполнения операции вычитания.

Целью изобретения является расширение функциональных воэможностей, заключающихся в выполнении операции вычитания чисел, представленных в прямых кодах.

Указанная цель достигается тем, что накапливающий сумматор, содержащий в каждом разряде триггер, два элемента И и элемент ИЛИ, причем первый вход первого элемента И соединен со входом накапливающего сумматора, а прямой выход триггера соединен с выходом суммы накапливающего сумматора, содержит в каждом разряде два сумматора по модулю два, причем счетный вход триг- 35 гера соединен с шиной считывания накапливающего сумматора, а управля ющий вход — с выходом первого сумматора по модулю два и с первым входом второго элемента И, первый вход пер- 40 вого сумматора по модулю два соединен с первым входом первого элемента И, а второй вход - co вторым входом первого элемента И и входом переноса (заема) накапливающего сумма- 45 тора, инверсный выход триггера соединен с первым входом второго сумматора по модулю два, второй вход которого соединен с управляющей шиной накапливающего сумматора, а выход подключен ко второму входу второго элемента И, выход которого подключен к первому входу элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, выход элемента ИЛИ соединен с выходом перено- 55 са (заема) накапливающего сумматора.

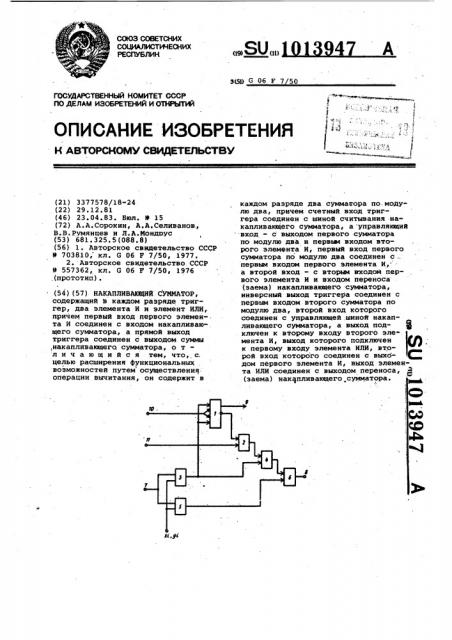

На чертеже представлена функциональная схема i-го разряда накапливающего сумматора.

Каждый разряд сумматора содержит . 60 счетный триггер 1, два сумматора по модулю два 2 и 3, два элемента И 4 и 5„ элемент ИЛИ б, вход 7 переноса (заема) из предыдущего млад.шего разряда, выход (шину) 8 пере- 65 носа (заема) данного разряда, выход (шину) 9 суммы, шину 10 считывания, управляющую шину 11 (управления операцией сложение-вычитание), вход (шину) 12 ввода i-го разряда числа.

Устройство работает следующим образом.

Каждый i-й разряд первого слагаемого или уменьшаемого X(X.„,X2,..., Хд) поступает на шину 12 соответст- вующего разряда сумматора. При этом на шину 11 подается потенциал логическая единица, соответствующий операции сложения. Через промежуток времени, равный или больше времени задержки информации, на сумматор по модулю два 3 по шине 10 всех разрядов одновременно поступает импульс считывания и число X записывается в триггерах 1 сумматора. Затем на шину 11 соответствующих разрядов сумматора поступает код второго слагаеМого или вычитаемого Y(Y„,Y>,..., Y„). При этом при операции сложения на -управщчющей шине 11 сохра- няется потенциал логическая единица, а при операции вычитания на ,шину 11 подается потенциал логический нуль . Далее по шине 10 поступает импульс считывания и триггеры 1 сумматора устанавливаются в состояние, соответствующее сумме или разности чисел Х и Y.

Работа i-го разряда сумматора в режиме вычитания, при котором на шину 11 подан потенциал логический нуль, поступающий на первый вход сумматора по модулю два 2 осуществляется следующим образом.

Если при подаче на вход 1-го разряда Y; = 1 по шине 7 поступает сигнал заема Е,-, = 1 из предыдущего разряда, то при совпадении двух сигналов на входе сумматора по модулю два 3 на его выходе формируется,дотенциал логический нуль, который поступает на управляющий вход триггера 1. Одновременно на выходе эле- . мента И 5 формируется потенциал логическая единица, который через элемент ИЛИ б пд шине 8 как единица заема Z. =1 распространяется в сторо1 ну старшего разряда. На поступление по шине 9 считывающего импульса триггер 1 не реагирует и сохраняет свое

1 .состояние. Если на вход i-го разФ ряда поступают сигналы Z1> =0 и

Y. =1 или Z- =1 и Y.= О, то на

i 1-1 1 выходе сумматора по модулю два 3 формируетсй потенциал логическая единица, который поступает на управляющий вход триггера 1 и на первый вход элемента И 4, Если триггер 1 находится в единичном (нулевом)состоянии, то с его инверсного выхода на второй вход сумматора по модулю два 3 поступает потенциал логический нуль (логическая едини1013947

Составитель А.Степанов

Редактор Н.Егорова Техред M.ÊîøòóÐà Корректор M. Шароши

Заказ 3018/57 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР.по делам изобретений и открытий

113035, Москва, Ж-35, Раушская.наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 ца ) н на его выходе формируется потенциал, . логический нуль (логическая единица ), который поступает на второй вход элемента И 4. При несовпадении (совпадении) двух логических единиц на входе элемента

И 4 на его выходе формируется потенциал логический нуль (логическая единица ) и на шине 8 формируется сигнал заема 2 =0(Z ° =1). При поступi ленин по шине iO счетного импульса триггер 1 переключается в противоположное состояние.

Если на вход i-ro разряда поступают сигналы Z =O и Y-=.Î, то на выходе сумматора по модулю два 3 15 формируется потенциал логический нуль . При этом по шине 8 распространяется сигнал Б.=О, но

1= триггер 1 реагирует на поступление счетного импульса по шине 10 и 20 сохраняет свое состояние.

Работа i-го разряда сумматора в режиме сложения, при котором на шину ll пОдан потенциал логическая единица, отличается от режима вычитания только тем, что при поступлении на вход сигнала переноса

П«1--О и Y = 1 или П- =1 и

1- 1 1-1

)((=О, если триггер l находится в единичном (нулевом) состоянии, на выходе сумматора по модулю два 2 формируется потенциал логическая единица (логический нуль), который поступает на вход элемента Й 4. При совпадении (несовпадении) двух. логических единиц на входе элемента

И 4 на его выходе формируется сигнал логическая единица (логический нуль ) и на шине 8 формируется сигнал переноса П = 1 (П-=О).При поступлении по шине 10 сиетйого импульса триггер 1 переключается в противоположное состояние.

Как при операции сложения, так и при операции вычитания числа поступают на входы сумматора в прямых кодах и результирукицее число получается также в прямом коде.

Предлагаемое устройство выгодно отличается от известного тем, что имея несложную схему (количество логических элементов и связей между ними не более, чем у известного), позволяет производить как операции сложения, так и операции вычитания чисел, представленных в прямых кодах. Эта особенность позволяет расширить область применения накапливалацего сумматора.