Генератор псевдослучайной последовательности

Иллюстрации

Показать всеРеферат

ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОС П1, содержащий гене ратор тактовых импульсов, счетчик., сумматор по модулю два, выход которого соединен о информационным входом блока памяти, о т л и чаю г щи и с я тем, что, с целью расширения функодюнальных возможностей генератора обеспечения изменения статистических характеристик формируемой последовательности, он содержит коммутатор, паралдель иЫ1й сумматор,, два D-триггера, Т-триггер два 31лемента И и элемент ИЛИ, выход которого соединен с управляю1цим вхо дом блока памяти, вiыxoд которого соединен с D-входами D-триггеров, выходы которых соединены с входами сумматора по модулю два соответственно , выходгенератора тактовых импульсов соединен с входом Т-триггера и с первыми входами первого и второго элементов И выходы которых соединены с С-входами соотвеТствуняцих D-триггеров, прямой выход Т-триггера соединен с управлякицим входом коммутатора, с первым входом элемента ИЛИ и с вторьйвходом перг вого элемента И, выход которого соединен со счетным входом счетчика, разрйдные .выходы которого соединены, с первой группой входов параллельного сумматора соответственно, выходы которого соединены с соответствщ)адами адресны

СОЮЗ СОВЕТСКИХ

О ° Ю

РЕСПУБЛИК

3(Д) G. 06 F. 7/58

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМЪГ СВИДЕТЕЛЬСТВУ

4©

gal. (21) 3367046/18-24 (22) 11.12.81 (46) 23.04. 83. Вюл. У 15 (72) A.М. Водовозов и -B.Í. Лабичев (71) .Вологодский политехнический институт (53) 681.325(088. 8) (56) 1. Авторское свидетельство СССР

9 524175, кл. 6 06 F 7/58, 1975.

2. Авторское свидетельство СССР по заявке В 3243239/18-24, кл. G 06 F 7/58, 1981 (прототип). (54) (57) EHRPATOP ПСЕВДОСЛУЧАЙНОЙ

ПОСЛЕДОВАТЕЛЬНОСТИ, содержащий гене- ратор тактовых импульсов, счетчик, сумматор по мсщулю два, выход которого соединен с-информационным входом блока памяти, о т л и ч à ю шийся тем, что, с. целью расши« рения функцдональных возможностей генератора путем обеспечения изменения статистических характеристик: формируемой последовательности, .он содержит коммутатор, параллельный сумматор, два D-триггера, Т-триггер, два элемента И и элемент ИЛИ, выход которого соединен с управляющим вхо дом .блока памяти, выход которого

„„SU„„1013954. A соединен с D-входами Р-триггеров, выходы которых соединены с входами сумматора по модулю два соответственно, выход4генератора тактовых импульсов соединен с входом T-триггера и с первымн входами первого и второго элементов И,- выходы кото-. рых соединены с С-входами соответствующих Р-триггеров, прямой выход

Т-триггера соединен с управляющим входом коммутатора, с первым входом элемента ИЛИ и с вторым входом пер; ного элемента И, выход которого соединен со счетным входом счетчика,- разрядные, выходы которого соединены, с первой группой входов параллельного сумматора соответственно, выходы ® которого соединены с соответствующими адресныМи входами блока паыя-. ти, инверсный выход Т-триггера сое- уиив динен с вторым входом второго эле- % мента И, выход которого соединен с вторым входом элемента ИЛИ, выход . Я второго 3-триггера является выхбдом генератора, группой входов которо- фа го является группа входов коммута-. тора, группа выходов которого сое- аю динена с второй группой входов па- )weak раллельного сумматора;соответственно. .

1013954

Изобретение относится к вычислительной технике и может быть использовано для решения вероятностных задач методом моделирования. .Известен .генератор псевдослучайной последовательности двоичных чисел, содержащий регистр сдвига с сумматором по модулю 2 в цепи обратной. связи, генератор тактовых импульсов, выход которого соединен со входом регистра сдвига, а также счетчик и блок сумматоров 11 .

Недостатком данного устройства является малое значение периода псевдослучайной последовательности, ог-раниченное разрядностью регистра сдвига. Увеличение периода последовательности за счет разрядности регистра приводит к усложнению схемы и снижению ее надежности.

Наиболее близким .по техническому 20 решению к изобретению является генератор псевдослучайной последовательности, содержащий тактовый генератор, счетчик импульсов, блок памяти и сумматор по модулю 2. В данной 25 схеме работа, выполняемая блоком памяти, аналогична работе многоразрядного регистра сдвига. 3а счет увеличения объема памяти длина генерируемой последовательности уве- 30 личивается без значительного усложнения схемы 12 .

Недостатком известного устройства является сложность изменения характеристик генерируемой псевдослучайной последовательности. Изменение последовательности возможно .эа счет изменения временного сдвига между сигналами на входах сумматора по модулю 2 путем увеличения или уменьшения разрядности регистра сдвига. Однако это приводит к изменению общего числа разрядов генератора и связано со значительным изменением схемы.

Цель изобретения - расширение функционирования возможностей генератора за счет обеспечения изменения характеристик формируемой последовательности. 50

Для достижения поставленной цели в генератор псевдослучайной пос ледовательности, содержащий генератор тактовых импульсов, счетчик, сумматор по модулю два, выход которого соединен с информационным входом блока памяти, введены коммутатор, параллельный сумматор, два

D-триггера, Т-триггер, два элемента И и элемент ИЛИ, выход которого соединен с управляющим входом бло- . 60 ка памяти, выход которого соединен с D-входами D-триггеров, выходы которых соединены со входами сумматора по модулю два соответственно, выход генератора .тактовых импульсов Я соединен со входом T-триггера и с первыми входами первого и второго элементов И, выходы которых соединены с С-входами соответствующих

D-триггеров, прямой выход T-триггера соединен с управляющим входом коммутатора, с первым входом элемента ИЛИ и со вторым входом первого элемента И, выход которого соединен со счетным входом счетчика, разрядные выходы которого соединены с первой группой входов параллельного сумматора соответственно, выходы которого соединены с соответствующими адресными входами блока памяти, инверсный выход Т-триггера соединен со вторым входом второго элемента И, выход которого соединен со вторым входом элемента ИЛИ, выход второго D-триггера является выходом генератора, группой входов которого является группа входов коммутатора, группа выходов которого соединена со второй группой входов параллельного сумМатора соответственно.

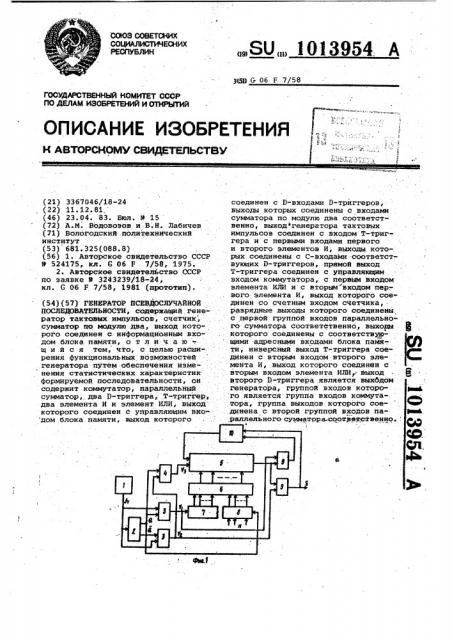

На фиг. 1 дана блок-..схема генератора; на фиг. 2 — диаграмма его работы.

Генератор псевдослучайной последовательности содержит генератор 1 тактовых импульсов, T-триггер 2, элементы И 3, элемент ИЛИ 4, блок 5 памяти, параллельный сумматор 6, счетчик 7, коммутатор 8, D-триггеры 9 и сумматор 10 по модулю два.

Генератор работает следующим образом.

Сигнал f с выхода генератора 1 поступает на вход триггера 2 и элементы И 3. На прямом и инверсном выходах триггера 2 формируются сигналы Я и 5 формы меандр (фиг. 2), а на выходах элементов И 3 — несовпадающие последовательности импульсов Vq, и V (фиг. 2) с частотой К

Каждый импульс сигнала V, поступающий на вход счетчика 7, увеличивается на код М на его разрядных выходах, соединенных со входами первого слагаемого параллельного сумматора 6.

При Состоянии Q = 1 коммутатором

8 подключается ко всем входам второго слагаемого кодовый сигнал логического нуля. Сумматор 6 формирует на адресных шинах блока памяти 5 код М, определяющий адрес опрашиваемой ячейки памяти. Элемент ИЛИ, формирующий сигнал Ч5 = Q q V<, воздействуя на вход управления режимом работы блока 5 памяти, устанавливает блок памяти в режим считывания, и в первый D-триггер 9 сигналом переписывается содержимое ячейки памяти с адресом N. С приходом следующего импульса f триггер

2 переходит в состояние Я = О, ком-:=А

---1013954. Фиг.2

Составитель A Карасов

Редактор Н. Егорова Техред К.Мыцьо Корректор С. Шекмар

Заказ 3006/58 Тираж 704 Подписное

ВНИИПИ Государственого комитета СССР по делам изобретений и открытий

113035, Москва, X(-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 мутатор 8 подключает ко входам втс — цого слагаемого сумматора б управ- . ляющий кодовый сигнал N. Сумматор

6 формирует на адресных шинах блока 5 памяти,- работающего по-прежнему в режиме считывания, код М + И, и во второй D-триггер 9 сигналом переписывается содержимое ячейки памяти M + N, На входах сумматора по модулю 2 формируется двоичное чис- . ло, определяемое состоянием D-триггеров 9. По окончании импульса V на выходе элемента ИЛИ 4 формируется сигнал V> = 0; блок 5 памяти переводится в режим записи, происходит запись числа с выхода суммато-ра по модулю 2 в ячейку памяти .с номером M + N.

Во время работы счетчик 7 прохо-. дит все К своих возможных состояний, число которых равно объему памяти . блока 5 памяти, и число, записанное в каждую i-ячейку памяти, считывается на вход первого D-триггера 9 чеI уез К вЂ” N периодов сигнала V<, а на вход второго D-триггера 9 - через .

К периодов. В результате работа, выполняемая блоком 5 памяти, аналогична работе К-разрядного регистра сдвига, охваченного обратной связью через сумматор по модулю 2, подключенный своими входами к последнему (k-му),. и К - N-му разрядам регист- . ра. 3а счет изменения регулирующей кодовой комбинации на входах коммутатора 8 может быть изменен номер разряда эквивалентного регистра сдвига, к которому подключен полусумматор.

Таким образом, генератор псевдослучайной последовательности позволяет получить все возможные последовательности при выбранном объеме па20 мяти. При этом изменение длины генерируемой последовательности не свя-. . зано с изменением схемы устройства и увеличением аппаратурных затрат.