Устройство для определения четности информации

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЧЕТНОСТИ ИНФОРМАЦИИ, содержащее регистр , первый и второй элемент ИЛИ, первый и второй элементы задержки, первый, второй, третий, четвертый . и пятый элементы И, группу пар элементов И, первый второй и третий триггеры, причем выход первого элемента ИЛИ соединен со счетным вхо дом первого триггера, единичный и ;нулевой выходы которого соединены с первыми входами первого и второго . элементов И, разрядные входы регистра являются входами устройства и соединены с группой входов второго элемента или, выход которого соединен с единичным входом второго триггера и через первый элемент задержки с первым входом третьего элемента И выходы первого и второго элементов И являются выходами устройства и соединены с входами третьего элемента ИЛИ., выход которого соединен с нулевым входом первого триггера и нулевым входом второго триггера, еди .ничный выход которого соединен с втоpbGM ВХОДОМ третьего элементга И,выхрд третьего элемента И соединен с входом второго элемента ИЛИ и с первыми входами четвертого и пятого элементов И, выход четвертого элемента И через второй элемент задержки соединен с единичным входом третьего триггера, . нулевой и единичный выходад которого соединены соответственно с вторь1ми входами четвертого и пятого, элементов И, выход пятого элемента И соединен с первыми входами первой пары элемен .тов И группы, выход первого и второго элементов И каждой пары группы, соединены соответственно с соответствующим входом первого элемента ИЛИ и первьши входами хшедующей пары элементов И группы единичный и нулевые выг ходы каждого счетного триггера регистра , начиная с третьего, соединены с вторыми входами соответствующей пары элементов И группы, о т л ич а ю щ еес я тем, чт.о, с целью повышения быстродействия и упрощения устройства, введена дополнительная пара элементов И и группа элементов И, причем выход четвертого элемента О) ,И соединен с первыми входсши элементов И дополнительной пары и с первыми входами элементов И группы, единичный выход первого и нулевой выход второго триггеров регистра сое-; динены с вторым и третьим входом первого элемента И дополнительной пары, нулевой выход первого и единичный выход второго триггеров регистра соединены соответственно с вторым и третьим входами второго элемента И дополнительной пары, вы00 ходы пары дополнительных элементов . со сд И соединены с соответствующими входа ми первого элемента ИЛИ, единичные выходы четных триггеров регистра, о начиная с четвертого, соединены с вторыми входами -соответствующих элементов И группы, выход каждого элемента И группы соединен со счетным входом каждого нечетного триггерарегистра , начиная с третьего, выход третьего элемента ИЛИ соединен с нулевым входом третьего триггера и нулевыми входами первого и всех четных триггеров регистра, выход первого элемента И каждой пары группы соединен сГнулевым.. входом соответстЪующего триггера регистра.

СОКИ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ . РЕСПУБЛИК (5 ) 6 06 F 11/10

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

1..ii".,-..".=с» i: з."

ЬЬс М«м 4 а; ь Л

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ (21)3383730/18-24 (22)13.11.81 (46)23.04,83, Бюл. м 15 (72) Н. Ф, Морозов и В. Д. Трусов . (71)Институт технической кибернетики

AH Белорусской CCP (53)681,3(088.8) (56)1. Авторское свидетельство СССР

Р 746530, кл. G. 06 F 11/10, 1978, 2, Авторское свидетельство СССР

9 767765, кл.G 06 F 11/08, 1978 (прототип), (54)(57) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ

ЧЕТНОСТИ ИНФОРМАЦИИ, содержащее регистр, первый и второй элемент ИЛИ, первый и второй элементы задержки, первый; второй, третий, четвертый и пятый элементы И, группу пар элементов И, первый второй и третий триггеры, причем выход первого элемента ИЛЙ соединен со счетным вхо-, дом первого триггера, единичный и нулевой выходы которого соединены с первыми входами первого и второго . элементов И, разрядные входы регистра являются входами устройства и соединены с группой входов второго элемента ИЛИ, выход которого соединен с единичным входом второго триггера и через первый элемент задержки — с первым входом третьего элемента И> выходы первого и второго элементов

И являются выходами устройства и соединены с входами третьего элемента

ИЛИ, выход которого .соединен с нулевым входом первого триггера и ну-. левым входом второго триггера, еди.ничный выход которого соединен с вторым входом третьего элемента И, выход третьего элемента И соединен с входом второго элемента ИЛИ и с первыми входами четвертого и пятого элементов

И, выход четвертого элемента И через второй элемент задержки соединен с единичным входом третьего триггера, нулевой и единичный выходы которого соединены соответственно с вторыми

„„SU „„1013959 А входами четвертого и пятого элементов

И, выход пятого элемента И соединен с первыми входами первой пары элементов И группы, выход первого и второго элементов И каждой пары группы соединены соответственно с соответствующим входом первого элемента HJJH и пер-. выми входами .следующей пары элементов И группы, единичный и нулевые выходы каждого счетного триггера регистра, начиная с третьего, соединены с вторыми входами соответствующей пары элементов И группы, о т л ич а ю щ е е с я тем, что, с целью повышения быстродействия и упрощения устройства, введена дополнительная пара элементов И и группа элементов Я

И, причем выход четвертого элемента ,И соединен с первыми входами элементов И дополнительной пары и с первыми входами элементов И группы, еди- 5ц ничный выход первого и нулевой выход второго триггеров регистра сое- р динены с вторым и третьим входом первого элемента И дополнительной пары, нулевой выход. первого и еди- ° ничный выход второго триггеров ре-. гистра соединены соответственно с 4» вторым и третьим входами второго элемента И дополнительной пары, выходы пары дополнительных элементов . 1э Ю

И соединены с соответствующими входа Q ми первого элемента ИЛИ, единичные выходы четных триггеров регистра, начиная с четвертого, соединены .с { ф . вторыми входами .соответствующих элементов И группы, выход каждого эле1 мента И группы соединен со.счетным входом каждого нечетного триггера. регистра, начиная с третьего,- выход третьего элемента ИЛИ соединен с нулевым входом третьего триггера и нулевыми входами первого и всех четных триггеров регистра, выход первого элемента И каждой пары группы соединен с: нулевым . входом соответ-, ствующего триггера регистра.

1813959

Изобретение относится к вычислительной технике и может использоваться для обнаружеНия ошибок нечетной кратности при передаче и хранении данных в двоичном коде, Известно устройство для контроля четности информации, содержащее триггер, два элемента И, регистр сдвига, группу элементов ИЛИ, число которых равно полонине количества разрядов контролируемого кода, группу двухвходовых элементов И, группу трехвходовых элементов ИЛИ и элемент задержки P1).

Недостатком устройства является

; очень низкое быстродействие, Наиболее близким по технической

t сущности к предлагаемому является асинхронное устройство для определения четности информации, содержащее регистр, разрядные входы которого 20 являются входами устройства, эле, мент ИЛИ, выходом соединенный со счетным входом триггера, выходы которого соединены с первыми выходами двух элементов И, выходы которых 25 являются выходами устройства, второй

-и третий элементы ИЛИ, элементы И, второй триггер и элемент задержки, причем входы устройства соединены со входами второго элемента ИЛИ, 30 выход которого соединен со входом элемента задержки и с установочным входом второго триггера, единичный выход которого и выход элемента задержки соединены со входами третьего 35

I элемента И, выход которого соединен с одним из входов второго элемента

ИЛИ и с первыми входами дополнительных элементов И, вторые входы которых соединены с выходами дополнитель-@ ного триггера, установочный вход которого соединен.с выходом порогового блока, входами соединенного со входами устройства, а вход сброса — с выходом дополнительного элемента задержки, входом подсоединенного к выходу первого дополнительного элемента

И и к объединенным вторым входам дополнительных элементов ИЛИ, к выходам которых подключены счетные входы триггеров регистра, причем перные и третьи. входы дополнительных элементов ИЛИ соответственно подключены к входам первого и второго элементов ИЛИ, выход второго дополнительного элемента И подключен к первым входам четвертого и пятого элементов

И, вторые входы которых соединены с выходами первого разряда регистра, выходы пятого и.последующих нечетных элементов И соединены с первыми вхо- бО дами днух последующих элементов И, вторые входы которых соединены с выходами следующего разряда регистра, выходы четвертого и последующих четных элементов И соединены со входами первого элемента HJIH выход последнего нечетного элемента И соединен с входами первых двух элементов И, выходы которых соединены со входами третьего элемента ИЛИ, выход которого соединен со входами сброса первого и второго триггеров g2).

Недостатками устройства являются большой объем оборудования вследствие применения достаточно сложно- го порогового блока, особенно при большой разрядности контролируемого кода, и необходимость применения по два двухвходовых элементов И на каждый разряд регистра, а также невысокое быстродействие, обусловленное тем, что последовательно анализируются все и разрядов регистра, Целью изобретения является упрощение устройства и увеличение его быстродействия за счет сокращения вдвое длины анализируемого кода путем предварительного попарного суммирования по модулю 2 содержимого соседних разрядов.„и совмещения по времени опроса первых двух разрядов с суммированием в.остальных, Поставленная цель достигается тем, что в устройство для определения четности информации, содержащее регистр, первый и второй элементы ИЛИ, первый и второй элементы задержки, первый, второй, третий, четвертый и пятый элементы И, группу пар элементов И, первый, второй и третий триггеры, причем выход первого элемента ИЛЙ соединен со счетным входом первого триггера, единичный и нулевой вы-. ходы которого соединены с первыми входами первого и второго элементов

И, разрядные входы регистра являются входами устройства и соединены с группой входов второго элемента

ИЛИ, выход которого соединен с единичным входом второго триггера и через первый элемент задержки — с первым нходом третьего элемента И, выходы первого и нторого элементов И являются выходами устройства и соединены со входами. третьего элемента

ИЛИ, выход которого соединен с нулевым входом первого триггера и нулевым входом второго триггера, единичный выход которого соединен со вторым входом третьего элемента И, выход третьего элемента И соединен со входом второго элемента ИЛИ и с первыми входами четвертого и пятого элементов И, выход четвертого элемента

И через второй элемент задержки соединен с единичным входом третьего триггера, нулевой и единичный выходы которого соединены соответственно со втсрыми входами четвертого и пятого элементов И, выход пятого элемента И соединен с первыми входами первой пары элементов И группы, вы1013959 ход первого и второго элементов И

Каждой пары группы. соединены соответственно с соответствующим входом первого элемента.ИЛИ .и первыми входами следующей пары элементов И группы, единичный и нулевые выходы каждого нечетного триггера регистра, начиная с третьего, соединены со вторыми входами соответствующей пары элементов И группы, введена дополнительная пара элементов И и

10 группа элементов И, причем выход четвертого элемента И соединен с первыми входами элементов И дополнительной пары и с первыми входами элементов И группы, единичный выход первого и нулевой выход второго триггеров регистра соединены со вторыми третьим входом первого элемента И. дополнительной пары, нулевой выход первого и единичный выход второго 20 триггеров регистра соединены соот- . ветственно со вторым и третьим входами второго элемента И дополнительной пары, выходы пары дополнительных элементов И соединены с соответ- 25 ствующими входами первого элемента

ИЛИ, единичные выходы четных триггеров регистра, начиная с четвертого, соединены со вторыми входами соответствующих элементов И группы, выход каждого элемента И группы соединен со счетным входом каждого нечетного триггера регистра, начиная с третьего, выход третьего элемента

ИЛИ соединен с нулевым входом третье-З5 го триггера и нулевыми входами пер-. вого, второго и всех четных тригге-, ров регистра, выход первого элемента

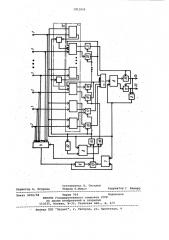

И каждой пары группы соединены с нулевым.-,:.входом соответствующего триггера регистра, На чертеже приведена функциональная схема предлагаемого устройства.

В состав устройства входят информационные входы 1, регистр 2, элементы ИЛИ 3-5, триггеры 6-8, элемен- 45 ты 9 и 10 задержки, элементы И 11-21, группа дополнительных элементов H 22 и выходы 23 и 24, Устройство работает следующим образом. 50

В исходном состоянии триггеры 6-8 и регистр находятся в нулевом со- стоянии. Входная и-разрядная кодовая комбинация поступает в параллель+ ном коде на входы устройства 1 и за- 55 писывается в регистр 2, Одновременно входные импульсы входного кода подаются на элемент ИЛИ 4, С выхода эле" мента ИЛИ 4 импульс, соответствующий моменту записи, поступает на вход элемента задержки 9 и на установочный вход триггера 7. Последний устанавливается в единичное состояние и открывает элемент И 13, Через время- „, соответствующее времени задержки 9, импульс через открытый элемент И 13 поступает на вход элемента ИЛИ 4 и входы элементов И 14 и 15.

Так как триггер 8 первоначально находится в нулевом состоянии, то от-: крыт элемент И 14, поэтому первый импульс пройдет на входы группы дополнительных элементов И и вызовет суммирование по mod 2 содержимого каждой пары соседних:разрядов 2i + 1 и 2i + 2 (для всех И ч.jj qadi ъ 1), причем результат этого суммирования окажется в 2t + 1 разрядах.

Одновременно первый импульс прой,дет через элемент И 16 либо 17, элемент ИЛИ 3 на счетный триггер 6 если значение двух первых разрядов регистра будет "10" либо "01" соот- ветственно, Спустя время д Я с Г.,) с выхода элемента задержки 10 триггер

8 будет установлен в единичное состояние и откроет элемент И 15 для всех последующих импульсов. Второй импульс поступает на элементы И 18 и

19. Если триггер третьего разряда находится в "1", то импульс пройдет через элементы Й 18, ИЛИ 3 на счетный триггер 6 и одновременно.- на вход сброса 3 разряда, К приходу третьего импульса третий разряд триггера будет сброшен и импульс пройдет через элемент И 19. на опрос пятого разряда и т,д, Если же содержимое третьего разряда равно нулю, то уже второй импульс пройдет на опрос пя,того разряда регистра. С выхода последнего элеМента И 21 ймпульс проходит на входы элементов И 11 и 12, Если чйсло единиц в кодовой комбинации яетно, то импульс появится на выходе 23, если нечетно - то на выходе 24, Через элемент ИЛИ 5 любой из этих импульсов проходит на входы сброса триггеров 6-8 первого и всех четных разрядов регистра, Это приводит схему в исходное состояние, Таким образом, изобретение позволит значительно повысить быстродействие и упростить устройство.

1013959

Составитель И, Сигалов

Техред К.Мыцьо Корректор С bley

Редактор Н. Егорова

Филиал ППП "Патент", г. Ужгород, ул, Проектная, 4

Заказ 3006/58 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5