Устройство для спектрального анализа

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ СПЕКТРАЛЬНОГО АНАЛИЗА, содержащее первый и второй блоки памяти, первый умножитель, сумматор и двоичный счетчик, причем вход первого блока naMfltH является информационным входом устройства, вход двоичного счетчика является тактовым входом устройства, о т л и чающееся тем, что, с целью повышения быстродействия и упрощения устройства, оно содержит двоичный счетчик циклов, второй умножитель и блок сравнения, выход которого соединен с входом двоичного счетчика циклов, выход которого подключен к первому входу второго умножителя, выход которого соединен с входом блока сравнения и адресными входами первого и второго блоков памяти, выходы которых подключены соответственно к первому и второму входам первого умножителя, выход которого соединен с входом сумматора, выход которого является выходом устройства, выход младшего разряда двоичного счетчика соединен с входом разрешения второго i умножителя, второй вход которого под (Л ключен к информационному выходу двоичному счетчика, выход переполнения которого соединен с входом двоичного счетчика циклов, а вход второго бгюка памяти является выходом задания коэффициентов устройства. со ч1 1чд

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3369877/18-24 (22) 25.12,81 (46) 23.04.83. Бюл. Н 15 (72) П.М.Чеголин, Н.В.Нечаев, P,Х,Садыхов и А.В,Шаренков (71) Институт технической кибернетики АН Белорусской ССР (53) 681.32(088.8) (56) 1.. Авторское свидетельство СССР

N 532100, кл. G 06 F 15/332, 1976, 2. Авторское CBèäåòeëüñòeo СССР

N 767774, кл. G 06 F 15/332, i980. (54) (57) УСТРОЙСТВО ДЛЯ СПЕКТРАЛЬНОГО АНАЛИЗА, содержащее первый и второй блоки памяти, первый умножитель, сумматор и двоичный счетчик, причем вход первого блока памяти является информационным входом устройства, вход двоичного счетчика является тактовым входом устройства, о т л и:ч а ю щ е е с я тем, что, с целью повышения быстродействия и упрощения

„„SU„„3013972 А з(ю G 06 F 1 /36; G 06 F 1 /332 устройства, оно содержит двоичный счетчик циклов, второй умножитель и блок сравнения, выход которого соединен с входом двоичного счетчика циклов, выход которого подключен к первому входу второго умножителя, выход которого соединен с входом блока сравнения и адресными входами первого и второго блоков памяти, выходы которых подключены соответственно к первому и второму входам первого умножителя, выход которого соединен с входом сумматора, выход которого является выходом устройства, выход младшего разряда двоичного счетчика соединен с входом разрешения второго умножителя, второй вход которого подключен к информационному выходу двоичному счетчика, выход переполнения которого соединен с входом двоичного счетчика циклов, а вход второго блока памяти является выходом задания коэффициентов устройства.

%„() = Ма„(;1, где

10139

Изобретение относится к вычисли" тельной технике и может быть использовано для спектрального анализа случайных процессов.

Известно устройство для вычисле- 5 ния спектра мощности Фурье, содержащее блок вычисления корреляционной функции, сумматор, два переключате" ля, блок памяти, блок вычисления спектра мощности Фурье, счетчик, 10 триггер и соответствующие связи. Устройство обеспечивает вычисление спектра мощности Фурье через корреляционную Функцию (1 ), Однако устройство не позволяет вы" 15 числять спектр мощности Фурье через спектр мощности Уолша, а также обладает низким быстродействием.

Наиболее близким к изобретению по технической сущности является уст- 20 ройство для спектрального анализа, содержащее первый, второй и третий блоки памяти, первый и второй триггеры, сумматор, счетчик, коммутатор, регистр, дешифратор, два блока форми- 25 рования дополнительного кода, блок умножения, элемент И, элемент ИЛИ и соответствующие связи (2 1, Недостатками устройства являются сложность конструкции и низкое быстродействие вследствие большого числа вычислительных операций, Целью изобретения является повышег ние быстродействия (эа счет значительного уменьшения вычислительных < операций) и упрощение устройства.

Поставленная цель достигается тем, что устройство для спектрального анализа, содержащее первый и второй блоки памяти, первый умножитель, сум- 4 матор и двоичный счетчик, причем вход первого блока памяти является информационным входом устройства, вход двоичного счетчика является тактовым входом устройства, содержит двоичный 45

72

2 дом разрешения второго умножителя, второй вход которого подключен к информационному выходу двоичного счет-чика, выход переполнения которого соединен с входом двоичного счетчи. ка циклов, а вход второго блока памяти. является выходом задания коэффициентов устройства.

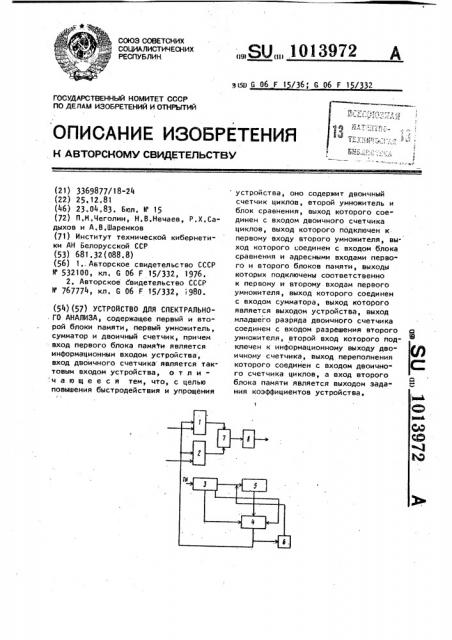

На чертеже приведена блок-схема устройства.

Устройство содержит первый 1 и второй 2 блоки памяти, двоичный счетчик умножитель 4, двоичный счетчик 5 циклов, блок 6 сравнения, умножитель

7, сумматор 8, Вычисление оценки спектральной плотности мощности Фурье основано на использовании существующего матричного соотношения связи между арифметической R>((.) и логической Р (ь) автокор реляцйонными функциями Р (i).

R D "ri„, (1) где 0 - матричный оператор связи.

Умножив(1) слева и справа на матрицу преобразования Фурье, получим

ГР„= F D " P„= s„, (2) где 5< - спектр мощности Фурье.

В свою очередь

P„=% 4„ где И - матрица преобразования Уолша, W - -энергетический спектр мощХ ности Уолша, Тогда, подставляя (3) в (2) имеем х F D W et„(4)

Так как

<<<„(2j-<)=%„(2!); ) = <, «/2- «<=й, =то

0001

0001

000

0 0 0 0 ° 0 ° °

0000

° ° О ° ° °

001 (Ь) счетчик циклов, второи умножитель и блок сравнения, выход которого соединен с входом двоичного счетчика циклов, выход которого подключен к первому входу второго умножителя, выход которого соединен с входом блока срав50 нения и адресными входами первого и второго блоков памяти, выходы которых подключены соответственно к первому и второму входам первого умножителя, выход которого соединен с.входом сум- 55 матора, выход которого является выхо. дом устройства, выход младшего разряда двоичного счетчика соединен с вхоТогда

Sx- FD- а-1ЩФ фщ

1013972 4

2,И 6,4 10 4 4.ц

О

0 Ь, =Ь 14=Ь1 q4= .,2 = 4- (4

+ <(2 2 1/2 - 3 2/4 — 1/2 6(2+ (2/4;

3,6 5,40 11,Щ 1З, g

7/

0 + 1(2 Д2-22/4+ 3/2 1/2+ß /4;

«(4.

Для М=8

1 О .О 0

О 0

0 0

-О О

0 0

0 0

О О

О 1е

Как видно из (7), матрица связи яв-. ляется слабоэаполненной, что позволяет существенно повысить быстродействие спектрального Фурье-анализа при упрощении конструкции устройства, реализующего выражение (6).

В общем виде матрица Ф содержит в каждой i-й строке М/4р ненулевых элементов, если р (М/4, и один элемент, равный 1, если p>:N/4, где р - наи-. . больший общий делитель чисел 1 и М, Ненулевые элементы матрицы Р расположены в столбцах с номерами J 2p+hk

k 0, N/4р"1, где h - шаг, равный 4р,, р.< М/4.

Если же р.) М/4, то l принимает одно из следующих значений: О, М/4, М/2;

N/2-М/4 и в этих строках единственный ненулевой элемент, равный 1, располо- з жен соответственно в столбцах с номерами 0 N/2 N-1; М/2.

Для пояснения работы устройства расрассмотрим пример для М 16, Необходимо отметить, что нижняя половина матрицы ф неинформативна,.так ка кЗ1, (j ) =5 (М- J ), ) l, М/2-1, поэтому для получения спектра мощности Фурье достаточно умножить век" тор Их на верхнк половину- матрицы 40 ф размерностью (М/2+1)М.

Для М 16 коэффициенты Ь,.- принимают следующие значения Ь1 2= Ь,(4 = ЪУ 14= Ь1 2=1/4+К2(4+

45 1(2 2 1/2 -22(4 +1(2 21/2+ Й(4;

Ъ,1 =Ъ =Ь =Ь =1/4-Я(4-3/2 6/2 -3(2(4 + 1/2 1Ч(2+32/4;

$6

Ь„„-Ь„- „-Ь,, =Ц4-Н((.

+3(2 1/02-22/4 -1/2 Б/2 2/4 i

Ъ114=Ь12 2 2 1314=1/4+Я/4"1(23/1(2-1/2/4-1/2 1/2+22/4;

Ь2 S = ЬЬЕ =Ъ,ЦЬ rZ--Ъ,14 4 « И+1/21 2 2

0 000 О

1/2+ 2/2 О 0 О 1/2-g/2

0 О1О З

1/2-Г2/2 О 0 0 1/2+ 2/2

0 000 О

1/2-М2/2 О О О 1/2+Й/2

0 010 0

1/2+1(2/2 О 0 0 1/2-1 2/2

З,Ю 5,Е И26 13, 0

-1/2 21/2-22/4-3/23/1/Е+Г2 Я l

, Р =", =,2 = И.= (4 (-1 231(2 72I4+ 1(Z (/112+12l4, Ъ = Ь

О,О 48 Ú845 SИЕ МИЬ

Работа устройства происходит следующим образом.

Предварительно в первый блок 1 памяти заносятся в естественном порядке значения ординат спектра Уолша

l4x(j), а во второй блок 2 памятизначенйя коэффициентов Ь1 ° последовательно по строкам матрицы Ф, т.е. в нулевую ячейку Ь о, в первую Ь1 3 во вторую b и т.д. С выхода двоичного счетчика 5 циклов подаются на вход второго умножителя только два младших разряда, в результате чего в зависимости от значения кода в них в умножителе 4 происходит умножение на 0,2 или g,4. Если значение кода

00, происходит умножение на О, если

10 или ll, происходит умножение на

2,- если Ol, на 4. Такой умножитель реализуется на регистре сдвига.

При поступлении первых N-1 тактовых импульсов на вход двоичного счетчика 3 во втором умножителе 4 происходит умножение на О, так как в счетчике 5 циклов все нули, в результате чего происходит выборка из первого блока 1 памяти значения спектра W„(0) и иэ второго блока 2 памяти коэффициента ОО, которые, перемножаются в умножителе 7 и далее поступают в сумматор, в результате чего на его выходе имеем значение, равное произведению векторстолбца Я„ на нулевую строку матрицы ф. С этого момента начинается следующий цикл вычисления. По приходу на вход счетчика 3 М-го импульса, последний вырабатывает импульс переполнения, который устанавливает блоки 7 и 8 .в исходное состояние

Составитель А.Баранов

Редактор А,Шишкина Техред 0.Неце Корректор Г.Решетник

Заказ 3019/59 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д, 4/5

Филиал ППП "Патент", г, Ужгород, ул, Проектная, 4

5 101 и записывает 8 счетчик циклов 1 в результате чего при поступлении следующих импульсов на вход счетчика 3, на выходе умножителя 4 присутствуют коды чисел после N-1-го1 2=2; N-3-го - 5.2=10 N-7-го

7 2=14, При поступлении М-9-го 9 2 >i 16 срабатывает блок 6 сравнения, который сбрасывает в исходное состояние блоки 3, 4, 7 и 8 и записывает в счетчике 5 циклов 1, При этом происходит умножение только на нечетные числа, так как младший разряд счетчика соединен с разрешающим входом умножителя 4 и дает разрешение только на умножения на нечетные числа. Таким образом, в результате выдачи умножи3972 6 тел м 4 адресов 2, 6, 1О, 14, происходит соответственно выборка ординат спектра L4„(2); W„(6); Wx(10);

U„(14) и коэффициентов Ь1, Ь,, в.т 4и последоваTe ьHoe to ние и суммирование их в блоках 7 и

8. Таким образом, происходит перемножение M„(j) на первую строку матрицы Ф, На этом заканчивается цикл вычисления, Аналогично проходят последующие циклы вычислений.

Данное устройство для спектрального анализа обладает большим быстродействием и простотой конструкции эа счет значительного сокращения количества арифметических операций,