Преобразователь кода

Иллюстрации

Показать всеРеферат

ПРЕОБРАЗОВАТЕЛЬ КОДА, содержащий сумматор-.вычитатель,, триггер , первый и второй управляемЕ е инверторы, управляющие входы котоРЫЗ{ подключены к вырсоду триггера, первый вход которого подключен к шине тактовых импульсрв, а второй к выходу старшего разряда сумматоравычитателя , поразрядные выходы которого подключены к поразрядным входам первого управляемого инвертора, а первые поразрядные входы подключены к поразрядным выходам второго управляемого инвертора и выходам iустройства, а вторые пс азрядные входы - к входам устройства, отличающийся тем, что, с , целью повышения быстродействия, в него введены регистр, элемент за- : держки, дополнительный сумматор-вычитатель и постоянное запоминающее устройство, входы которого подключены к выходам первого управляемого инвертора и вторым входам дополнительного сумматора-вычит.ателя, первые входы которого подключены к выходам постоянного запоминающего устройства, управлякяций первого управляемого инвертора подключен к управляющему входу дополнительного сумматора-вычитателя и к входу старшего разряда регистра, остальные поразрядные входы которого подключены к выходам дополнительного сумматоравычитателяу а стробйрующий вход через элемент задержки - к шине так- 2 товЦх импульсов, выход старшего разряда регистра соединен с входом старшего разряда сумматора-шачитателя , остальные выходы регистра с входами второго управляемого инвертора.

СОЮЗ СОВ :ГСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

3Ш Н ЗК1 24

ГОСУДАРСТВЕННЫЙ. КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ. (21) 3372086/18-21 (22) 29. 12. 81 (46) 23.04. 83. Бюл. Р 15 (72) В.И. Горбачев (7Т) Ленинградский электротехнический. институт связи им. проф., М.A. Бонч-Бруевича (53) 621.382(088 ° 8) (56) 1. Букреев И.Н., Мансуров Б.М. и Горячев В.И; Микроэлектронные схемы цифровых устройств. М., "Советское радио", 1975, с. 339-341.

2. Авторское свидетельство СССР по заявке В 3231939, кл. Н 03 К 19/24>

21.07.81 (прототип). (54)(57) ПРЕОБРАЗОВАТЕЛЬ КОДА, содержащий сумматор-:вычитатель„ триггер, первый и второй управляемые инверторы, управляющие входы которы» подключены к выходу триггера, первый вход которого подключен к шине тактовых импульсов, а второй— к выходу старшего разряда сумматоравычитателя, поразрядные выходы которого подключены к поразрядным входам первого управляемого инвертора, а первые поразрядные входы подключены к поразрядным выходам второго,.Я0.„ 1014144 A управляемого инвертора и выходам устройства, а вторые поразрядные входы - к входам устройства, о тл и ч а ю шийся тем, что, сцелью повышения быстродействия, в него введены регистр, элемент задержки, дополнительный сумматор-вычитатель и постоянное запоминающее устройство, входы которого подключе-. ны к выходам первого управляемого инвертора и вторым входам дополнительного сумматора-вычитателя, первые входы которого подключены к выходам постоянного запоминающего устройства, управляющий вход первого управляемого инвертора подключен к управляющему входу дополнительного сумматора-вычнтателя и к входу старшего разряда регистра, остальные поразрядные входи которого подключены к выходам дополнительного сумма- С тора-вычитателя, а стробирующий вход через элемент задержки — к шине так товцх импульсов, выход старшего разряда регистра соединен с входом старшего разряда сумматора-внчита- lieaL теля, остальные выходы регистра— с входами второго управляемого инвертора. О 4

«Ф»

4 в

1014144

Изобретение относится к импульсной технике, может быть использованс в устройствах кодирования, передачи данных и технике связи. В частности, устройство может быть использовано в системах цифровой компрессии стандартного телевизионного видеосигнала методами адаптивной дельта-модуляции (АДМ) и дифференциальной импульсно-кодовой модуляции (gHKM).

Известны .устройства, содержащие 10 сумматор-вычитатель и регистр, поразрядные входы которого подключены к поразрядным выходам сумматора-вычитателя, а его первые и вторые входы соединены соответственно с 15 входом устройства и выходом регистра 1).

В данных устройствах на регистре с помощью сумматора-вычитателя накапливается последовательность положительных и отрицательных кодовых приращений. Однако эти устройства не обеспечивают экспоненциального преобразования накапливаемой суммы, что приводит к ухудшению помехоустойчивости при использовании устройства в качестве петли обратной связи в системах передачи с адаптивной дельта-модуляцией и дифференциальной .импульсно-кодовой модуляцией.

Известен преобразователь кода, обеспечивающий экспоненциальное пре-образование накапливаемой последовательности различных по знаку и амплитуде параллельных кодовых приращений, причем экспоненциальный

:спад стремится к среднему значению

Бср 12J.

Однако .быстродействия устройства недостаточно для работы в системах

-цифровой компрессии стандартного 4О телевизионного видеосигнала.

Целью изобретения является повышение быстродействия преобразования кода за счет сокращения времени 45 экспоненциаль ной обработки накаплию ваемой суммы параллельных кодовых приращений.

Указанная цель достигается тем, что в преобразователь кода, содержащий сумматор-вычитатель, триггер, первый и второй управляемые инверторы, управляющие входы которых подключены к выходу триггера, первый вход которого подключен к шине тактовых импульсов, а второй - к выходу старшего разряда сумматора-вычитателя, поразрядные выходы которого подключены к поразрядным входам первого управляемого инвертора, а первые поразрядные входы подключены 60 к поразрядным выходам второго управляемого инвертора и выходам устройства, а вторые поразрядные входык входам устройства, введены регистр элемент задержки, дополнительный 65 сумматор-вычитатель и постоянное запоминающее устройство, входы которого подключены к выходам первого управляемого инвертора и вторым входам дополнительного сумматора-вычитателя, первые входы которого подключены к выходам постоянного запоминающего устройства, управляющий вход первого управляемого инвертора подключен к управляющему входу до-. полнительного сумматора-вычитателя и к входу старшего разряда регистра, остальные поразрядные входы которого подключены к выходам дополнительного сумматора-вычитателя,а стробирующий вход через элемент задержки — к шине тактовых импульсов, выход старше-. го разряда регистра соединен с входом старшего разряда сумматора-вычитателя, остальные выходы регистра с входами второго управляемого инвертора.

Существенное повышение быстродействия устройства образуется за счет сокращения времени экспоненциальной обработки накапливаемой суммы поступающих кодовых приращений. В известном преобразователе для экспоненциальной обработки требуются сотни импульсов высокой частоты f>, поступающих на суммирующий и вычитающий счетчики до момента совпадения их выходных кодов (окончание цикла обработки). В предлагаемом устройстве нет необходимости в высокой частоте поскольку введение указанных новых элементов и их определенная взаимосвязь позволяет производить обработку за один такт. Укаэанное в известном устройстве ограничение . частоты поступления кодовых приращений f«fX устранено. Поэтому частота поступления кодовых приращений

fz может быть значительно повышена и она определяется лишь задержкой в элементах схемы, для компенсации которой в устройство введен элемент задержки.

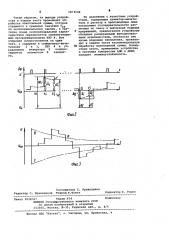

На фиг. 1 представлена структурная схема преобразователя кода; на фиг. 2 и 3 — временные диаграммы его работы.

Преобразователь кода содержит сумматор-вычитатель 1, выходы младших разрядов которого подключены к входам управляемого инвертора 2, а выхопы последнего соединены с вторыми входами дополнительного сумматоравычитателя 3 и входами постоянного запоминающего устройства (ПЗУ) 4, а его выходы подключены к первым входам сумматора-вычитателя 3, управляющий вход которого соединен с входом старшего разряда регистра 5, управляющими входами управляемых инверторов

2 и б и выходом триггера 7, информационный вход которого подключен

1014144 к выходу старшего разряда сумматоранычнтателя 1-, а первые и вторые входы сумматора-вычитателя подключены соответственно к входу устройства и ныходу управляемого иннертора б, а входы последнего подсоединены к 5 выходам регистра 5, поразрядные и стробирующий входы которого соединены соответственно с выходами дополнителв. ного сумматора-вычитателя 3 и через элемент 8 задержки - с стробирующим 10 входом триггера 7, на который подан сигнал тактовой частоты.

Устройство работает следующим образом.

На первые входы сумматора-вычиталеля 1 поступают параллельные кодовые приращения с частотой 1 . Сумматор-нычитатель предстанляет собой обычный сумматор с комбинационной логической схемой для выполнения

20 операции сложения или вычитания. В каждом такте в зависимости от знака кодового приращения, т.е. "1" или

"0" в знаковом разряде, происходит суммирование или нычитание его из остатка суммы, подающегося на вторые входы сумматора-вычитателя 1 с выхода устройства. После суммирования осуществляется экспоненциаль:ная обработка с помощью постоянного запоминающего устройства (ПЗУ) 4, в котором записана экспоненциальная характеристика с заданной крутизной, дополнительного сумматора-нычитателя

3, элемента 8 задержки регистра 5.

На выходе устройства образуется новый остаток суммы, обработанный по экспоненциальному закону, причем ,экспоненциальный спад стремится к некоторому среднему значению Ц .

В момент времени ti (фиг. 2) кодовое 40 приращение 1_#_1 суммируется с ранее образованным остатком накопленных приращений. Если новая сумма превышает средний уровень Оср, то нысокий noTeHcHa Ha выходе старшего 45 разряда сумматора-вычитателя 1 ,фиксируется триггером 7 и выключает управляемые инверторы 2 и б, и выходы младших разрядов в прямом коде поступают на ПЗУ 4, Триггер 7 и управляемый инвертор 2 подают на ПЗУ

4 абсолютную величину разности где Ui - кодовое значение необработанной суммы в момент времени +i;

U — кодовое значение среднего уровня. указанная величина. поступает на 40 первые входы дополнительного сумматора-вычитателя 3, а на его вторые входы из ПЗУ 4, в соответствии с входным кодом ф, поступает код раз ности ;, зависящий от крутизны 65 спада экспоненциальной кривой и представляющий собой величину, на которую необходимо уменьшить в соответствии с записанным н ПЗУ 4 экспоненциальным ..законом обработки.

В соответствии с высоким потенциалом на выходе триггера 7 дополнительный сумматор-вычитатель 3 производит операцию вычитания Jdg †„ = )д ) (интервал времени Π— ti на фиг.2).

Задержанный во время включения вышеуказанных элементов устройства с помощью элемента 8 задержки. импульс тактовой частоты f вписывает в регистр 5 код )(P(и высокий потенциал триггера 7 (старший разряд кода обработанной суммы) . В соответствии с управляющим сигналом триггера 7 инвертор б пропускает обработанный код младших разрядов суммы на выход устройства B неинвертиронанном виде, а старший разряд снимается непосредственно с соответствующего выхода регистра 5, т,е. на выходе устройства формируется обработанное кодовое значение суммы Ui. Если в момент

° 1 времени . отрицательное приращение Ц приведет к тому, что на выходе сумматора-нычитателя 1 новая сумма

0 станет меньше среднего уровня то низкий потенциал старшего разряда сумматора-вычитателя 1 зафиксируется триггером 7 и включит управляемые инверторы 2 и б.- Вследствие этого на ПЗУ 4 и первые входы дополнительного сумматора-вычитателя

3 подается инвертированный код младших разрядов необработанной . суммы, что соответствует абсолютное величине разности Idj I = lu> — V е

В соответствии с поданным на вход

Пну 4 кодом )P> (, на его выходе образуется код Я, необходимый для получения обработанной по экспоненциальному закону величины Id I . Дополнительный сумматор-вычитатель 3 производит операцию сложения )Д . +

+ Е. = l jI так как на его управляю-.

I щий вход подан низкий потенциал с триггера 7. Далее указанная величина и низкий потенциал триггера 7 вписываются в регистр 5 и, пройдя вклю ченный управляемый инвертор б, на„ выходе устройства в момент времени образуется обработанное значение

c ììû U> (фиг. 2) .

На фиг. 3 показаны примеры функ" ционирования устройства. Кривая Q отображает пример работы при поступлении на вход устройства последовательности различных положительных и отрицательных кодовых приращений.

Кривые В и С показывают экспоненциальный характер изменения амплитуды за несколько тактов в случае подачи единовременных положительного и отрицательного приращений, соответст» венно.

1014144

° ° ° ° и«

° Ф ° ° °

Составитель С. Кривуценко

Редактор О. Юрковецкая Техред Т.Фанта

Корректор Е. Рошко

Заказ 3038/67 Тираж 934

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Таким образом, на выходе устройства в каждом такте происходит обработка накопленной сумМы, которая стремится к среднему значению U по экспоненциальному закону, а крутизна спада экспоненциальной характеристики определяется соответствующим программированием ПЗУ 4. Все операции осуществляются за один такт, а задержки в сумматорах-вычитателях 1 и 3, ПЗУ 4 и управляемом инверторе 2 компен снруются элементом 8 задерж ки.

По сравнению с известным устройством, содержащим сумматор-вычитатель и регистр и производящим лишь накопление последовательности pasличных по знаку и амплитуде кодовых

5 приращений, предлагаемое устройство обладает расширенными функциональными возможностями, поскольку оно кроме операции накопления, производит в каждом такте экспоненциальную

t0 обработку накопленной суммы. Вследствие этого, применение устройства в системах компрессии АДМ и ДИКМ повысит. помехоустойчивость.