Усилитель считывания

Иллюстрации

Показать всеРеферат

УСИЛИТЕЛЬ СЧИТЫВАНИЯ, содер жащий первый и второй ключевые транзисторы , включенные по триггерной схеме, ИСТО5КИ которых соединены со стоком первого управляющего транзистора , .исток первого управляющего транзистора соединен с шиной нулевог потенциала, затвор первого управляющего транзистора соединен с первой шиной управления, первый и второй ;транзисторы предварительного заряда стоки которых соединены-с шиной пита ния , стоки ключевьлх транзисторо являются выходами усилителя считывания , затворы транзисторов предварит тельного заряда соединены со второй иданой управления, и третью шину управления , о т л и ч а ю щи и с я тем, что, с целью повьоаения быстродействия и расширения области qro применения путем увеличения выходного нгшряжения, превышаемого напряж ние источника питанияj в него введены первый, второй, третий и четвертый коммутирующие траиэйстоЕИ, второй управляющий транзистор, первый и транзисторы разряда, накрпн тельные элементы на первом и втором конденсаторах, первый и второй разделительные транзистс а стоки которых соединены соответственно с истоками транзисторов предварительного заряда, первые обкладки койдексаторов соединены с затворами первого и второго коммутирующих транзисторов и первой шиной управления, вторые обкладки конденсаторов соединены соответственно со стоками первого и второго коммутирукюих транзисторов, истоки которых соединены соответственно с истоками третьего и четвертого коммутирующих транзисторов и являются nepBbiM и вторш, усилителя счиилаания CTOICH разделительных транзисторов соединены COOT-I ветственно с истоками третьего и четвертого коммутирующих транзисто ров затворы кото1зых соединены со второй шиной управления, затвор и исток первого разделителзьного транзистора соединены со стоком nepBojro ключевого транзистора, .затвор и исток второго разделительного транзистора соединены со стоком второго ключевого транзистора , истоки транзисторов разряда соединены со стоком второго управляющего транзистора, исток соединен с шиной нулевого потейциаЛа , затвор второго улравляквдегв транёистора соединен с третьей шиной управления , затворы .ключевых транзисторов соединены соответственно с затво рами транзисторов разряда. Стоки. которых соединены соответственно с истоками первого и второго коммутирующих транзисторов.

COOS СОВЕТСНИХ

РЕСПУБЛИН д) (311 С 7/00

ОПИСАНИЕ ИЗСБРЕТЕНИ

К АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ, ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3367041/18-24 (22) 23.12.81 (46) 30.04.83. Бюл. Р 16. .(72) В.Д.Рещанов (53) 681«327.66(088 .8) .(56) l ° Патент C2IA 9 4003035, кл. Gll С 7/00, 1978.

2. Патент CQIA Р 4125878

;кл.. Gll С 7/00, 1979 (прототип)..(54) (57) уСил1(11ь CmHTHWHHa, содержащий первый и второй ключевые тран-, зисторы, включенные по триггерной : схеме, истоки которых соединены со стоком первого управлякицего транзистора, исток первого управляющего транзистора соединен с шиной нулевого потенциала, затвор первого управляющего транзистора соединен с первой шиной управления, первый и второй транзисторы предварительного заряда, стоки которых соединены-с шиной питания, стоки ключевых транзисторов"яв- . ляются выходами усилителя считыва« . ния, затворы транзисторов предварительного заряда соединены со второй . шиной управления, и третью шину управления, отличающийся тем, что, с целью повышения быстро-.действия и расширения области его применения путем увеличения выходного напряжения, превышаемого напряжение.источника пйтания; в него введены первый, второй, третйй и четвертый коммутирукщие транзисторы, второй управляющий транзистор, первый . .и второй транзисторы разряда, накопи"-:тельные элементы на первом и втором.„SU 1015435 A конденсаторах, первый и второй разделительные транзисторы стоки которых соединены соответственно с истоками транзисторов предварительного заряда, первые обкладки конденсаторов соединены о затворами первого и второго коммутирующих транзисторов и первой шиной управления, вторые обкладки конденсаторов ссединены соответственно со стоками первого и второго коммутирущщих транзисторов, истоки которых соединены соответственно с истоками третьего и четвер" того коммутирующих транзисторов н являются первым и. .вторим;:входами: уси.лителя считывания стоки разделительных транзисторов соединены соот- Е ветственно с истоками третьего и четвертого коммутирующих транзисторов за воры которых соединены со второй шиной управления, затвор и исток первого разделительного транзистора соединены со стоком первого ключевого ф транзистора, затвор и исток второго раэделительнЬго транзистора соединены со стоком .второго ключевого транзистора,истоки транзисторов разряда соединены со стоком второго управлякщего транзистора, исток которого соединен с шиной. нулевого потейциаЛа, затвор второго управляющегб тран зистора соединен с третьей шиной управления, затворы .ключевых трайэисто ров соединены соответственно с ватно рами транзисторов разряда, стоки которых соединены соответственно с йстоками nepaoro и второго коммутирр ющих транзисторов.

1015435

Изобретение относится к вычислительной технике, в частности к технике полупроводниковых запоминающих устройств (Зу) и может быть использовано в качестве усилия считывания при выполнении накопителя полупроводникового ЗУ на однотранэисторных

ИДП-элементах памяти.

Известен усилитель, построенный на. основе триггера к плечам котороУ

10 го подключены транзисторы предзаряда, к одному из Плеч подключена шина вывода информации, а к другому — . источник опорного напряжения 5 1). второго, управляющего транзистора, исток которого соединен с шиной нулевого потенциала, затвор второго управляющего транзистора соединен с третьей шиной управления, затворы ветственно с затворами транзисторов разряда, стоки которых соединены соответственно с истоками первого и второго коммутирующих .транзисторов.

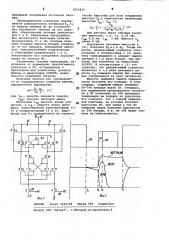

На фиг.1 изображена электрическая схема предлагаемого усилителя считыванияу на фиг.2 †. временные диаграм мы, поясняющие его работу.

Предлагаемый усилитель содержит ключевые транзисторы 1 и 2, управляюНедостатками данного усилителя являются невысокая чувствительность иэ-за использования источника опор.ного напряжения, а также малое быстродействие.

Наиболее близок к предлагаемому по технической сущности усилитель считывания, построенный на основе триггера,.образованного двумя транзисторами, соединенными перекрестными связями, истоки которых соединены со стоком включающего транзистора, исток включающего транзистора соединен с общей шиной, а его затвор образует управляющий вход усилителя, плечи триггера образуют входы -выходы усилителя. К плечам трйггера подключены транзисторы предзаряда и шины вывода информации. При работе усилителя считанный из опрашиваемого элемента памяти информационный сигнал поступает на один иэ дифференциаль- 35 ных усилителей, расположенных в накопителе, и усиливается им, после чего через ключи, управляемые с дешифратора, в виде дифференциального сигнала передается на шины вывода 40 информации, с которых поступает на усилитель, усиливается и устанавливается на его выходах. Одновременно с этим .усиленный сигнал снова запи. сывается в элемент памяти, из кото- 45 рого он был снитан. Увеличение ам:плитуды записываемого в элемент памяти сигнала обеспечивает большую величину считываемого из него сигнала при последующем обращении и позволяет уменьшить размеры элемента памяти (2). Недостатком известного усилителя является невысокое быстродействие, так как оно определяется задержкой между его включением и установлением усиленного сигнала на его выводах, а непосредственно к выходам усилителя подключены имеющие большую емкость шины вывода информации.

Цель изобретения — увеличение . 60 быстродействия усилителя считывания и расширение области его применения путем увеличения амплитуды выходного напряжения, превышающего напряжение источника питания. 65 поставленная цель достигается тем, что в усилитель считывания, содержащий первый и второй ключевые транзисторы, включенные по триггерной схеме, истоки которых соединены со стоком первого управляющего транзистора, исток первого управляющего транзистора соединен с шиной нулевого потенциала, затвор первого управляющего транзистора соединен с первой шиной управления, первый и второй транзисторы предварительного заряда, стоки которых соединены с шиной питания, стоки ключевых транзисторов являются выходами усилителя считывания, затворы транзисторов предварительного заряда соединены со второй шиной управления, и третью шину управления, введены первый, второй, третий и четвертый коммутирующие транзисторы, второй управляющий транзистор, первый и второй .транзисторы разряда, накопительные элементы на первом и втором конденсаторах, первый и второй разделительные транзисторы, стоки которых соединены соответственно с истоками транзисторов предварительного заряда, первые обкладки конденсаторов соединены с затворами первого и второго коммутирующих транзисторов и первой шиной управления, вторые обкладки конденсаторов соединены соответственно со стоками первого и второго коммутирующих транзисторов, истоки которых соединены соответственно с истоками третьего и четвертого коммутирующих транзисторов и являются первым и вторым входами усилителя считывания, стоки разделительных транзисторов соединены соответственно с истоками третьего и четвертого коммутирующих транзисторов, затворы которых соединены со второй шиной управления, затвор и исток первого разделительного транзистора соединены со стоком первого ключевого транзистора, затвор и исток второго разделительного тран- зистора соединены со стоком второго ключевого транзистора, истоки транзисторов разряда соединены ео стоком ключевых транзисторов соединены соот1015435 щие транзисторы 3 и 4, шину 5 пита.ния, транзисторы,6 и 7 разряда, шину 8 н1 левого потенциала, транзисторы 9 и 10 предварительного заряда, коммутирующие транзисторы 11-14,. накопительные элементы, например, конденсаторы 15 и 16, разделительные транзисторы 17 и 18, а также шины

19-21 управления. чинает разряжаться через открытое плечо дифференциального усилителя (не показан). В результате на входах усилителя возникает и начинает расти дифференциальный информационный сигнал Ь О . Через открытые разделительные транзисторы 17 и 18 сигнал передается на стоки транзисто- . ров 1 и 2, образующих выходы усилите ля, В момент, когда сигнал, b.() достигает величины, при которой он может быть уверенно различен усилителем, подается высокий уровень сигнала включения усилителя Фl на шину

19. Транзистор 3 переходит в открытое состояние и в интервале Ь - Фэ разряжает транзистор 1 или транзистор 2. В результате на одном из выходов усилителя устанавливается низкий уровень напряжения, который задается делителем, образованным транзистором 17 (или 18) и транзистором 1 (или 2}, а на втором выходе усилителя сохрайяется высокий уровень напряжения. Одновременно с этим вследствие заряда обкладок конденсаторов 15 и 16 на их вторых обкладках возникает избыточный заряд, который через открывшиеся коммутирующие транзисторы 11 и 12,передается на. входы усилителя, устанавливая уровни напряжения на них выше уровня источника питания. В момент времени

+ подается высокий уровень сигнала

Ф2 на шину 20 и через открывшийся транзистор 4 и один из транзисторов

6(7), затвор которого подключен к выходу усилителя с высоким потенциалом,производится ускоренный разряд соответствующего входа усилителя.

Поскольку транзистор 3 (или 4) остается в закрытом состоянии, второй вход усилителя остается заряженным до высокого уровня напряжения превосходящего уровень напряжения Ц источника пит ания. Через открытый ключ дешифратора (не показаны) этот уровень напряжения передается на соответствующую числовую шийу! и ";ус танавливается в опрашиваемом элементе памяти. По истечении необходимого времени сигнал включения элемЕнта памяти снимается и высокий уровень напряжения () оказывается записанным в элементе памяти. После этого сни-. маются высокие уровни .сигналов Фl, Ф2 с шин 19 и 20 и подается высокий уровень сигнала ФЗ на шину 21 . Уси-литель переводится в интервал подготовки, по истечении которого он будет готов к новому рабочему интервалу.

Таким образом, предлагаемый уси-. литель позволяет записать в элемент памяти сигнал с амплитудой, превышающей напряжение источника питания

Е . В прототипе величина записываемого в элемент памяти сигнала не

Усилитель функционирует следую- 10 щим образом.

Работу усилителя рассмотрим во взаимодействии с накопителем полупроводникового Зу.

В начале рабочего периода, в интервале .Ьо- происходит подготовка элементов памяти накопителя (не показаны) к подключению усилителя.

Для этого в момент времени Ф подается сигнал включения опрашиваемого элемента памяти, по которому к входам дифференциального усилителя, также расположенного в накопителе, через соответствующие числовые шины подключается опрашиваемый элемент памяти и опорный элемент. В результате на входах дифференциального усилителя устанавливается соответствующий хранимой в элементе памяти информации сигнал Ю=О,-Uq (где 0„ и 0 -. .соответственно потенциалы первой и второй числовых шин). Послупивший на дифференциальный усилитель сигнал усиливается им, в результате числовая шина с меньшим исходным потенциалом (допустим вторая) через .от- З5 крытое плечо дифференциального усилителя оказывается подключенной к шине нулевого потенциала, числовая шина с большим потенциалом (первая) заряжена примерно до напряжения пи- 4О тания.

После этого накопитель готов к подключению усилителя.

До момента времени .Ь в интервале подготовки на соответствующих шинах

19-21 установлены низкие уровни сигналов Фl, Ф2 и высокий уровень сигнала ФЗ. При этом через открытые транзисторы 9 и 10, на затворах которых установлен высокий уровень сиг- 50 нала ФЗ, входы усилителя заряжены до напряжения источника питания. Верхние обкладки конденсаторов 15 и 16 через открытые коммутирующие транзисторы 13-14 соединены с входами усили- теля, и таким образом, также заряже.ны до напряжения источника питания.

В момент времени (; снимается высокий уровень сигнала ФЗ. После этого входы усилителя через ключи, управляемые с дешифратора (не показаны) 60 подключаются к соответствующей опращиваемому элементу памяти паре числовых шин. При этом тот из входов усилителя, который подключается к разряженной числовой шине, также íà- 65

1815435

Фг.7 Ю

ВНИИПИ Заказ 3223/48 Тираж 594 Подпйсное

ФиЛиал ППП "Патент", r.Óæãîðoä,óë.Ïðoåêòíàÿ,4 превышает напряжение источника пита= ния.

Быстродействие усилителя определяется длительностью интервалами -Ьj от подачи сигнала Ф1 до установления усиленного сигнала на его выхо-: дах, образованных стоками транзисторов 1- и 2. Увеличение быстродействия достигается благодаря наличию транзисторов 17 и 18, которые отде-:

Ляют большие емкости входов УСилителя от его выходов. Уменьшение емкостей, непосредственно подключенных.

: .к электродам транзисторов 1 и 2, обеспечивает его ускоренное переключение по сигналу Ф1. 15 !

Увеличение степени интеграции, получаемое от применения. предлагаемого усилителя в ЗУ, по сравнению с прототипом или усилителем, реализо ванным в микросхеме 565РУЗ, можно 2() оценить следующим образом.

Величина сигнала Ь(), считываемо-., го из опрашиваемого элемента памяти, определяется выражением

С„ 0 . 25 . (1, Л сш где С - емкость элемента памяти;

С1, ; емкость числовой шины)

Обозначим СВ емкость входа усн" лит еля, а С ф — емкость блока доз а ряда, образованного транзисторами 1114 и конденсаторами 15 и 16. Выражение для 0л опредеЛяется из первого

Ю закона кирхгофа для узла соединения емкости Cg. и параллельно включенных емкостей С, С Cä

Вм

С,, () = ((+ 1 )

СЪ сэ» сш+

Для расчета берут типовые,значения емкостей, т.е. Си 0,05 пФ;

С О, 8 пФ; С > 3 пФ. Емкость С равна 6 пФ.

Подставляя значение емкостей в (2), получают U, 1 6 Е,„. Таким образом, предлагаемый усилитель обес" печивает в соответствии с (2) величину записываемого в элемент памяти сигнала в 1,6 раза больше, чем прототип или усилитель на микросхеме

565РУЗ. В соответствии с (1) это означает, что предлагаемый усилитель позволяет в 1,6 раза уменьшить емкость С элемента памяти без изменения считываемого иэ него сигналаЬИ .

Емкость элемента памяти занимает около половины его площади. В свою очередь, элементы памяти занимают.

60-70% площади всего ЗУ. Очевидно, ,что применение предложенного усилителя в ЗУ позволяет на 20% уменьшить занимаемую им площадь на кристалле.

Это означает, что с каждой кремниевой пластины, иа которых получают кристаллы ЗУ, при одних и тех же затратах будет получено кристаллов на 20% больше, т.е. на 20% будет снижена их себестоимость.